## Scholars' Mine

**Masters Theses**

Student Theses and Dissertations

Fall 2018

## System level power integrity transient analysis using a physicsbased approach

Jun Xu

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons

#### Department:

#### **Recommended Citation**

Xu, Jun, "System level power integrity transient analysis using a physics-based approach" (2018). Masters Theses. 7842.

https://scholarsmine.mst.edu/masters\_theses/7842

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# SYSTEM LEVEL POWER INTEGRITY TRANSIENT ANALYSIS USING A PHYSICS-BASED APPROACH

by

#### JUN XU

#### A THESIS

Presented to the Faculty of the Graduate School of the MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

MASTER OF SCIENCE

in

**ELECTRICAL ENGINEERING**

2018

Approved by

Jun Fan, Advisor James L. Drewniak Chulsoon Hwang

#### **PUBLICATION THESIS OPTION**

This thesis consists of the following three articles, which have been submitted for publication, or will be submitted for publication as follows:

Paper I: Pages 7-38, "System Level Power Integrity Transient Analysis Using Physics-Based Approach and Optimization with Hybrid Target Impedance," is intended for submission to IEEE Symposium on Electromagnetic Compatibility and Signal/Power Integrity (EMCSIPI) 2019.

Paper II: Pages 42-58, "A Survey on Modeling Strategies for High-Speed Differential Via between Two Parallel Plates," published in 2017 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMCSIPI).

Paper III: Pages 60-72, "Application of Deep Learning for High-speed Differential Via TDR Impedance Fast Prediction," published in 2018 IEEE Symposium on Electromagnetic Compatibility and Signal/Power Integrity (EMCSIPI).

#### **ABSTRACT**

With decreasing supply voltage level and massive demanding current on system chipset, power integrity design becomes more and more critical for system stability. The ultimate goal of well-designed power delivery network (PDN) is to deliver desired voltage level from the source to destination, in other words, to minimize voltage noise delivered to digital devices. The thesis is composed of three parts. The first part focuses on-die level power models including simplified chip power model (CPM) for system level analysis and the worst scenario current profile. The second part of this work introduces the physicsbased equivalent circuit model to simplify the passive PDN model to RLC circuit netlist, to be compatible with any spice simulators and tremendously boost simulation speed. Then a novel system/chip level end-to-end transient model is proposed, including the die model and passive PDN model discussed in previous two chapters as well as a SIMPLIS based small signal VRM model. In the last part of the thesis, how to model voltage regulator module (VRM) is explicitly discussed. Different linear approximated VRM modeling approaches have been compared with the SIMPLIS small signal VRM model in both frequency domain and time domain. The comparison provides PI engineers a guideline to choose specific VRM model under specific circumstances. Finally yet importantly, a PDN optimization example was given. Other than previous PDN optimization approaches, a novel hybrid target impedance concept was proposed in this thesis, in order to improve system level PDN optimization process.

#### **ACKNOWLEDGMENTS**

First, my sincere gratitude and respect go to my advisor, Prof. Jun Fan, for his support and guidance of my master degree study and related research, for his patience, motivation, and immense knowledge. His guidance helped me in all the time of research and finish this thesis. I would like to give my special thanks to Prof. James L. Drewniak for his instruction and support on both my technical and non-technical skills. I would also thank Prof. Chulsoon Hwang for provide his suggestion and hard questions to widen my research from various perspectives.

I would like to thank all my colleagues and friends in the EMC laboratory for their support and cooperation during my master coursework and research. I am very grateful to my parents for their endless love and support throughout these years.

## TABLE OF CONTENTS

| F                                                                               | Page |

|---------------------------------------------------------------------------------|------|

| PUBLICATION THESIS OPTION                                                       | iii  |

| ABSTRACT                                                                        | iv   |

| ACKNOWLEDGMENTS                                                                 | v    |

| LIST OF ILLUSTRATIONS                                                           | ix   |

| LIST OF TABLES                                                                  | xiii |

| SECTION                                                                         |      |

| 1. INTRODUCTION                                                                 | 1    |

| 1.1. BACKGROUND                                                                 | 1    |

| 1.2. MOTIVATION AND CHALLENGE                                                   | 4    |

| 1.3. RESEARCH LITERATURE REVIEW                                                 | 5    |

| PAPER                                                                           |      |

| I. SYSTEM LEVEL POWER INTEGRITY TRANSIENT ANALYSIS USING PHYSICS-BASED APPROACH | 7    |

| ABSTRACT                                                                        | 7    |

| 1. ON-CHIP POWER NETWORK AND LOAD TRANSIENTS                                    | 8    |

| 1.1. ON-CHIP POWER NETWORK MODEL                                                | 8    |

| 1.1.1. Lumped and Reduced Order Power Model                                     | 9    |

| 1.1.2. Simplified Current Load and Pwl Current Profile.                         | 10   |

| 1.2. WORST-CASE LOAD SCENARIO TO PDN IMPEDANCE PEAK                             | 14   |

| 2. PHYSICS-BASED EQUIVALENT CIRCUIT MODEL                                       | 16   |

| 2.1 MODELING BASED ON CURRENT PATH PHYSICS                                      | 16   |

| 2.1.1. Modeling of Printed Circuit Board.                                                       | . 17 |

|-------------------------------------------------------------------------------------------------|------|

| 2.1.2. Modeling of Chip Package.                                                                | . 18 |

| 2.2. END TO END PDN CASCADED EQUIVALENT CIRCUIT MODEL                                           | . 19 |

| 3. SYSTEM LEVEL TRANSIENT ANALYSIS                                                              | . 21 |

| 3.1. TRANSIENT SIMULATION WITH FULL PDN                                                         | . 21 |

| 3.1.1. Spike, Droop and Ripple of Voltage Response on DIE                                       | . 22 |

| 3.1.2. Output Impedance of Voltage Regulator Module (VRM)                                       | . 22 |

| 3.2. VRM MODELS TRADEOFF FOR POWER INTEGRITY ANALYSIS                                           | . 27 |

| 3.2.1. Various VRM Models Extraction and Response                                               | . 27 |

| 3.2.2. Summary on VRM Model Tradeoff                                                            | . 33 |

| 3.3. APPLICATION FOR SYSTEM LEVEL PI OPTIMIZATION                                               | . 34 |

| 3.3.1. Hybrid Target Impedance                                                                  | . 36 |

| 3.3.2. An Example for FD Optimization and TD Validation                                         | . 38 |

| REFERENCES                                                                                      | . 38 |

| II. A SURVEY ON MODELING STRATEGIES FOR HIGH-SPEED DIFFERENTIAL VIA BETWEEN TWO PARALLEL PLATES | 42   |

| ABSTRACT                                                                                        | . 42 |

| 1. INTRODUCTION OF DIFFERENTIAL VIA                                                             | . 42 |

| 2. SURVEY OF MODELING STRATEGIES                                                                | . 45 |

| 2.1. PHYSICS BASED RLC CIRCUIT MODEL                                                            | . 45 |

| 2.2. TRANSMISSION LINE MODEL WITH VIA-PLATE CAPACITANCE                                         | . 46 |

| 2.3. TL MODEL WITH EFFECTIVE DIELECTRIC CONSTANT                                                | . 46 |

| 2.4. PARALLEL PLATES IMPEDANCE ZPP MODEL                                                        | . 47 |

| 3 TWO-LAYERS CASE COMPARISON                                                                    | 50   |

|      | 4. MULTI-LAYERS CASES COMPARISON                                                                | . 52 |

|------|-------------------------------------------------------------------------------------------------|------|

|      | 5. CONCLUSION                                                                                   | . 56 |

|      | REFERENCES                                                                                      | . 58 |

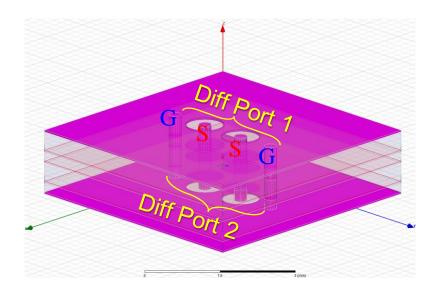

|      | III. APPLICATION OF DEEP LEARNING FOR HIGH-SPEED DIFFERENTIAL VIA TDR IMPEDANCE FAST PREDICTION | . 60 |

|      | ABSTRACT                                                                                        | . 60 |

|      | 1. INTRODUCTION OF VIA IMPEDANCE                                                                | . 60 |

|      | 2. DEEP LEARNING APPROACH                                                                       | . 64 |

|      | 3. MODEL DEVELOPMENT AND VALIDATION                                                             | . 67 |

|      | 4. CONCLUSION                                                                                   | . 71 |

|      | REFERENCES                                                                                      | . 72 |

| SEC' | TION                                                                                            |      |

|      | 2. CONCLUSION                                                                                   | . 73 |

|      | 2.1. SUMMARY OF CONTRIBUTIONS                                                                   | . 73 |

|      | 2.2. FUTURE WORK                                                                                | . 74 |

|      | REFERENCES                                                                                      | . 75 |

| VITA | Α                                                                                               | . 93 |

## LIST OF ILLUSTRATIONS

| SECTION                                                                                                                                           | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.1. Chip-Package-PCB System Full Power Delivery Network (PDN)                                                                             | 1    |

| Figure 1.2. Simplified Circuit Representation of System Full PDN                                                                                  | 3    |

| Figure 1.3. Full PDN Impedance and Current Spectral Component on DIE                                                                              | 3    |

| Figure 1.4. Transient Voltage Response on DIE                                                                                                     | 3    |

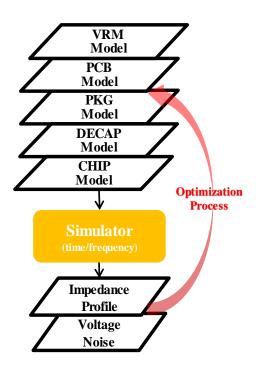

| Figure 1.5. System-level Power Integrity Simulation Flow                                                                                          | 5    |

| PAPER I                                                                                                                                           |      |

| Figure 1. Parasitic Capacitance Circuit Representation of On-Die Transistors                                                                      | 8    |

| Figure 2. Simplified Lumped Equivalent Chip Power Model                                                                                           | 8    |

| Figure 3. Frequency Domain Comparison between Lumped Equivalent Power Model and Multiple Order Power Model                                        |      |

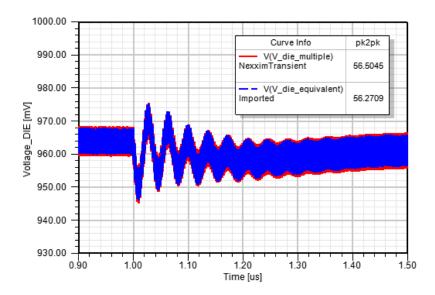

| Figure 4. Time Domain Comparison between Lumped Equivalent Power Model and Multiple Order Power Model                                             | 10   |

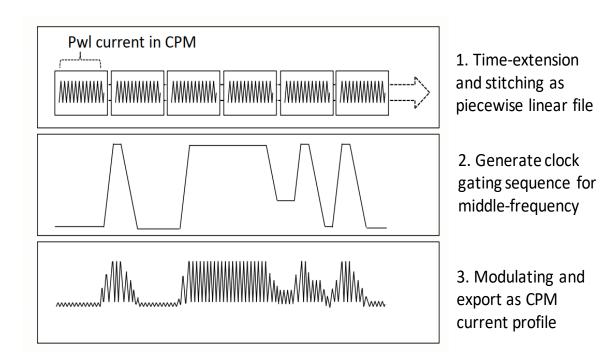

| Figure 5. Current Profile Modulation for Load Transients Modeling                                                                                 | 11   |

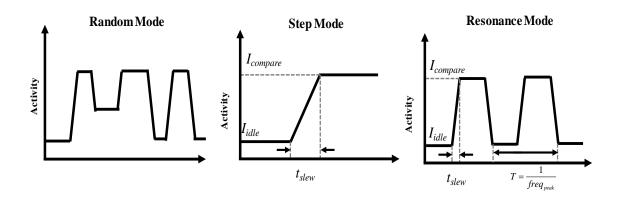

| Figure 6. Typical Operating Mode for Clock Gating Sequence                                                                                        | 11   |

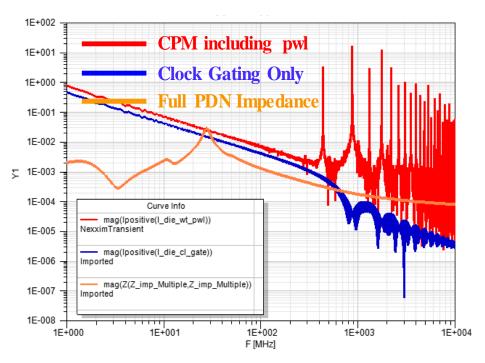

| Figure 7. Frequency Domain between Simplified Current Load and Complete Current Load included pwl current profile with Full PDN Impedance Profile |      |

| Figure 8. Time Domain Comparison between Simplified Current Load and Complete Current Load included pwl current profile                           | 13   |

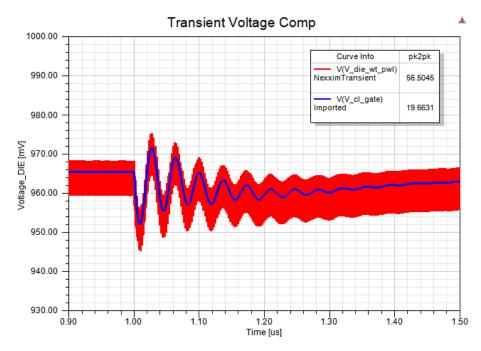

| Figure 9. Time Domain Ripple Comparison between Simplified Current Load and Complete Current Load included pwl current profile                    |      |

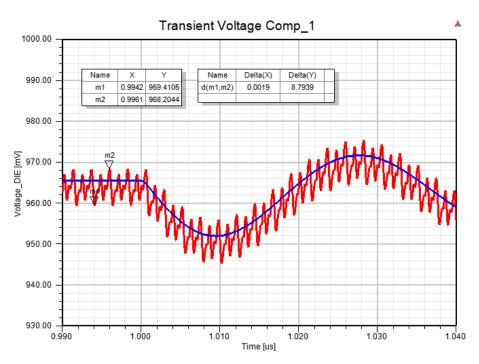

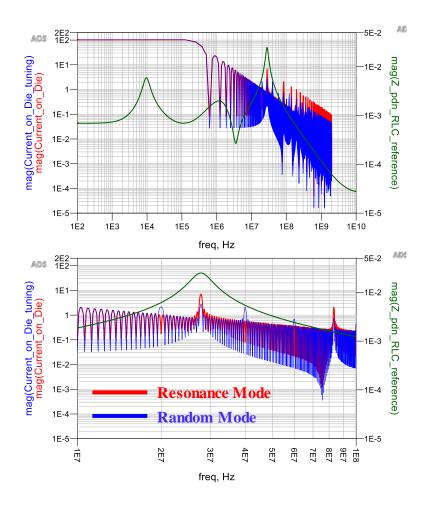

| Figure 10. Frequency Domain - Random Mode Current Profile and Resonance Mode Current Profile with Full PDN Impedance Parallel Resonance Peak      | 14   |

| Figure 11. Time Domain - Random Mode and Resonance Mode Current Profile and Voltage Response Comparison                                           | 15   |

| Figure 12. Geometry Segmentation based on Current Path                                                                                            | 16   |

| Figure 13. PCB Modeling Based on DECAP Placement Locations                                                                             | . 17 |

|----------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 14. Equivalent Circuit Model Extraction for PCB                                                                                 | . 18 |

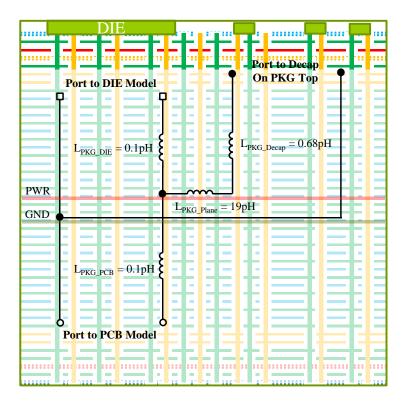

| Figure 15. PKG Modeling Based on DECAP Placement Locations                                                                             | . 18 |

| Figure 16. Equivalent Circuit Model Extraction for PKG                                                                                 | . 19 |

| Figure 17. Cascaded Equivalent Circuit Models from End to End                                                                          | . 20 |

| Figure 18. Correlation between S-parameter Model and Equivalent Circuit Model                                                          | . 20 |

| Figure 19. Two-Phase Synchronous Buck Converter Small Signal VRM Model in SIMPLIS with PDN Equivalent Circuits Models and Load Current | . 21 |

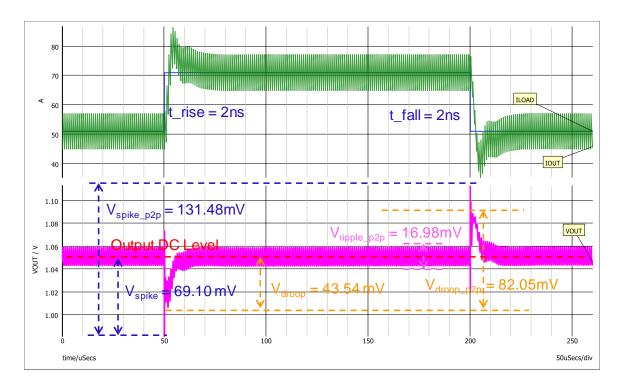

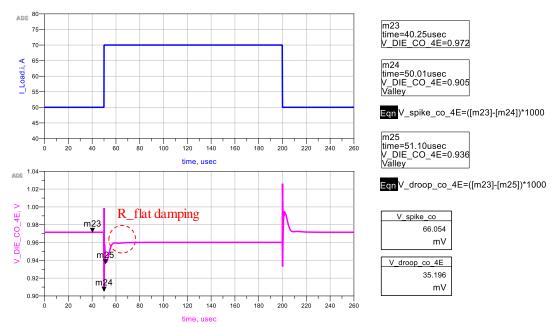

| Figure 20. Identify on Spike, Droop and Ripple of Voltage Response on DIE                                                              | . 23 |

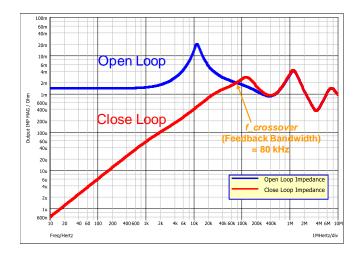

| Figure 21. Comparison between OL and CL Output Impedance                                                                               | . 24 |

| Figure 22. VRM Open loop (OL) Output Impedance                                                                                         | . 25 |

| Figure 23. VRM Closed loop (CL) Output Impedance                                                                                       | . 26 |

| Figure 24. Extracted VRM Output Impedance from SIMPLIS Small Signal Model                                                              | . 27 |

| Figure 25. Voltage Response by VRM Small Signal Model                                                                                  | . 28 |

| Figure 26. Typical Linear VRM Model                                                                                                    | . 29 |

| Figure 27. Correlated Model between Two Element RL Model and SIMPLIS Model                                                             | . 30 |

| Figure 28. Voltage Response by Extracted Two-Element RL Model                                                                          | . 30 |

| Figure 29. Correlated Model between Simple Inductor Model and SIMPLIS Model                                                            | . 31 |

| Figure 30. Voltage Response by Extracted Simple Inductor Model                                                                         | . 31 |

| Figure 31. Three-Element RLL Model .vs. SIMPLIS Model                                                                                  | . 32 |

| Figure 32. Voltage Response by Extracted Three-Element RLL Model                                                                       | . 32 |

| Figure 33. Extremely difficult to meet above target impedance on system level                                                          | . 35 |

| Figure 34. Full PDN Impedance and Current Profile on DIE                                                                               | . 36 |

| Figure 35. Current Profile-based Discrete and Continuous Target Impedance                                                              | . 37 |

| Figure 36. Impedance Optimization based on Hybrid Target Impedance                                                                     | . 38 |

| Figure 37. Voltage Response for PDN-Optimized Case                                                 | 39 |

|----------------------------------------------------------------------------------------------------|----|

| PAPER II                                                                                           |    |

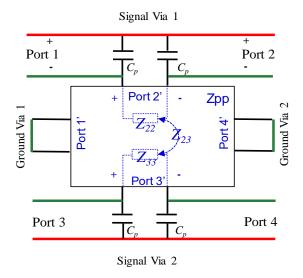

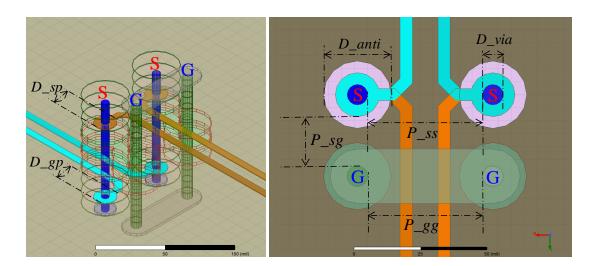

| Figure 1. Geometry of the differential via pairs between planes                                    | 43 |

| Figure 2. Divide-and-conquer method for differential via modeling                                  | 44 |

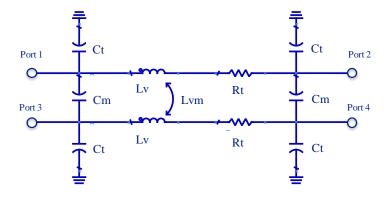

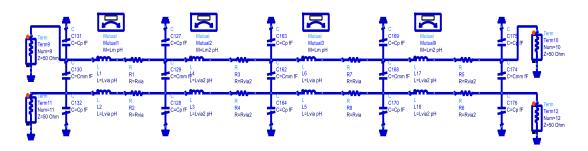

| Figure 3. Model 1 - RLC π-type circuit model                                                       | 45 |

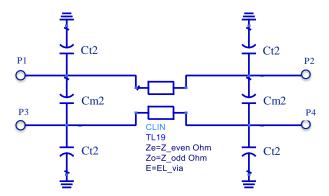

| Figure 4. Model 2 - Transmission line model with via-plate capacitance                             | 46 |

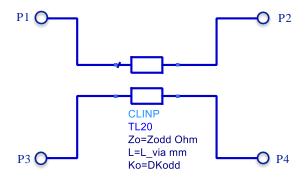

| Figure 5. Model 3 - Transmission line model with effective dielectric constant                     | 47 |

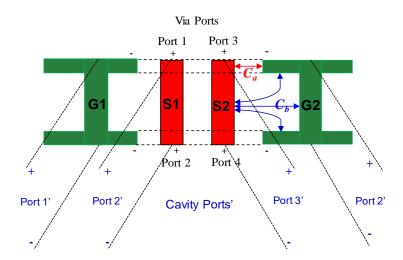

| Figure 6. Illustration of four ports between two parallel plates                                   | 49 |

| Figure 7. Illustration of circuit model - Parallel plates Impedance Zpp model                      | 49 |

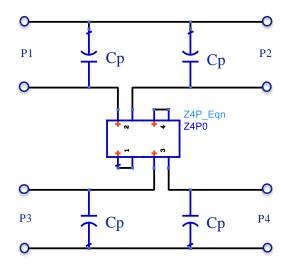

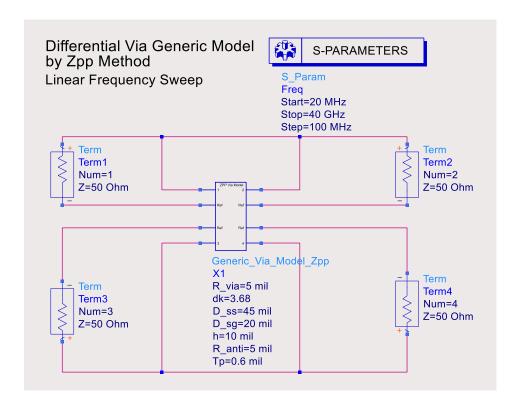

| Figure 8. Circuit model for Model 4 - Parallel plates Impedance Zpp model                          | 50 |

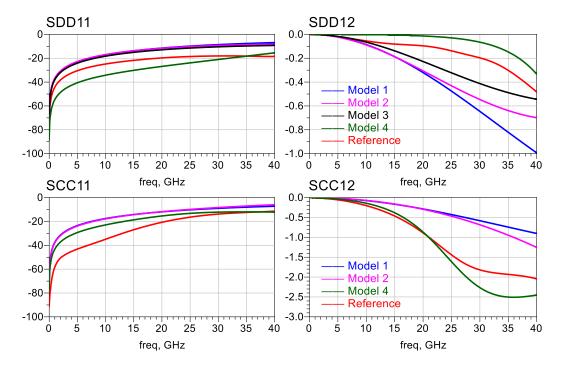

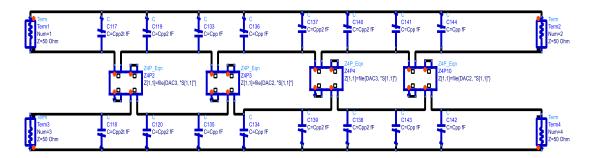

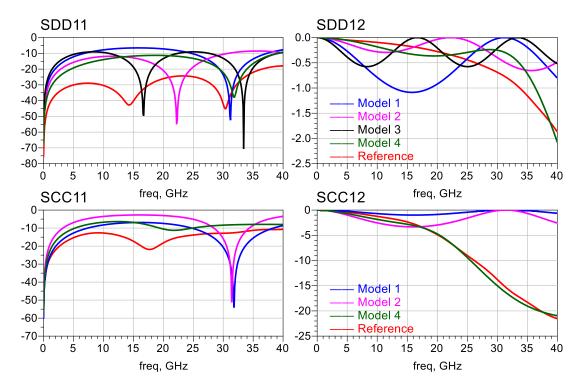

| Figure 9. Mixed mode S-parameter comparison for via with 2-layer plates                            | 51 |

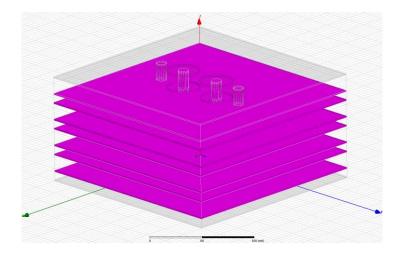

| Figure 10. Full-wave models structure for differential via with 5-layers plates                    | 52 |

| Figure 11. Four-stage π-circuit RLC model for via with 5-layer plates                              | 52 |

| Figure 12. Cascaded Zpp model for via with 5-layer plates                                          | 53 |

| Figure 13. S-parameter Comparison for via with 5-layer plates                                      | 53 |

| Figure 14. Full-wave models structure for differential via with 9-layers plates                    | 54 |

| Figure 15. S-parameter Comparison for via with 9-layer plates                                      | 55 |

| Figure 16. A generic parameterized model using Zpp model for differential via                      | 56 |

| PAPER III                                                                                          |    |

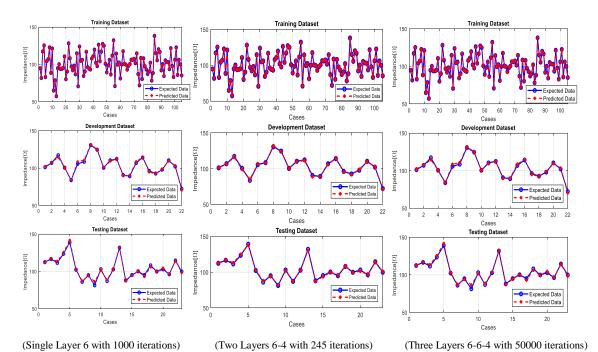

| Figure 1. Geometrical parameters of the differential via in multi-layers PCB                       | 61 |

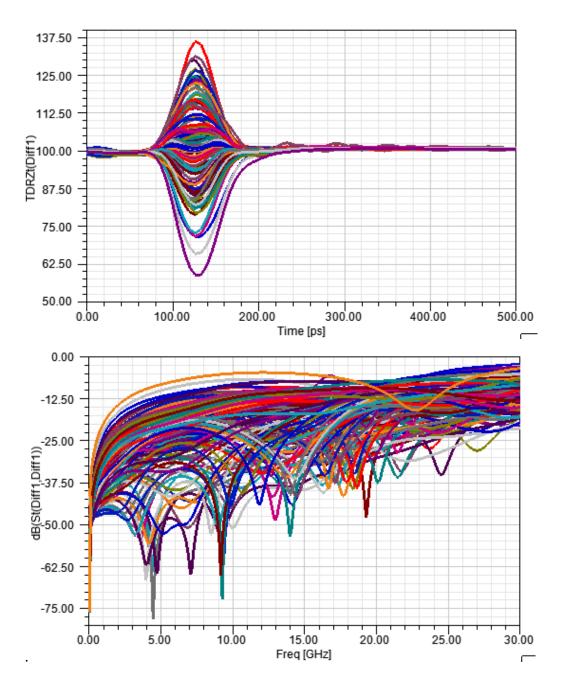

| Figure 2. TDR Impedance and Return Loss Variation with Tuning Design Parameters in the Wide Range  |    |

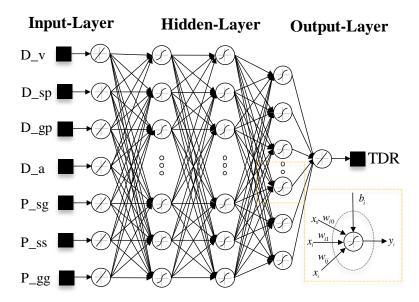

| Figure 3. Structure of DNN model with several hidden layers and quadratic mapping at a neural node | 64 |

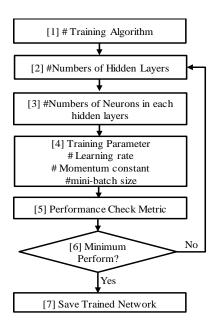

| Figure 4. Flow of DNN model hyperparameter selection                                               | 65 |

| Figure 5. Flow for developing DNN model for designing optimized via                                                                                                                                                    | 68 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

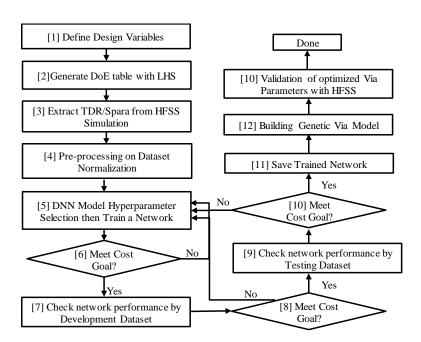

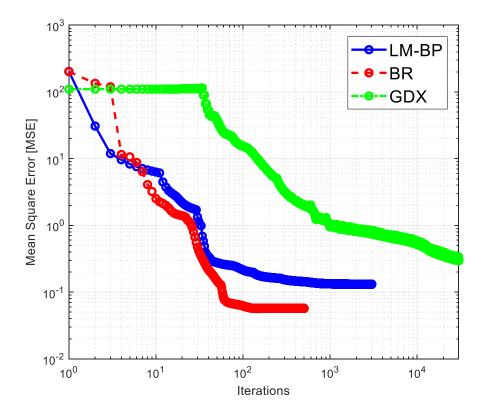

| Figure 6. Training Data (105 sets-70%), Development Data(22 sets-15%) and Testing Data(23 sets-15%) Correlation between expected and predicted data trained with three different training algorithm for neural network | 70 |

| Figure 7. Loss Convergence Comparison between Three Training Algorithm                                                                                                                                                 | 71 |

### LIST OF TABLES

| SECTION                                                                      | Page |

|------------------------------------------------------------------------------|------|

| Table 1.1. 2015 International Technology Roadmap for Semiconductors (ITRS)   | 2    |

| Table 1.2. Common Models Comparison for Each Parts in System PI Analysis     | 5    |

| PAPER I                                                                      |      |

| Table 1. On-chip Low Power Load Operation that Possibly Cause Critical Noise | 12   |

| Table 2. Supply Voltage AC Noise and Design Spec                             | 23   |

| Table 3. Two Element RL Model - Extracted Parameters                         | 30   |

| Table 4. Simple Inductor Model - Extracted Parameters                        | 31   |

| Table 5. Three-Element RLL Model - Extracted Parameters                      | 32   |

| Table 6. Transient Response Comparison between Four Different VRM Models     | 33   |

| Table 7. Tradeoff on VRM model for System Level PI Simulation                | 34   |

| Table 8. Voltage Response Comparison between Previous and Optimized Case     | 39   |

| PAPER II                                                                     |      |

| Table 1. Linear Scale Error for Sdd12 for via with 2-layer plates            | 51   |

| Table 2. Linear Scale Error for Scc12 for via with 2-layer plates            | 51   |

| Table 3. Linear Scale Error for Sdd12 for via with 5-layer plates            | 53   |

| Table 4. Linear Scale Error for Scc12 for via with 5-layer plates            | 54   |

| Table 5. Linear Scale Error for Sdd12 for via with 9-layer plates            | 55   |

| Table 6. Linear Scale Error for Scc12 for via with 9-layer plates            | 55   |

| Table 7. Comparison of Four Models for differential via                      | 57   |

| PAPER III                                                                    |      |

| Table 1. Via Design Tunable Parameters in Layout Stage                       | 61   |

| Table 2. Tabulated Samples of Dataset (150 data points)                                               | 69 |

|-------------------------------------------------------------------------------------------------------|----|

| Table 3. Prediction Cost Metric Value (Ohm) of Performance Evaluation for Differen Training Algorithm |    |

#### **SECTION**

#### 1. INTRODUCTION

#### 1.1. BACKGROUND

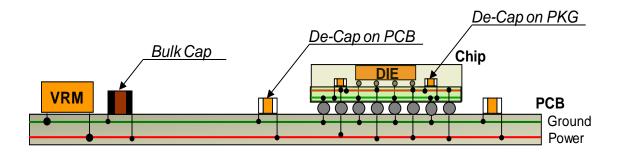

To deliver a reliable power delivery network is a critical design challenge for a Chip-Package-PCB System as shown in figure 1.1. As the chip semiconductor integrated process scale down to nano-scale, the chip supply voltage is also continuously decreasing. From International Technology Roadmap for Semiconductors (ITRS) 2015 report as shown in table 1.1, the supply voltage will move from 0.85V to 0.64V at 2022 [1]. At the same time, the current demand for microprocessor unit (MPU) or central processing unit (CPU) is also growing with higher computational ability and power as the arrival of artificial intelligence era, the development of computer-aided engineering, smartphones, robotics and pilotless automobile.

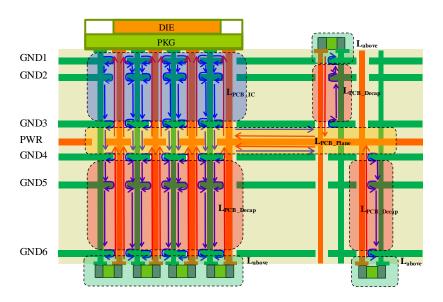

Figure 1.1. Chip-Package-PCB System Full Power Delivery Network (PDN)

The target impedance is a metrics for evaluating the qualification of the power delivery network. From table 1.1, target impedance will potentially decrease to  $0.315 m\Omega$  in future years. That assumed it is calcucated with 2.5% voltage noise tolerance dividing

to 25% current change. This impedance could become less if the chip can only tolerate a smaller voltage noise less than 2.5% or have larger current change than 25%. These would be extremely hard to meet the design target to main a robust system circuit performance.

Table 1.1. 2015 International Technology Roadmap for Semiconductors (ITRS)

| Year            | 2013  | 2014  | 2015  | 2016  | 2017  | 2018  | 2019  | 2020  | 2021  | 2022  |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Voltage<br>(V)  | 0.85  | 0.82  | 0.80  | 0.77  | 0.75  | 0.73  | 0.71  | 0.68  | 0.66  | 0.64  |

| Power (W)       | 149   | 152   | 143   | 130   | 130   | 136   | 133   | 130   | 130   | 130   |

| Current (A)     | 175   | 185   | 179   | 169   | 173   | 186   | 187   | 191   | 197   | 203   |

| Target Imp (mΩ) | 0.486 | 0.443 | 0.447 | 0.456 | 0.434 | 0.392 | 0.380 | 0.356 | 0.335 | 0.315 |

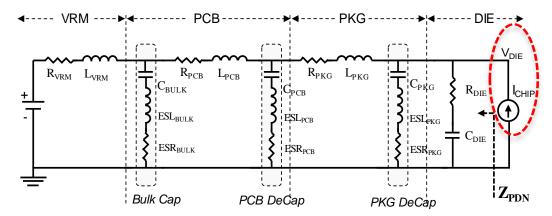

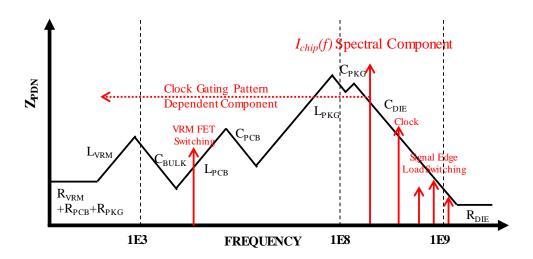

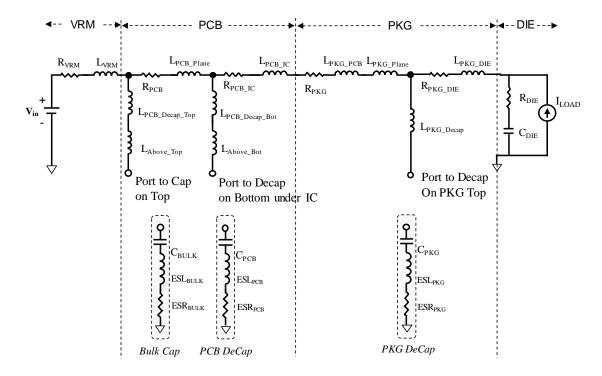

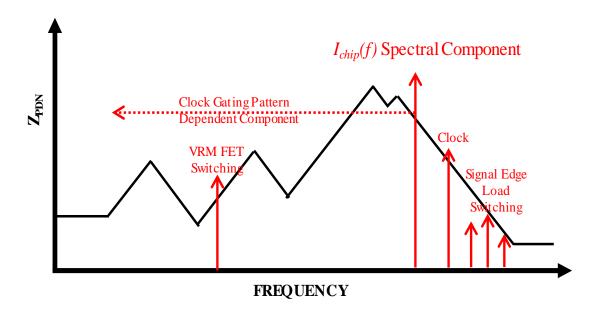

Therefore, it is important to develop a set of methodology to analyze and optimize the PDN then validate the proposed design for the Chip-Package-PCB system full PDN. The system full PDN represented by simplified circuit elements as shown in figure 1.3. The Chip-Package-PCB system includes voltage regulator module (VRM), printed circuit board (PCB), chip package (PKG), chip die and capacitors (CAP). The resistance of these components would cause dc voltage drop, that decreases nominal voltage to a lower voltage and potentially cause a thermal issue of the system.

Figure 1.2. Simplified Circuit Representation of System Full PDN

Figure 1.3. Full PDN Impedance and Current Spectral Component on DIE

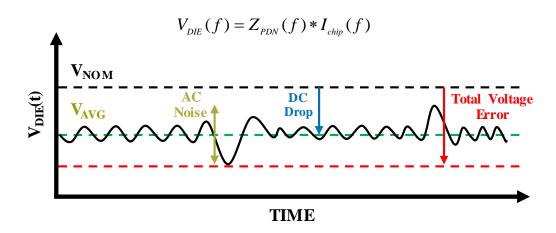

Figure 1.4. Transient Voltage Response on DIE

The PCB and PKG have parasitic inductance, which create anti-resonance with the capacitance in the PDN as shown in the figure 1.3. Especially the resonance peak that cause by package inductance and chip die capacitance would be the highest impedance, which exceed the expected target impedance to make a critical voltage noise to the system chip. From clock gating operation pattern, current spectral components would also vary from a broadband range in middle frequency. These current spectral components multiply with PDN impedance. It would also create an unexpected ac noise droop.

Totally, the DC drop and AC noise of supply voltage will give the total voltage error for the supplied chip. These could cause logic gate error, functional failure, excessive thermal issue and even system chip damage. The well-designed power delivery network from a set of effective methods from system-level is greatly important for maintaining a robust Chip-Package-PCB System.

#### 1.2. MOTIVATION AND CHALLENGE

For system each parts, there are several available models developed for analyzing their behavior and performance as shown in table 1.2. Serval analysis tool and simulators also developed for analyzing each model from different perspectives. The impedance profile could achieve from s-parameter model, spice model, RLC model for frequency domain analysis and optimization to meet the target impedance. The voltage noise could calculate from simulator with these models but the computational time would be very consuming from different tools. How to integrate available models in one compliable simulator for a better approximately accurate simulation, optimization and validation process in a faster way would a critical challenge for system level PI simulation.

|                     | VRM Model                                                                                                          | PCB/PKG Model                                                                                                                       | DECAP Model                                                                                                               | Chip Model                                                                                                                                    |

|---------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Available<br>Models | <ul> <li>Small Signal</li> <li>Model</li> <li>Linear RL</li> <li>Model</li> <li>Behavior</li> <li>Model</li> </ul> | <ul> <li>S-parameters</li> <li>Model</li> <li>Broad-Band</li> <li>Spice Model</li> <li>Equivalent</li> <li>Circuit Model</li> </ul> | <ul> <li>S-parameters</li> <li>Model</li> <li>Spice Netlist</li> <li>Model</li> <li>RLC Circuit</li> <li>Model</li> </ul> | <ul> <li>CPM model</li> <li>Distributed Model</li> <li>Lumped Model</li> <li>Vector-aware</li> <li>VCD</li> <li>Vectorless Profile</li> </ul> |

Table 1.2. Common Models Comparison for Each Parts in System PI Analysis

Figure 1.5. System-level Power Integrity Simulation Flow

#### 1.3. RESEARCH LITERATURE REVIEW

Power integrity analysis to power delivery network design are critical topics in both academic and industrial for many years.

About VRM modeling [2]-[4], [L. Smith et al. 1999] four-element model, and [C. Chung et al. 2001] simplified inductor Model were applied for power integrity analysis.

[K.Yao Phd. 2004], [Y.Qiu Phd. 2005] and [S. Baek et al.2012] provided high-frequency modeling and behavior modeling for buck converters.

About chip power modeling [5]-[13], [J. Zheng et al.2007] presented reduced order CPM model by Norton equivalent circuit with Krylov subspace approximation. [A. Waizman et al. 2004] proposed integrated power supply frequency domain impedance meter (IFDIM) method for system full impedance measurement from the die; [S.Sun ea al.2010] gave On-Die Noise and Capacitance Measurement. [X. Zhang et al. 2013], [L. Smith et al. 2012] and [I.Novak et al. 2013] discussed worst-case PDN noise by reverse pulse technique. [K. Koo et al.2015] and [D. Hu et al.2015] extended CPM model for system core power optimization.

About PDN metrics Target Impedance [14]-[15], [L. Smith et al. 1999] proposed a target impedance to be met across a broad frequency range, [J. Kim et al. 2010, 2013] identified improved Target Impedance and IC transient measurement, [O. Dan et al. 2014] presented improved Target Impedance Method for PCB Decoupling of Core Power.

About power delivery network and PCB channel modeling, [16]-[101] provided related studied about power plane, via modeling and via-plane capacitance calculation related research work for passive interconnector electromagnetic (EM) modeling and analysis. The equivalent circuit model for system interconnectors was investigated from [16]-[32] by various methods including the cavity model and parallel plate partial element equivalent circuit (PEEC) methodology. In addition, related mathematical, analytical and experimental methodology from [33]-[101] were investigated by various researchers from different perspectives for the power delivery network (PDN) modeling and interconnectors electromagnetic (EM) performance modeling for the Chip-Package-PCB System.

#### **PAPER**

# I. SYSTEM LEVEL POWER INTEGRITY TRANSIENT ANALYSIS USING PHYSICS-BASED APPROACH

#### **ABSTRACT**

In this section, a methodology for system level end-to-end transient analysis was developed and validated in SIMPLIS tool with current path physics-based equivalent circuit model of board and package, simplified on-die power model and load current profile. Then compared the SIMPLIS small signal VRM model with different linear models of voltage regulator module (VRM) in both frequency domain and time domain, these comparisons and studies present the advantage of this methodology using equivalent circuit model for system level power integrity transient analysis. This thesis work also proposed a method of hybrid target impedance including current profile-based discrete and continuous target impedance. This hybrid target impedance could apply for system level PDN optimization to get a qualified and convergent solution to meet the supply voltage specification of the chip power. The PDN impedance optimization in frequency domain and voltage response validation in time domain are both achieved effectively in this thesis work with the hybrid target impedance and the physics-based equivalent circuit model.

#### 1. ON-CHIP POWER NETWORK AND LOAD TRANSIENTS

#### 1.1. ON-CHIP POWER NETWORK MODEL

Due to the continuous scaling on-die transistors process technology and increasing power consumption of the chips, the voltage noise related on-chip failure has drawn industrial-wide attention in past decades [4]-[6].

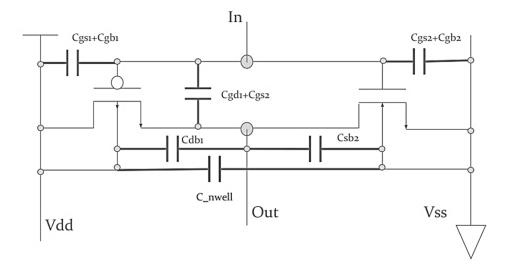

Figure 1. Parasitic Capacitance Circuit Representation of On-Die Transistors

Figure 2. Simplified Lumped Equivalent Chip Power Model

The chip power model (CPM) is a common chip power modeling approaches presented from Apache Design [4] for system level power integrity analysis and optimization. Full-chip switching scenario needs to be determined first in order to build the model of the on-chip power network. Non-switching instances with parasitics are modeled by their lumped RC equivalent circuit [4] as shown in figure 1. Then switching instances are modeled by a linearized macro-model including parametric voltage-dependent current sources as shown in figure 2.

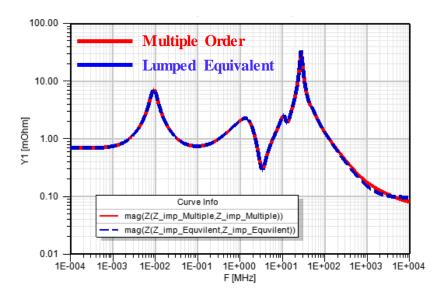

**1.1.1. Lumped and Reduced Order Power Model.** The passive RC network model includes that the original full-chip power network may contains 100M+ cells. These multiple order power model was reduced to lumped order as shown in figure 3, which might loss high frequency accuracy but could provide approximate voltage response as show in figure 4. Therefore, this reduced order lumped RC circuit model is desirable to employ the CPM model for on-PCB and on-PKG level design optimization.

Figure 3. Frequency Domain Comparison between Lumped Equivalent Power Model and Multiple Order Power Model

Figure 4. Time Domain Comparison between Lumped Equivalent Power Model and Multiple Order Power Model

1.1.2. Simplified Current Load and Pwl Current Profile. In the CPM model, the switching instance can be modeled by voltage-dependent current sources with piecewise linear (pwl) current profile as show in figure 5. The on-chip low power load operation was categorized from different operation origins [9]-[10] as shown in table 1. The dynamic clock gating is dominating frequency spectral components above clock frequency. The clock gating sequence is the key components to middle-lower frequency range, which need on-PCB and on-PKG DECAP for noise suppression.

This full-chip switching scenario can be determined with only focusing on clock gating sequence operation, categorized with random mode, step model and resonance mode scenario. From comparison in figure 7, the clock gating only scenario presented the similar spectral components at lower frequency to complete profile including pwl current. The higher frequency range above clock frequency cannot be optimized from system level, which can only be improved from on-die power network design and with on-die DECAP.

The clock gating only current profile can also give the same envelop on voltage response as shown in figure 8, which did not consider higher-frequency switching noise along the envelop as shown in figure 9. Therefore, this clock gating only current profile is desirable to employ the CPM model for on-PCB and on-PKG level design optimization.

Figure 5. Current Profile Modulation for Load Transients Modeling

Figure 6. Typical Operating Mode for Clock Gating Sequence

Table 1. On-chip Low Power Load Operation that Possibly Cause Critical Noise

| Load<br>Operating<br>Origin | Transition<br>Time | Expected<br>Freq.<br>Spectral<br>Components | Suppression<br>Technique                        | Consideration<br>for System PI<br>Analysis |

|-----------------------------|--------------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|

| DVFS                        | ms order           | < kHz                                       | VDD monitoring by VRM                           | Not required                               |

| Power Gating                | us to ms           | kHz ~ 0.1Mhz                                | VDD monitoring<br>by VRM and<br>current control | Not required                               |

| Clock Gating                | us order           | 0.1 ~ 100 Mhz                               | On-PCB Decap,<br>On-PKG Decap                   | Required                                   |

| Dynamic<br>Clock Gating     | ns order           | > 100 Mhz                                   | On-die decap                                    | Not required                               |

Figure 7. Frequency Domain between Simplified Current Load and Complete Current Load included pwl current profile with Full PDN Impedance Profile

Figure 8. Time Domain Comparison between Simplified Current Load and Complete Current Load included pwl current profile

Figure 9. Time Domain Ripple Comparison between Simplified Current Load and Complete Current Load included pwl current profile

#### 1.2. WORST-CASE LOAD SCENARIO TO PDN IMPEDANCE PEAK

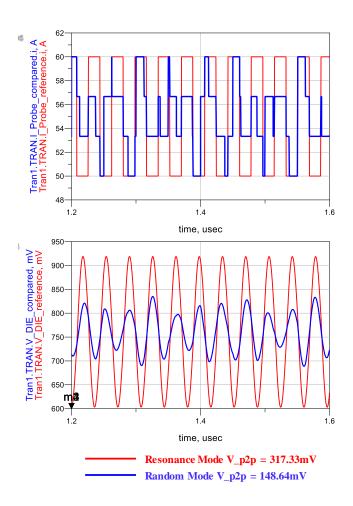

To achieve the worst-case current load is an essential part for predicting the maximum voltage noise to supplied chip through the PDN [9]-[12]. When the clock gating sequence is modulating in resonance model with period equal with inverse of the maximum anti-resonance peak, the current spectrum would hit the PDN impedance highest peak as shown in figure 10 to give an enormous voltage noise compared to random mode as shown in figure 11. From comparing to figure 10, random mode have multiple current spectral components, which split the energy from resonance peak at the resonance mode.

Figure 10. Frequency Domain - Random Mode Current Profile and Resonance Mode Current Profile with Full PDN Impedance Parallel Resonance Peak

Here are the steps for deploying the worst-case to PDN impedance peaks [5]:

- Cascaded the full PDN impedance and identify the frequency freq<sub>peak</sub> with the maximum impedance peak;

- 2. Generate the clock gating current sequence with the period  $T_{resonance} = 1/f_{req_{peak}}$  as resonance model in figure 6;

- 3. Modulated generated clock gating sequence with time-extended piecewise linear (pwl) current profile together;

- 4. Exported this worst-case switching pattern CPM profile for noise analysis.

Figure 11. Time Domain - Random Mode and Resonance Mode Current Profile and Voltage Response Comparison

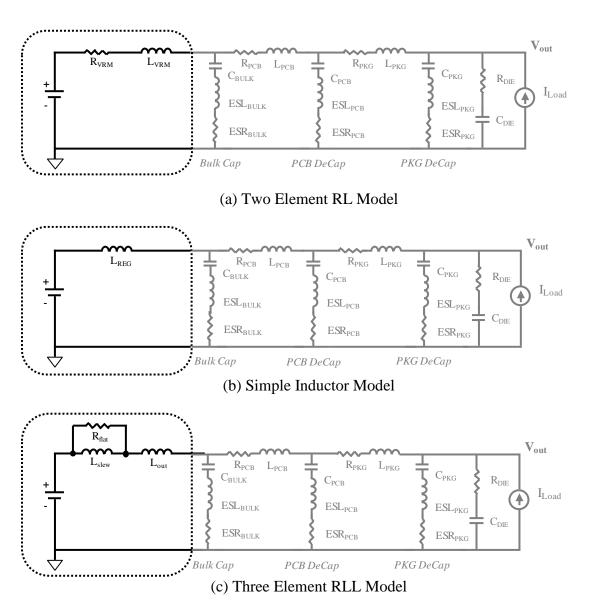

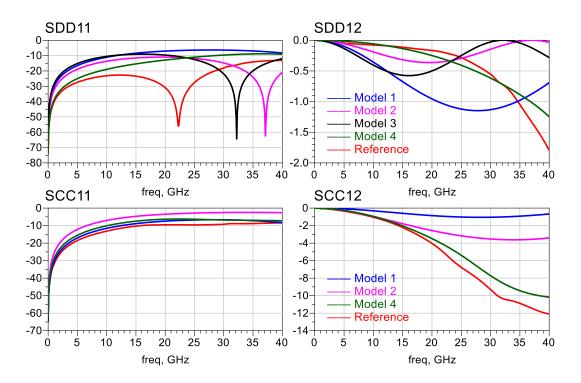

#### 2. PHYSICS-BASED EQUIVALENT CIRCUIT MODEL

#### 2.1. MODELING BASED ON CURRENT PATH PHYSICS

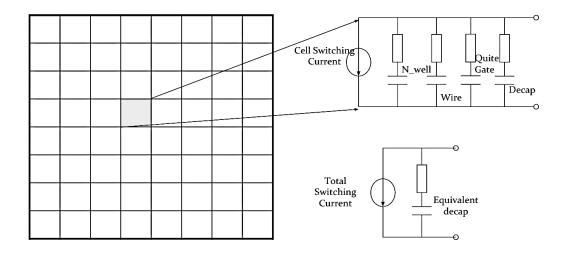

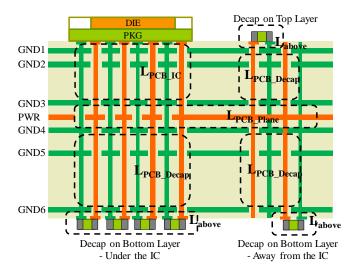

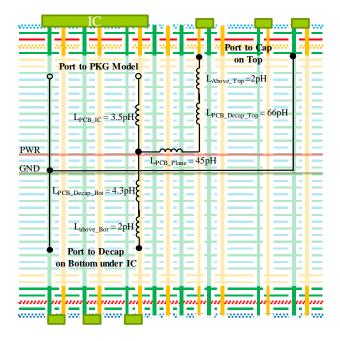

The power delivery network is mainly composed of these interconnecting structures including PCB and PKG to deliver power from VRM supply source to chip destination. The modeling on these passive structures is a critical topic for research for many years [15-21]. Based on the current path physics, the modeling of PCB could be divided into four segmentations as shown in figure 12., including the IC interconnection inductance  $L_{PCB\_IC}$ , the DECAP interconnection inductance  $L_{PCB\_DECAP}$ , the inductance of the current crossing the power plane area  $L_{PCB\_PLANE}$  and the mounting inductance from DECAP attaching to the PCB top plane  $L_{PCB\_IC}$ . The total equivalent inductance  $L_{PCB\_EQU}$  is the sum of all segments inductance given by equation (3.1). The specific inductance would be calculated based on the DECAP placement locations.

$$L_{PCB\_EQU} = L_{PCB\_IC} + L_{PCB\_DECAP} + L_{PCB\_Plane} + L_{above}$$

(3.1)

Figure 12. Geometry Segmentation based on Current Path

**2.1.1. Modeling of Printed Circuit Board.** To decrease the PDN impedance in middle frequency range that dominant by the equivalent inductance  $L_{PCB\_EQU}$ , the DECAP is the key elements. There are three categories of DECAP based on the DECAP placement locations as shown in figure 13.

- 1) DECAP on bottom layer and directly under the IC;

- 2) DECAP on bottom layer but away from the IC;

- 3) DECAP on top layer and side of the IC.

The equivalent circuit parameters was extracted based on above categories for a specific PCB casa as shown in figure 14, with left ports for connecting to PKG model, DECAP models on bottom and top layers of PCB. The presented circuits could be used in both frequency domain and time domain analysis with fast iteration. Most importantly, these provide flexible ports for DECAP from different location and physical metrics on these geometries. It could be desirable for doing PI margin analysis and design variation analysis from the equivalent circuit model.

Figure 13. PCB Modeling Based on DECAP Placement Locations

Figure 14. Equivalent Circuit Model Extraction for PCB

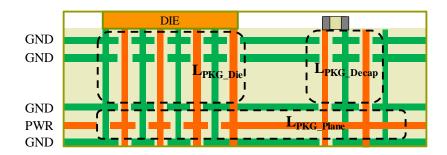

**2.1.2. Modeling of Chip Package.** To decrease the PDN impedance in middle-higher frequency range that dominant by the equivalent inductance of the package, the DECAP on package would be helpful. There are only one DECAP on top layer and side of the DIE as shown in figure 15. The equivalent circuit parameters was extracted for the example case as show in figure 16, the ports are connected to DIE model, PCB model and DECAP model on top layer of package.

Figure 15. PKG Modeling Based on DECAP Placement Locations

Figure 16. Equivalent Circuit Model Extraction for PKG

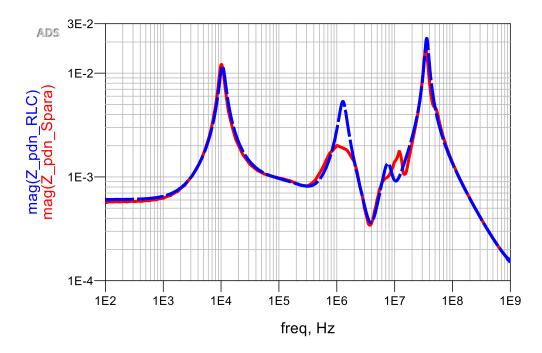

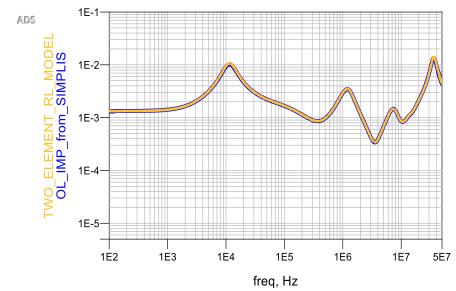

#### 2.2. END TO END PDN CASCADED EQUIVALENT CIRCUIT MODEL

With extracted PCB and PKG circuits elements, these can be cascaded to VRM model and CPM model from end to end for modeling the full PDN impedance as shown in figure 17. The impedance from equivalent circuit can be correlated with S-parameter model that was extracted from other commercial tool for full structure extraction as shown in figure 18. These resonance peaks in the impedance are related to the Q factor of RLC tank circuits. The accurate extraction on DC resistance of each segments are also critical for these peak amplitude. Once these equivalent circuit models for PCB and PKG are extracted and validated, they would be available for extending to time domain transient simulation for predicting the voltage noise on-die.

Figure 17. Cascaded Equivalent Circuit Models from End to End

Figure 18. Correlation between S-parameter Model and Equivalent Circuit Model

#### 3. SYSTEM LEVEL TRANSIENT ANALYSIS

#### 3.1. TRANSIENT SIMULATION WITH FULL PDN

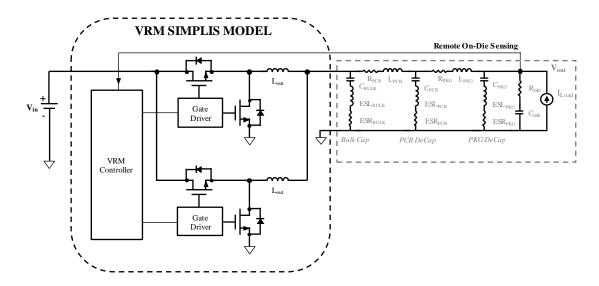

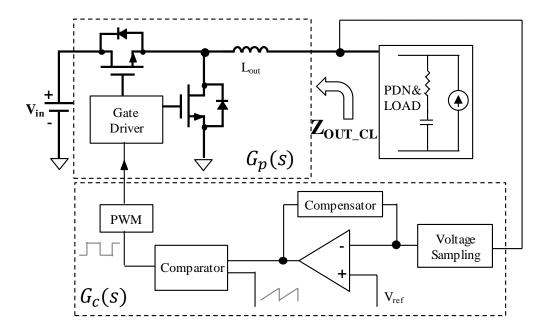

As mentioned in the introduction chapter, how to validate the full PDN design in time domain response for voltage noise is the ultimate goal for optimizing the full PDN. For an appropriate transient response prediction, the VRM model is an integral part of transient simulation with end-to-end power delivery network. The role of the VRM model provide not only the supply voltage to the system chip, but also compensation for dc voltage offset and lower frequency current fluctuation. The VRM model accuracy directly decides if predicted voltage response could qualify or fail with the supply design specification.

Figure 19. Two-Phase Synchronous Buck Converter Small Signal VRM Model in SIMPLIS with PDN Equivalent Circuits Models and Load Current

The VRM provider in the industry provides well-correlated small signal model in SIMPLIS tool from their product line. This vendor-provided VRM model would be a good choice from system level power integrity transient validation. However, the s-parameter

model or broadband spice model of interconnects networks including PCB and PKG cannot be compliable with small signal model in SIMPLIS tool. The methodology using physics based approach was presented in previous chapter to model interconnects networks by the equivalent circuit models. These equivalent circuit models can be cascaded with small signal model in SIMPLIS tool for transient simulation and validation.

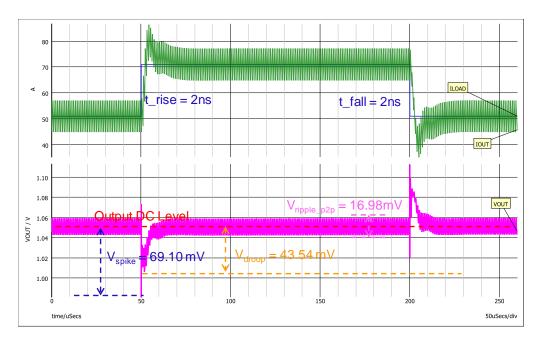

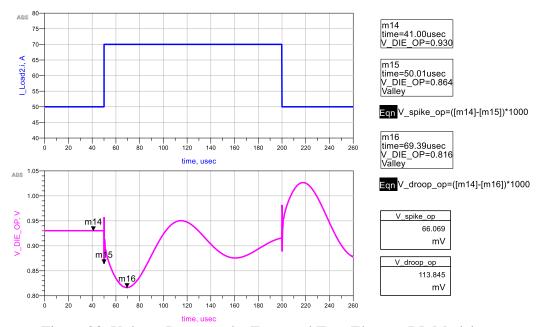

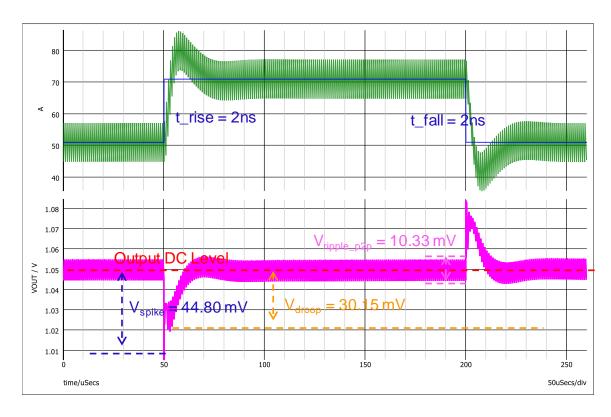

**3.1.1. Spike, Droop and Ripple of Voltage Response on DIE.** The voltage response of full system PDN that measured at Die is consisted of voltage spike, voltage droop, and voltage ripple as shown in figure 20. These three main ac noise would be the critical transient response, which need to suppress from optimizing physical parameters of the power delivery network. How to minimize these three types of voltage response is the design goal of the full system power integrity.

The identification on these three types of noise presented in table 4.1 from different perspectives of time lasting duration, frequency response range, and dominant capacitor in corresponded frequency range. From understanding in both time domain and frequency domain, the noise peak optimized to meet the design spec for the chip supply voltage.

The first voltage droop refers to voltage spike happens in nanosecond level, which can optimize from higher to middle frequency range by decoupling capacitors. The second voltage droop refers to voltage droop come into microsecond level, which can optimize from middle to lower frequency by bulk capacitors and decoupling capacitors with larger value. The voltage ripple noise caused from load switching and VRM MOSFET switching, the ripple by VRM MOSFET switching will be firstly concerned for system level PDN optimization. The load switching on die would optimize from on-die decoupling capacitors.

Figure 20. Identify on Spike, Droop and Ripple of Voltage Response on DIE

Table 2. Supply Voltage AC Noise and Design Spec

|                        | $ m V_{Spike}$    | $ m V_{Droop}$        | $ m V_{Ripple}$              |

|------------------------|-------------------|-----------------------|------------------------------|

| Time<br>Duration       | In nSeconds       | In uSeconds           | In uSeconds                  |

| Response<br>Frequency  | Middle Frequency  | Lower Frequency       | VRM n Phase * Switching Freq |

| Dominant<br>Capacitors | Decoupling<br>Cap | Bulk Cap<br>and DeCap | Decoupling<br>Cap            |

| Voltage<br>Design Spec | 3.0 %<br>30 mV    | 3.0 %<br>30 mV        | 1.0 %<br>10.0 mV             |

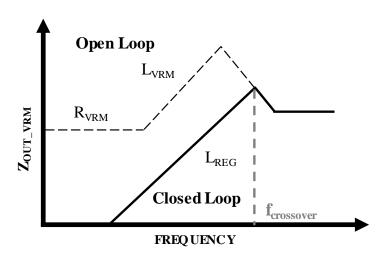

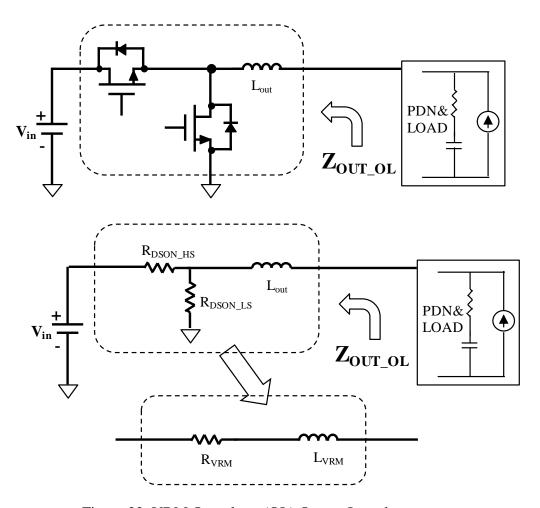

3.1.2. Output Impedance of Voltage Regulator Module (VRM). The switching mode power supply is main application for voltage supply to core power of system chip. For example, the synchronous buck converter shown in figure 19 is a common topology for voltage step-down application. When gate driver of the MOSFET switched with different duty cycle, output voltage from VRM provide scaled voltage to supplied chip. When looking from the chip die, the VRM output impedance is dominant at lower frequency impedance from dc to several kHz range of full system PDN impedance as shown in figure 1.3 and figure 21.

Figure 21. Comparison between OL and CL Output Impedance

The VRM output impedance varies with different working status for different supply to it and transient load on it. The output impedance generally divided into two categories of open loop output impedance and close loop output impedance based on the operation status. The feedback loop of the VRM have limitation to respond on current load change by the bandwidth of operational amplifier circuits in compensator. In fast current load changing, the VRM compensation circuit would not work for suppressing the voltage

noise response. The VRM that seen by PDN and load is directly as MOSFET turn-on resistance  $R_{DSON}$  and output inductor of the VRM.

Thus, a two-element linear RL model as below can give VRM output impedance in open loop:

$$Z_{OUT\_OL} = R_{VRM} + j\omega L_{VRM} \tag{4.1}$$

Where,  $Z_{OUT\_OL}$  is the open loop output impedance of the VRM,  $R_{VRM}$  is the equivalent resistance of high-side (HS) and low-side (LS) MOSFET turn-on resistance,  $L_{VRM}$  is the can be equivalent inductance of all phase output inductance for the VRM.

Figure 22. VRM Open loop (OL) Output Impedance

Due to negative feedback, output impedance in close loop responses as inductive behavior to pull down the output impedance of the VRM. The output voltage modulates to lower level voltage response for supplied device [2].

$$Z_{OUT\_CL} = \frac{Z_{OUT\_OL}}{1 + G_p(s) * G_c(s)} = sL_{REG}$$

$$\tag{4.2}$$

Where,  $s = j\omega = j \cdot 2\pi f$ ,  $Z_{OUT\_CL}$  is the close loop output impedance of the VRM,  $G_p(s)$  is the feedforward gain of the VRM,  $G_c(s)$  is the gain of feedback circuit,  $L_{REG}$  is the approximate equivalent inductance by a simple inductor with the value given by:

$$L_{REG} = \frac{Z_{OUT\_OL}/s}{1 + G_p(s) * G_c(s)} \tag{4.3}$$

The close loop impedance would be varying for different conditions with varied supply voltage to load current change. The equivalent inductance  $L_{REG}$  would also depend on the approximately extraction method and points frequency. The simple inductor model and extended three elements model discussed in next session.

Figure 23. VRM Closed loop (CL) Output Impedance

#### 3.2. VRM MODELS TRADEOFF FOR POWER INTEGRITY ANALYSIS

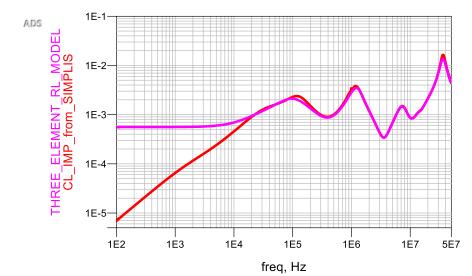

**3.2.1. Various VRM Models Extraction and Response.** This session provided comparison between different VRM models including small signal model, two-element RL model for open loop, simple inductor model and three-element for close loop.

The small signal models in SIMPLIS is a common analysis technique for VRM manufacture provider to design the power supply. The correlated and tuned model in encrypted version can be requested from VRM vendor. The SIMPLIS small signal models approximate the behavior of the switching mode power supply containing nonlinear device with linear equations. The small signal models can modeling the nonlinear effects including the discrete sample and hold effect of the switching mode power supply.

Based on the small signal models, the open loop and close loop output impedance could be accurately extracted from the SIMPLIS as shown in figure 24. These output impedance are showing the similar response as shown in figure 21. Other three linear VRM models would be extracted based on the open loop and close loop output impedance then compared their voltage response in the time domain to understand these models.

Figure 24. Extracted VRM Output Impedance from SIMPLIS Small Signal Model

Figure 25. Voltage Response by VRM Small Signal Model

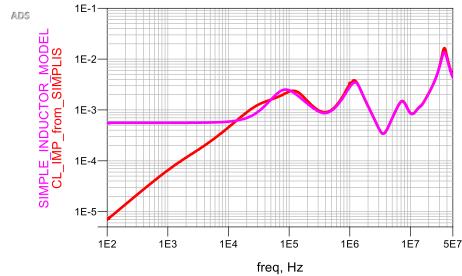

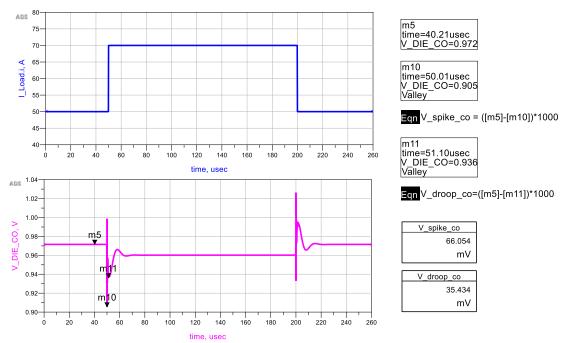

In power integrity analysis, the lumped two-element RL model is a common method to describe the impedance from the VRM as shown in figure 26..(a). From table 4.3, the parameters for the two-element RL model for open loop output impedance is shown as  $R_{VRM}$  and  $L_{VRM}$ , which parameters can be calculated by following the methods described in equation (4.1) and figure 22. The two-element RL model can be correlated with SIMPLIS extracted model as shown in figure 27. In addition, voltage response presented the approximately same amplitude for the first voltage spike, two-element RL model presented 66.06 mV compared to 69.10mV from voltage spike by small signal model in figure 28.

However, the second voltage droop was over-estimated to 113.84 mV comparing with 43.54 mV from voltage droop by small signal model in figure 25. Therefore, this lumped two-element RL model can predict the first voltage spike that response in higher-middle frequency range, but cannot accurate predict the second voltage droop that response

in middle-lower frequency range. Because the VRM model will affect the impedance in lower frequency by feedback loop control to change the PWM pulse width for modulating the output voltage. From frequency impedance perspective, the feedback loop control will change the loop gain to change the VRM output impedance, which refers to close loop impedance.

Figure 26. Typical Linear VRM Model

Table 3. Two Element RL Model - Extracted Parameters

| Parameters   | Value | Units |

|--------------|-------|-------|

| $R_{VRM}$    | 0.825 | mOhm  |

| $L_{ m VRM}$ | 75    | nН    |

Figure 27. Correlated Model between Two Element RL Model and SIMPLIS Model

Figure 28. Voltage Response by Extracted Two-Element RL Model

Table 4. Simple Inductor Model - Extracted Parameters

| Parameters   | Value | Units |

|--------------|-------|-------|

| $L_{ m REG}$ | 2.8   | nН    |

Figure 29. Correlated Model between Simple Inductor Model and SIMPLIS Model

Figure 30. Voltage Response by Extracted Simple Inductor Model

Table 5. Three-Element RLL Model - Extracted Parameters

| Parameters        | Value | Units |

|-------------------|-------|-------|

| R <sub>flat</sub> | 0.33  | mOhm  |

| L <sub>slew</sub> | 2.50  | nН    |

| L <sub>out</sub>  | 2.50  | nН    |

Figure 31. Three-Element RLL Model .vs. SIMPLIS Model

Figure 32. Voltage Response by Extracted Three-Element RLL Model

Small Signal 2-Element Simple 3-Element Model Linear RL Inductor Linear RL DC Drop  $0 \, \text{mV}$ 70mV 28mV 28mV 69.10mV 66.06 mV 66.05mV 66.05mV VSpike 43.54 mV VDroop 113.84 mV 35.43 mV 35.20 mV 16.96 mV  $m V_{Ripple}$

Table 6. Transient Response Comparison between Four Different VRM Models

**3.2.2. Summary on VRM Model Tradeoff.** From these compared results with different VRM models, the tradeoff on different VRM model is discussed in table 7 from different perspectives based on the results for transient response comparison between four different VRM models from table 6. We could also conclude these following guidelines for perform the system-level power integrity analysis:

- Time domain first response voltage spike is not directly relating to the VRM portion impedance, and these VRM models show the similar results;

- 2. Time domain second response voltage droop is directly relating to the lower frequency portion VRM impedance. The VRM small signal model can provide the most accurate voltage droop; the simple inductor and three-element RLL model can be approximately predicting the voltage droop.

- These simplified linear VRM models cannot predict the voltage ripple caused by VRM MOSFET switching, but the small signal model can.

- 4. The linear model extracted from close loop VRM impedance is a good choice for impedance optimization in frequency domain; the small signal model would be better choice for voltage response validation in time domain.

Table 7. Tradeoff on VRM model for System Level PI Simulation

|                                  | Small Signal<br>Model | 2-Element<br>Linear RL | Simple<br>Inductor | 3-Element<br>Linear RLL |

|----------------------------------|-----------------------|------------------------|--------------------|-------------------------|

| Implementation<br>Complexity     | Moderate              | Low                    | Low                | High                    |

| Applicable<br>Input/Load         | Dynamic               | Limited                | Limited            | Limited                 |

| VRM Output<br>Impedance          | Both OL and CL        | Open Loop              | Closed Loop        | Closed Loop             |

| Gain/Phase<br>Stability Analysis | Supported             | No                     | No                 | No                      |

| FD Impedance<br>Optimization     | Limited               | Overdesigned           | Supported          | Supported               |

| TD Response<br>Accuracy          | High                  | Low                    | Moderate           | Moderate                |

# 3.3. APPLICATION FOR SYSTEM LEVEL PI OPTIMIZATION

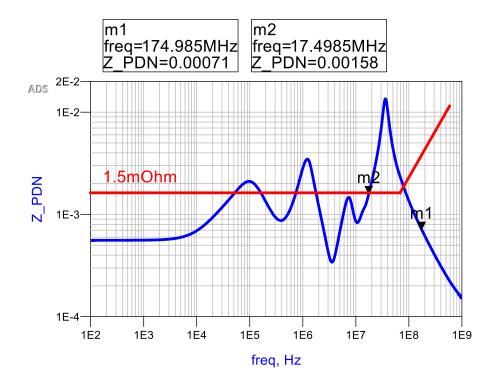

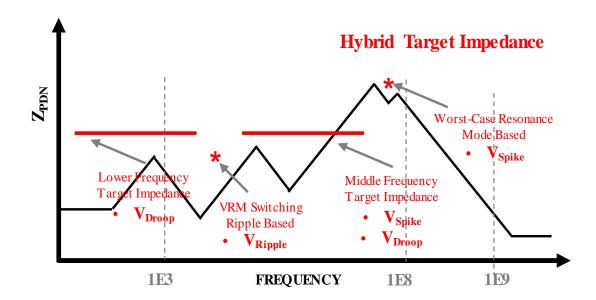

The conventional method to design power delivery network is by controlling the impedance under a metrics called target impedance [1], which assumed to be set as the ratio of the maximum tolerated voltage ripple to current change in the step by applying ohm's law in frequency domain. The example can be calculated for previous case by:

$$Z_{Target} = \frac{Voltage \, Ripple}{Current \, Change} = \frac{1V * 3\%}{20A} = 1.5 mohm$$

However, this target impedance can no longer be satisfied the broadband frequency for modern process with lower voltage and larger dynamic current. Then many authors

identified improved target impedance with IC transient current [13] and modified target impedance with modeling surging current [14]. The example can be calculated for previous case by:

$$f_{knee} = \frac{0.35}{T_r} = \frac{0.35}{2ns} = 175 Mhz$$

,  $Leq = T_r = 2nH$

Figure 33. Extremely difficult to meet above target impedance on system level

Nevertheless, these target impedance are extremely difficult to be met by system level optimization as shown in figure 33. The anti-resonance peak caused by package inductance and on-die decoupling capacitor would not be suppressed only with on-PCB and on-PKG decoupling capacitors to meet these target impedance. In addition, these metrics for system level PDN design would provide an over-design solution and even cannot get an achievable solution on system level PDN optimization. How to define better

metrics for PDN design would be critical on avoid these over-design by applying a novel definition on target impedance for system-level achievable solution and considering worst-case current scenario.

**3.3.1. Hybrid Target Impedance.** For core power of system chip, the current profile spectral components were identified in previous chapter by classifying with operation pattern and dominant frequency range. As show in figure 34, these current profile spectral components were listed with corresponded frequency to the full PDN impedance.

Based identified current components, the continuous target impedance in sectional type can be calculated based on conventional method for lower and middle frequency. Then breakpoint for this continuous target impedance are based on VRM output voltage switching ripple frequency, which usually need a lower impedance for smaller ripple noise as shown in figure 35.

Figure 34. Full PDN Impedance and Current Profile on DIE

Figure 35. Current Profile-based Discrete and Continuous Target Impedance

Above the middle frequency, that would be limited with another discrete impedance point for considering the worst-case scenario resonance peak. This impedance point would be larger than the continuous target impedance but it can give a limitation on impedance peak based on worst-case current harmonic components. These two discrete impedance points in hybrid target impedance either can be achieved from previous design data for a qualified product, or can be calculated based on the estimation for these current components and requirement to tradeoff between performance and cost.

The hybrid target impedance can help to avoid the over-design problem, and provide specific solutions for each voltage response noise including the voltage spike, voltage droop and voltage spike. Most important, these well-defined hybrid target impedance with continuous target impedance in sectional type and discrete target impedance for specific point would give a reasonable constrain for get an achievable solution in fast convergence.

**3.3.1. An Example for FD Optimization and TD Validation.** Finally yet importantly, a PDN optimization example was given in this session to apply the hybrid target impedance as constrain, use the linear VRM model for frequency domain optimization, and validate this optimized solution with small signal VRM model in time domain.

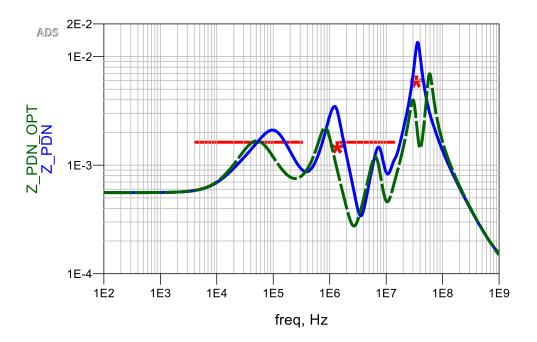

From figure 36, the optimized impedance was shown by green curve, which below the provided hybrid target impedance with red points for discrete impedance and red lines for continuous target impedance. From figure 37, the output voltage was provided including voltage spike with 44.80mV, voltage droop with 30.15mV and voltage ripple 10.33mV. Comparing with previous voltage response with the PDN impedance by the blue curve in figure 36, these voltage noises are all improved to lower level for voltage spike by 24.30mV, voltage droop by 13.39 mV and voltage ripple by 6.63mV as shown in table 8.

Figure 36. Impedance Optimization based on Hybrid Target Impedance

Table 8. Voltage Response Comparison between Previous and Optimized Case

|                 | Previous | Optimized | Difference |

|-----------------|----------|-----------|------------|

| $ m V_{Spike}$  | 69.10mV  | 44.80 mV  | 24.30 mV   |

| $V_{Droop}$     | 43.54 mV | 30.15 mV  | 13.39 mV   |

| $ m V_{Ripple}$ | 16.96 mV | 10.33 mV  | 6.63mV     |

Figure 37. Voltage Response for PDN-Optimized Case

#### REFERENCES

- [1] L. D. Smith, R. E. Anderson, D. W. Forehand, T. J. Pelc, and T. Roy, "Power distribution system design methodology and capacitor selection for modern CMOS technology," *IEEE Transactions on Advanced Packaging*, vol. 22, no. 3, pp. 284-291, 1999.

- [2] A. Waizman and Chee-Yee Chung, "Resonant free power network design using extended adaptive voltage positioning (EAVP) methodology," in *IEEE Transactions on Advanced Packaging*, vol. 24, no. 3, pp. 236-244, Aug. 2001.

- [3] S. Baek, P. Pun, and A. Agrawal, "Behavioral model of switching DC-DC converter for improving power delivery network design," in 2012 IEEE 62nd Electronic Components and Technology Conference, 2012, pp. 926-929.

- [4] E. Kulali, E. Wasserman and J. Zheng, "Chip Power Model A New Methodology for System Power Integrity Analysis and Design," 2007 IEEE Electrical Performance of Electronic Packaging, Atlanta, GA, 2007, pp. 259-262.

- [5] A. Waizman, M. Livshitz, and M. Sotman, "Integrated power supply frequency domain impedance meter (IFDIM)," in *Electrical Performance of Electronic Packaging 2004*, 2004, pp. 217-220.

- [6] L. Smith, S. Sun, P. Boyle, and B. Krsnik, "System power distribution network theory and performance with various noise current stimuli including impacts on chip level timing," in 2009 IEEE Custom Integrated Circuits Conference, 2009, pp. 621-628.

- [7] X. Zhang, Y. Liu, and C. Cheng, "Worst-case noise prediction using power network impedance profile," in 2013 ACM/IEEE International Workshop on System Level Interconnect Prediction (SLIP), 2013, pp. 1-8.

- [8] I. Novak," Systematic Estimation of Worst-Case PDN Noise", in proc of DesignCon 2015

- [9] K. Koo, Y. Lee, W. Beak, "Extended CPM for system power integrity analysis," in 2015 IEEE Electrical Design of Advanced Packaging and Systems Symposium (EDAPS), 2015, pp. 217-220.

- [10] K. Koo, Y. Lee, W. Beak, "Power Integrity Analysis of Chip-Package-System (CPS) of a mobile AP using Extended CPM technique," presented at the in DesignCon 2014, 2014.

- [11] D. Hu *et al.*, "System power noise analysis using modulated CPM," in *2015 IEEE Symposium on Electromagnetic Compatibility and Signal Integrity*, 2015, pp. 265-270.

- [12] B. Ko, J. Kim, J. Ryoo, C. Hwang, J. Song, and S. Kim, "Simplified Chip Power Modeling Methodology Without Netlist Information in Early Stage of SoC Design Process," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 6, no. 10, pp. 1513-1521, 2016.

- [13] J. Kim, Y. Takita, K. Araki, and J. Fan, "Improved Target Impedance for Power Distribution Network Design With Power Traces Based on Rigorous Transient Analysis in a Handheld Device," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 3, no. 9, pp. 1554-1563, 2013.

- [14] G. Chen and D. Oh, "Improving the target impedance method for PCB decoupling of core power," in 2014 IEEE 64th Electronic Components and Technology Conference (ECTC), 2014, pp. 566-571.

- [15] B. Zhao, S. Bai, C. Huang, J. Fan, A. Ruehli, J. Drewniak, H. Ye et al. "Surface Current Distribution for PCB PDN Geometry." In *Electrical Design of Advanced Packaging and Systems Symposium (EDAPS)*, 2015 IEEE, pp. 113-116. IEEE, 2015.

- [16] B. Zhao, K. Hardin, A. Hosseinbeig, Y. S. Cao, N. Dikhaminjia, Z. Kratzer, J. Fessler, J. Drewniak, "A Novel Z-Directed Embedded Component for the Reduction of Voltage Ripple on the Power Distribution Network for PCBs." *IEEE Electromagnetic Compatibility Magazine* 6, no. 3: 91-97.

- [17] B. Zhao, S. Bai, S. Connor, M. Cocchini, D. Becker, M. A. Cracraft, A. Ruehli, B. Archambeault, and J. Drewniak. "System level power integrity analysis with physics-based modeling methodology", *IEEE Electromagnetic Compatibility and Signal Integrity Symposium*, 2018.

- [18] B. Zhao, Z. Chen, D. Becker, "Impacts of Anisotropic Permittivity on PCB Trace and Via Modeling", *IEEE Electrical Performance of Electronic Packaging (EPEPS)*, 2018.

- [19] B. Zhao, S. Pan, and J. Fan. "Green's Functions in Lossy Multi-Layer Dielectrics for 3D IC/Packaging Applications." In 2018 IEEE International Conference on Computational Electromagnetics (ICCEM), pp. 1-3. IEEE, 2018.

- [20] K. Shringarpure, B. Zhao, B. Archambeault, A. Ruehli, J. Fan, and J. Drewniak. "Effect of narrow power fills on PCB PDN noise." *2014 IEEE International Symposium on Electromagnetic Compatibility (EMC)*, pp. 839-844. IEEE, 2014.

- [21] K. Shringarpure, B. Zhao, L. Wei, B. Archambeault, A. Ruehli, M. Cracraft, M. Cocchini, E. Wheeler, J. Fan, J. Drewniak., "On Finding the Optimal Number of Decoupling Capacitors by Minimizing the Equivalent Inductance of the PCB PDN," 2014 IEEE International Symposium on Electromagnetic Compatibility (EMC), 2014.

# II. A SURVEY ON MODELING STRATEGIES FOR HIGH-SPEED DIFFERENTIAL VIA BETWEEN TWO PARALLEL PLATES

#### **ABSTRACT**

This paper presents a survey on physics-based modeling strategies for differential via in high-speed multi-layer printed circuits (PCBs). Driven by the goals of accurate and efficient design, researchers have explored several approaches for differential via modeling, including π-type RLC circuit, differential transmission line with via-plate capacitance/ effective dielectric constant and parallel plate impedance model. This survey provides overviews of these modeling strategies and comparisons by correlating mixed-mode S-parameter from HFSS. In particular, this paper then aims on building a generic parameterized and SPICE-compatible circuit model for designing differential via in a frequency range up to 40GHz.

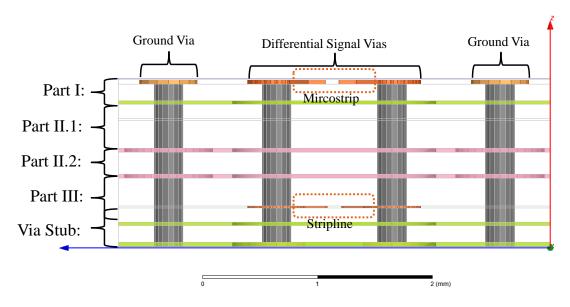

# 1. INTRODUCTION OF DIFFERENTIAL VIA

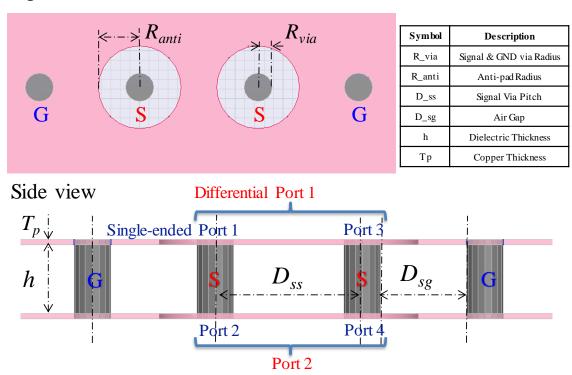

Differential via is a common signal transition in multi-layer printed circuit board (PCB). For high-speed channel with data rates above tens of Gbps, it contributes a critical discontinuity to distort and degrade signal. This paper reviewed four types of differential via modeling strategies. These models can be utilized for the via structure development. An accurate geometry-dependent and SPICE-compatible circuit model is needed for geometrical parameters optimization of an example of the differential via pairs between two parallel plates as shown in figure 1, which is the part II in figure 2 that segmented by the divide-and-conquer method for differential via modeling.

# Top view

Figure 1. Geometry of the differential via pairs between planes

There is a lot of research done on via modeling in past years. The work on simple lumped element circuit RLC model did based with some analytical approximation and optimization methods [1-4]. These lumped circuit models are too complicated to understand and extract for their parameters. An equivalent model based on transmission line with via-plate capacitance was applied with space-mapping neural network technique for simplified SPICE-compatible application[5]. However, the model parameter extraction are still complicated and time-consuming. Another simplified and efficient transmission line model proposed with effective dielectric constant calculation in differential mode [6-8]. However, via structure for a practical PCB board is excited by vertical current with

parallel plane waves between two parallel plates. The higher order evanescent modes cannot be involved in above models. The parallel plate impedance model was studied with considering plane effects in many papers [9-19].

In this paper, these differential via models were studied comparatively and comprehensively for understanding their accuracy, physical meaning, application limitation and design flexibility. This work can help to know how to select a flexible model for a specific application objective. In section II introduce each structure and circuit model of four differential via models. In section III and IV, mixed-mode S-parameters comparison between these models and full-wave simulation reference are presented and analyzed quantitatively with error percentage in linear scale. Based on comparison and studying, an accurate parameterized model for designing differential via is developed.

Figure 2. Divide-and-conquer method for differential via modeling

# 2. SURVEY OF MODELING STRATEGIES

# 2.1. PHYSICS BASED RLC CIRCUIT MODEL

A physics-based via model can be developed by peeling and partitioning method and analyzing current distributing path through via structure [1, 2]. The displacement current paths are represented by capacitances Ct and Cm. The partial inductance Lv (via barrels part between plates) and the mutual inductance Lm (between via barrels) of via barrels must be taken into account as well. The resistance shown in model 1 from figure 3 are frequency dependent and calculated by

$$R(f) = R_t \cdot \sqrt{f} \tag{7.1}$$

where, the  $R_t$  are the skin-effect effective resistance with the unit of  $\Omega/\sqrt{Hz}$ , and f is frequency in Hz.

These RLC parameters are extracted from the commercial full-wave HFSS/Q3D tools based on the physical meaning. And these extracted parameter are substituted into the circuit model 1 to calculate the single-ended S-parameter. Then, the mixed-mode S-parameter are converted from these calculated S-parameter for comparing with reference.

Figure 3. Model 1 - RLC  $\pi$ -type circuit model

#### 2.2. TRANSMISSION LINE MODEL WITH VIA-PLATE CAPACITANCE

A coupled transmission line (TL) model is used to model via barrel part in a lower bandwidth under 20 GHz. The mixed-mode impedance  $Z_{even}$  and  $Z_{odd}$  were calculated by the Q2D tool by modeling via barrels as the transmission line model. The electrical length  $EL_{via}$  in degree is calculated with the physical length of via barrel. The via to plate capacitance  $C_{t2}$  and mutual capacitance  $C_{m2}$  can be added at terminals of transmission line model for describing an entire via between two plates as shown in figure 4.

The  $C_{t2}$  models the coaxial capacitance between via barrel in planes and the reference ground planes. The  $C_{m2}$  models the capacitive coupling between via barrels in the planes. These capacitance in this model were trained by some optimization algorithms [5]. However, these capacitance parameters were also extracted from full wave simulation tools for aiming to build the generic parameterized model.

Figure 4. Model 2 - Transmission line model with via-plate capacitance

# 2.3. TL MODEL WITH EFFECTIVE DIELECTRIC CONSTANT

Another transmission line model was studied in a series of paper [6-8] based on analytical equations for characteristic impedance and effective dielectric constant. By

analyzing differential via holes as a twin-rod transmission line geometry, the differential impedance  $Z_{diff}$  and differential effective dielectric constant  $DK_{eff}$  are calculated by following equations (2, 3). These two derived parameters were put back into the coupled transmission line model as shown in figure 5.

The differential effective dielectric constant  $DK_{eff}$  can also be extracted by HFSS tool or calculated from average effective dielectric constant with a combination of the anisotropic property of dielectric material plus the capacitive loading effect of the anti-pads [6]. These is most important part for this simple circuit model.

$$Z_{diff} = \frac{120}{\sqrt{Dk_{eff}}} \times \ln\left(\frac{s}{2r} + \sqrt{\left(\frac{s}{2r}\right)^2 - 1}\right)$$

(7.2)

$$Dk_{eff} = Dk_{avg} \times \ln\left(\frac{s}{2r} + \sqrt{\left(\frac{s}{2r}\right)^2 - 1}\right)$$

(7.3)

Where, s is the signal via to signal via pitch, r is radius of signal via barrel.

Figure 5. Model 3 - Transmission line model with effective dielectric constant

# 2.4. PARALLEL PLATES IMPEDANCE ZPP MODEL

To involve the higher order evanescent modes in the model, plane effect must be considered by cavity model with parallel plate impedance that was studied from many papers [9-19]. This parallel plate impedance matrix Z is calculated by analytical equations (4, 5). It is a frequency-dependent table of impedance. The cavity port i and j for impedance matrix Z are cylindrical ports between two plates as shown in figure 6. With corresponded ports connecting as in shown by figure 7, this parallel plate impedance matrix Z is substituted into circuit model in figure 8 with capacitance  $C_p$  for modeling the entire via between two plates.

$$Z_{ii} = \frac{V_i}{I_i} = \frac{j\omega\mu h}{2\pi k r_i} \cdot \frac{H_0^{(2)}(k r_i)}{H_1^{(2)}(k r_i)}$$

(7.4)

$$Z_{ji} = \frac{V_{j}}{I_{i}} = \frac{j\omega\mu h}{2\pi k r_{i}} \cdot \frac{H_{0}^{(2)}(kr_{ij})J_{0}(kr_{j})}{H_{1}^{(2)}(kr_{i})}$$

(7.5)

$$C_a = \frac{2\pi\varepsilon_r \varepsilon_0 t}{\ln(b/a)} \tag{7.6}$$

$$C_b = \frac{4\pi\varepsilon_r \varepsilon_0 t}{h \ln(b/a)} \sum_{n=1,3,5,\dots}^{2N-1} \frac{(1 - \Gamma_a^{(n)} \Gamma_R^{(n)})^{-1}}{k_n^2 H_0^{(2)}(k_n a)}$$

(7.7)

$$C_p = C_a + C_b \tag{7.8}$$

Where a is the radius of via, b is the radius of anti-pad, t is the thickness of the reference plate, h is the via barrel physical length.  $\varepsilon_r$  is the relative permittivity of the dielectrics in which the via is embedded. R is the outer boundary. N is the mode number.  $k_n$  is the wavenumber calculated by (4).  $\Gamma_a$  and  $\Gamma_R$  are the reflection coefficients for any  $TM_{zn}$  mode with different boundary conditions [11].

The via-plate capacitance  $C_p$  is sum of coaxial capacitance  $C_a$  and via barrel to plate capacitance  $C_b$  that are calculated by analytical equations (6, 8).

This approach is more efficient than the numerical method and can be integrated with SPICE circuit model. Furthermore, these analytical equations are fully geometry-related, which can be utilized for via structure optimization design with a generic model. And it can support a rather higher frequency to 40Ghz and well-correlated with measurement results[9, 10].

Figure 6. Illustration of four ports between two parallel plates

Figure 7. Illustration of circuit model - Parallel plates Impedance Zpp model

Figure 8. Circuit model for Model 4 - Parallel plates Impedance Zpp model

# 3. TWO-LAYERS CASE COMPARISON

In this section, above mentioned via models are used to generate S-parameter by SPICE circuit model. The correlation accuracy between these models and reference is presented here and evaluated by linear scale error percentage. The single differential via between 2-layer plates in figure 1 is simulated by a finite element method (FEM) based commercial tool as a reference of the frequency range from 20Mhz to 40Ghz. The geometry parameters for this example are  $R_{via} = 5$ mil,  $R_{anti} = 16$ mil,  $D_{ss} = 45$ mil,  $D_{sg} = 20$ mil, h = 10mil,  $T_p = 0.6$ mil and dielectric constant = 3.68.

The mixed mode S-parameter was obtained from the four methods and reference for comparison in figure 9. Table I and II also provide the linear scale error for SDD12 and SCC12 at three frequency points of 14 Ghz, 28Ghz and 40Ghz. The model 3 only support differential mode, so common mode comparison between model 3 and reference was not included.

Figure 9. Mixed mode S-parameter comparison for via with 2-layer plates

Table 1. Linear Scale Error for Sdd12 for via with 2-layer plates

| Sdd12   | % Error between models and reference |         |         |         |

|---------|--------------------------------------|---------|---------|---------|

| 2-layer | Model 1                              | Model 2 | Model 3 | Model 4 |

| 14Ghz   | 1.00%                                | 1.01%   | 0.51%   | -0.84%  |

| 28Ghz   | 4.55%                                | 4.55%   | 2.32%   | -1.46%  |

| 40Ghz   | 5.71%                                | 2.45%   | 0.69%   | -1.74%  |

Table 2. Linear Scale Error for Scc12 for via with 2-layer plates

| Scc12   | % Error between models and reference |         |         |  |

|---------|--------------------------------------|---------|---------|--|

| 2-layer | Model 1                              | Model 2 | Model 4 |  |