Scholars' Mine

Masters Theses

Student Theses and Dissertations

Spring 2017

# A physics-based approach for power integrity in multi-layered PCBs

Biyao Zhao

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electromagnetics and Photonics Commons Department:

#### **Recommended Citation**

Zhao, Biyao, "A physics-based approach for power integrity in multi-layered PCBs" (2017). *Masters Theses*. 7670. https://scholarsmine.mst.edu/masters\_theses/7670

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# A PHYSICS-BASED APPROACH FOR POWER INTEGRITY IN MULTI-LAYERED PCBs

by

# BIYAO ZHAO

# A THESIS

Presented to the Faculty of the Graduate School of the

## MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

## MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

2017

Approved by

James L. Drewniak, Advisor Jun Fan David Pommerenke

© 2017

Biyao Zhao All Rights Reserved

#### ABSTRACT

Developing a power distribution network (PDN) for ASICs and ICs to achieve the low-voltage ripple specifications for current digital designs is challenging with the highspeed and low-voltage ICs. Present methods are typically guided by best engineering practices for low impedance looking into the PDN from the IC. A pre-layout design methodology for power integrity in multi-layered PCB PDN geometry is proposed in the thesis. The PCB PDN geometry is segmented into four parts and every part is modelled using different methods based on the geometry details of the part. Physics-based circuit models are built for every part and the four parts are re-assembled into one model. The influence of geometry details is clearly revealed in this methodology. Based on the physicsbased circuit mode, the procedures of using the pre-layout design methodology as a guideline during the PDN design is illustrated. Some common used geometries are used to build design space, and the design curves with the geometry details are provided to be a look up library for engineering use.

The pre-layout methodology is based on the resonant cavity model of parallel planes for the cavity structures, and parallel-plane PEEC (PPP) for the irregular shaped plane inductance, and PEEC for the decoupling capacitor connection above the top most or bottom most power-return planes. PCB PDN is analyzed based on the input impedance looking into the PCB from the IC. The pre-layout design methodology can be used to obtain the best possible PCB PDN design. With the switching current profile, the target impedance can be selected to evaluate the PDN performance, and the frequency domain PDN input impedance can be used to obtain the voltage ripple in the time domain to give intuitive insight of the geometry impact on the voltage ripple.

#### ACKNOWLEDGMENTS

I would like to take this opportunity to express my sincere gratitude to Prof. Drewniak and Prof. Fan for the incredible support and guidance with professional skills development and research work. I would also to thank Prof. Pommerenke for suggestions and inspirations through my master program. I'm also grateful for all the members of the "Electromagnetic Compatibility Laboratory" at Missouri University of Science and Technology for all the support and encouragement through the process.

I would like to thank my parents for all the support, encouragement, and love through my education.

# TABLE OF CONTENTS

| ABSTRACTii                                                                          | i |

|-------------------------------------------------------------------------------------|---|

| ACKNOWLEDGMENTS iv                                                                  | 7 |

| LIST OF ILLUSTRATIONS                                                               | i |

| LIST OF TABLES xi                                                                   | i |

| SECTION                                                                             |   |

| 1. INTRODUCTION                                                                     | l |

| 2. PHYSICS BASED METHODOLOGY FOR PCB PDN                                            | 1 |

| 2.1. CIRCUIT EXTRACTION FORM CAVITY MODEL                                           | 1 |

| 2.2 PARALLEL-PLATE PEEC                                                             | 5 |

| 2.3. PMSR FOR DECAP CONNECTION MODELING                                             | ) |

| 3. PCB PDN DESIGN CRITERIA                                                          | l |

| 3.1. GENERIC PCB PDN INPUT IMPEDANCE11                                              | l |

| 3.2. TARGET INPUT IMPEDANCE DEFINITION11                                            | l |

| 3.3. SURFACE CURRENT ANALYSIS 13                                                    | 3 |

| 3.3.1. Test Geometry for Current Density Distribution                               | 1 |

| 3.3.2. Current Distribution Comparison between the Cavity Model and Plane-Pair PEEC | 5 |

| 3.3.3. Current Distributions in the PCB PDN Structures                              | 5 |

| 3.4. GEOMETRY SEGMENTATION                                                          | 3 |

| 3.5. EQUIVALENT INDUCTANCE AS CRITERIA 19                                           | ) |

| 4. L <sub>PCB_IC</sub> CONVERGENCE                                                  | l |

| 4.1. LPCB_IC SEGMENTATION IN THE STACK-UP                                           | l |

| 4.2. IC PIN PLACEMENT PATTERNS                                                      | l |

| 4.2.1. Circuit Reduction and Rigorous L <sub>PCB_IC</sub> Formulation               | 2 |

| 4.2.2. L <sub>PCB_IC</sub> Simulation Results Comparison                            | 1 |

| 4.3. UNIT CELL APPROACH FOR L <sub>PCB_IC</sub> APPROXIMATION                       | 5 |

| 4.4. SELF AND MUTUAL INDUCTANCE EXTRACTION IN LPCB_IC 27                            | 7 |

| 4.5. MEASUREMENT FOR LPCB_IC CONVERGENCE                                            | 3 |

| 5. L <sub>PCB_Decap</sub> CONVERGENCE                                               | ) |

| 5.1. L <sub>PCB_Decap</sub> DEFINITION                                              | ) |

| 5.2. DECAP CONNECTION INDUCTANCE CONVERGENCE CRITERIA 29                            | ) |

| 5.3. DECOUPLING CAPACITOR PLACEMENT PATTERNS                                           | . 30 |

|----------------------------------------------------------------------------------------|------|

| 5.4. LPCB_Decap FORMULATION                                                            | . 32 |

| 5.5. L <sub>PCB_Decap</sub> MODELING RESULTS COMPARISON FOR DIFFERENT<br>DECAP LAYOUTS |      |

| 5.6. L <sub>PCB_Decap</sub> FORMULATION FOR THE THREE PLACEMENT<br>PATTERNS            | . 35 |

| 5.7. MUTUAL INDUCTANCE INFLUENCE IN LPCB_Decap                                         | . 38 |

| 5.8. L <sub>PCB_Decap</sub> DESIGN CURVES AND DESIGN PROCEDURES                        | . 39 |

| 5.8.1. L <sub>PCB_Decap</sub> Design Library                                           | . 39 |

| 5.8.2. Procedures to Design the L <sub>PCB_Decap</sub> Convergence                     | . 40 |

| 5.9. VALIDATION OF LPCB_Decap CONVERGENCE                                              | . 40 |

| 6. L <sub>PCB_Plane</sub> CONVERGENCE                                                  | . 43 |

| 6.1. L <sub>PCB_plane</sub> EXTRACTION BASED ON THE CAVITY MODEL                       | . 43 |

| 6.2. L <sub>PCB_Plane</sub> MODELING BASED ON PPP                                      | . 46 |

| 7. Labove DESIGN                                                                       | . 48 |

| 7.1. Labove MODELS AND RESULTS                                                         | . 48 |

| 7.2. NINE CAPACITOR PLACEMENT PATTERNS AND DESIGN SPACE                                | . 51 |

| 8. PHYSICS-BASED CIRCUIT MODEL FOR PCB PDN                                             | . 53 |

| 9. VOLTAGE RIPPLE CALCULATION                                                          | . 54 |

| 9.1. BEHAVIOR CIRCUIT MODEL FOR VOLTAGE RIPPLE<br>CALCULATION                          | . 54 |

| 9.2. FREQUENCY SEGMENTATION                                                            | . 55 |

| 9.3. PARAMETERS FITTING                                                                | . 56 |

| 9.4. EQUIVALENT CIRCUIT FOR EVERY FREQUENCY RANGE                                      | . 57 |

| 9.5. VOLTAGE RIPPLE CALCULATION                                                        | . 58 |

| 9.6. APPLICATION TO REAL-WORLD PCB                                                     | . 61 |

| 10. PRE-LAYOUT DESIGN METHODOLOGY PROCEDURE                                            | . 64 |

| 10.1. PRE-LAYOUT DESIGN CRITERIA                                                       | . 64 |

| 10.2. L <sub>PCB_IC</sub> DESIGN                                                       | . 65 |

| 10.3. PRE-LAYOUT DESIGN APPROACH BASED ON LPCB_Decap                                   | . 65 |

| 10.4. DESIGN APPROACH BASED Labove                                                     | . 65 |

| 10.5. DESIGN APPROACH BASED ON LPCB_Plane DOMINANT                                     | . 66 |

| 11. DISCUSSIONS AND CONCLUSION                                                         | . 67 |

| BIBLIOGRAPHY |  |

|--------------|--|

| VITA         |  |

# LIST OF ILLUSTRATIONS

| Figure 2.1. (a) An open plane-pair cavity with four vias; (b). The equivalent circuit mode based on the cavity model in [17];                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.2. (a) A multilayer power/ground structure with multiple via connections, and, (b) its corresponding circuit model from the cavity model                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7    |

| Figure 2.3. The mesh used around the vias in one cavity for the inductance calculation based on PPP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8    |

| Figure 2.4. Decap connection above the PCB separation, (a) Decap connection definition, (b) Labove when the decaps are shorted, (c) Decap part in the decap conection.                                                                                                                                                                                                                                                                                                                                                                                                            | 10   |

| Figure 2.5. The physics-based circuit model extraction based on the PMSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 10 |

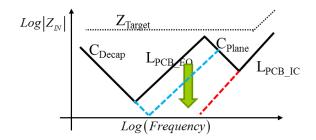

| Figure 3.1. The generic PCB PDN input impedance. By adding decoupling capacitors, the mid frequency range inductance reduces.                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12   |

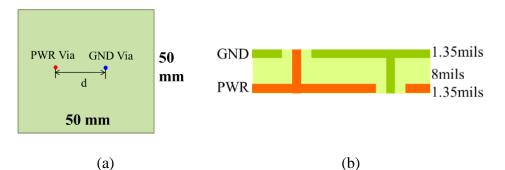

| Figure 3.2. A plane-pair cavity with a power via and a shorting ground via placed with distance d, (a) top view of the test case, (b) stack-up of the test case. [27]                                                                                                                                                                                                                                                                                                                                                                                                             | 15   |

| Figure 3.3. Circuit model for geometries shown in Figure 3.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 15 |

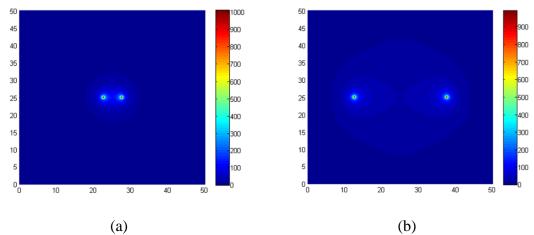

| Figure 3.4. Current density plot based on the cavity model for the geometry shown in Figure 3.2 with different d values, (a) d=5mm, (b) d=25mm. [27]                                                                                                                                                                                                                                                                                                                                                                                                                              | 15   |

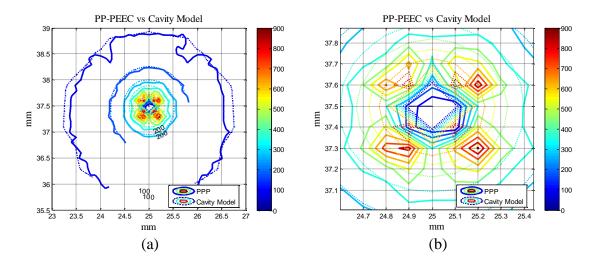

| Figure 3.5. Current density comparison around the vias between cavity model and PP-PEEC for the geometry shown in Figure 3.2 for d=25mm, (a). the via region, (b).zoom-in region for the via center shown in (a). [27]                                                                                                                                                                                                                                                                                                                                                            | 16   |

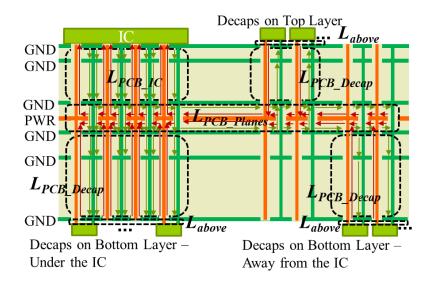

| Figure 3.6. A stack-up of a high-layer count PCB PDN geometry with a power net fill and the definitions of the parts segmented from the PCB PDN geometry. [17]                                                                                                                                                                                                                                                                                                                                                                                                                    | 19   |

| Figure 4.1. IC interconnection inductance extraction in the PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

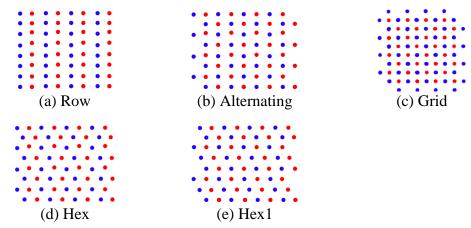

| Figure 4.2. Five IC pin placement patterns with different power and power-return relative locations, (a). Row placement pattern with power and power-return vias placed in a row, (b). Regular placement pattern with power and power-return vias placed alternating, (c). Grid placement pattern with the unit cell of one power via surrounded by four power-return vias, (f). Hex placement pattern with power and power-return vias placed alternating in hexagonal pattern, (e) Hex 1 placement pattern with another configuration of power and power-return vias as in (d). |      |

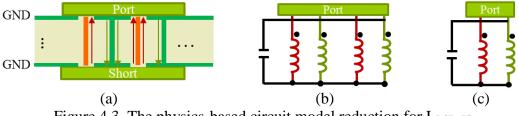

| Figure 4.3. The physics-based circuit model reduction for L <sub>PCB_IC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

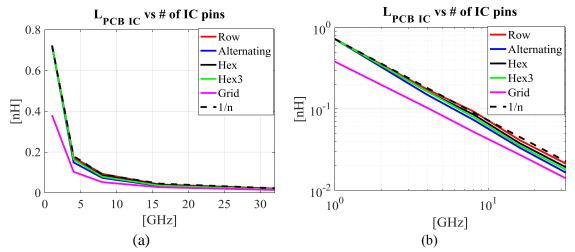

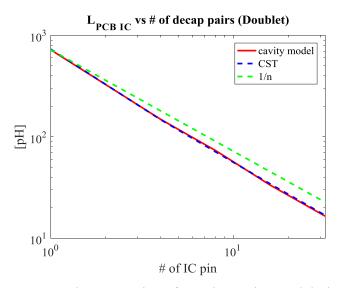

| Figure 4.4. L <sub>PCB_IC</sub> comparison for the IC pin placement patterns shown in Figure 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25   |

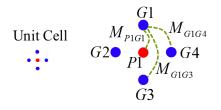

| Figure 4.5. Unit cell definition in the IC pin placement pattern and the mutual inductance definitions                                                                                                                                                                                                                                                                                                                             | 26 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

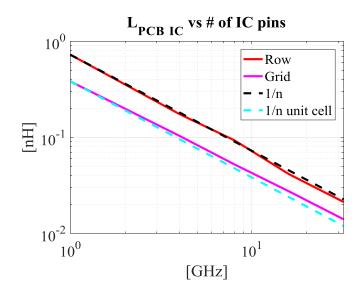

| Figure 4.6. L <sub>PCB_IC</sub> formulation validation shown in (25).                                                                                                                                                                                                                                                                                                                                                              | 27 |

| Figure 4.7. Stack up details of the test cases with IC pins added incrementally in the center.                                                                                                                                                                                                                                                                                                                                     | 28 |

| Figure 4.8. L <sub>PCB_IC</sub> results comparison from the cavity model, the formulas, and CST for alternating placement pattern.                                                                                                                                                                                                                                                                                                 | 28 |

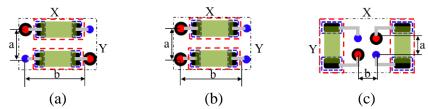

| Figure 5.1. Three decoupling capacitor placement patterns used in the thesis, (a) Alternating placement patterns with the neighbour vias of the decap placed in different directions; (b) Aligned placement patterns with the neighbour vias of the decap placed in different directions; (c)Doublet placement patterns with vias placed as close as possible in alternating directions.                                           | 30 |

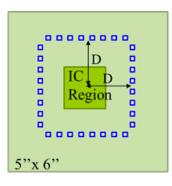

| Figure 5.2. The decap pair locations with decaps placed in a line with the distance D to the IC region used in the alternating, aligned and doublet placement patterns                                                                                                                                                                                                                                                             | 31 |

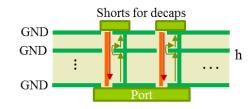

| Figure 5.3. The stack-up settings to extract decap interconnection inductance L <sub>PCB_Decap</sub> .                                                                                                                                                                                                                                                                                                                             | 32 |

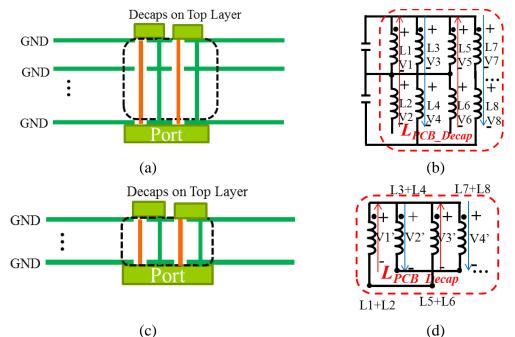

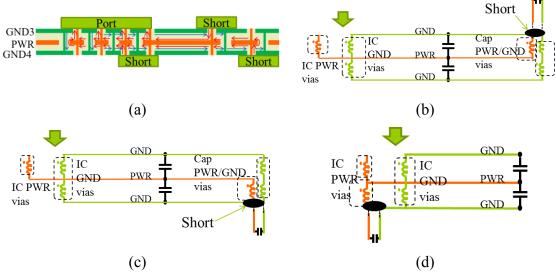

| Figure 5.4. Physics-based circuit model reduction for the L <sub>PCB_Decap</sub> calculation based<br>on the cavity model, (a) L <sub>PCB_Decap</sub> stack-up extracted from the high layered<br>stack-up shown in Fig, (b) one-to-one corresponding circuit model for (a), (c)<br>the stack-up after the series reduction applied to the geometry in (a), (d) one-to-<br>one corresponding circuit model for the geometry in (c) | 33 |

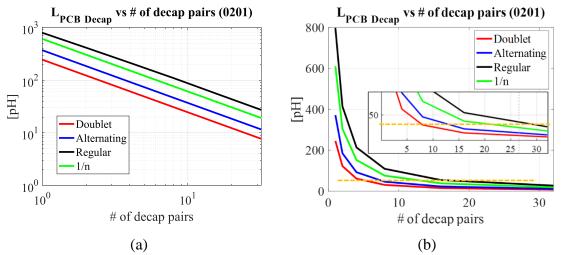

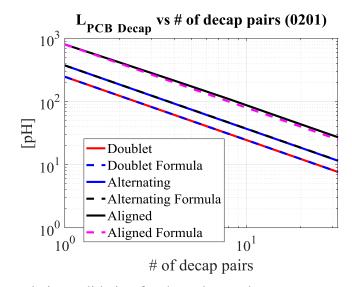

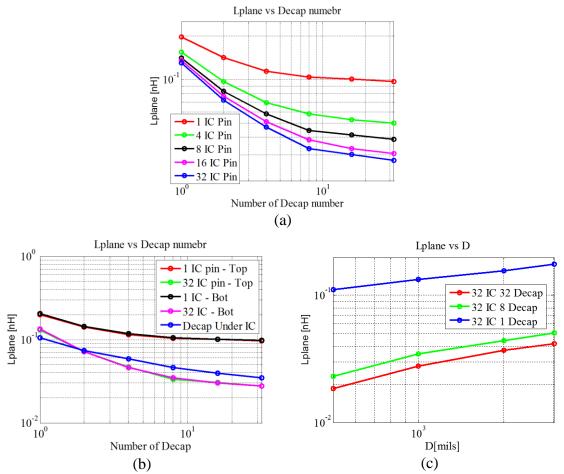

| Figure 5.5. L <sub>PCB_Decap</sub> change vs the number of decaps. By adding more decaps, the L <sub>PCB_Decap</sub> reduces and converges to one number, (a) The convergence rate of L <sub>PCB_Decap</sub> is a straight line in loglog scale plot, (b) The convergence of L <sub>PCB_Decap</sub> is clearly shown in linear scale plot.                                                                                         | 35 |

| Figure 5.6. The definition of the vias in one pair decoupling capacitors placement patterns.                                                                                                                                                                                                                                                                                                                                       | 36 |

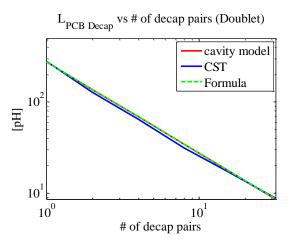

| Figure 5.7. Formulation validation for three decap placement patterns shown in Figure 5.1.                                                                                                                                                                                                                                                                                                                                         | 38 |

| Figure 5.8. Stack up details of the test cases with decoupling capacitors added in pairs incrementally.                                                                                                                                                                                                                                                                                                                            | 41 |

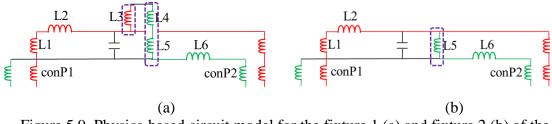

| Figure 5.9. Physics-based circuit model for the fixture 1 (a) and fixture 2 (b) of the measurement test cases.                                                                                                                                                                                                                                                                                                                     | 41 |

| Figure 5.10. The comparison of L <sub>PCB_Decap</sub> from cavity model, formulas, CST and measurement for doublet layout of size 0402.                                                                                                                                                                                                                                                                                            | 41 |

| Figure 6.1. L <sub>PCB_Plane</sub> (a) stack-up extraction, current path, and equivalent circuit model from the cavity model for decap placed (b) on the top layer, (c) on the bottom layer away from the IC, (d) on the bottom layer under the IC                                                                                                                                                                                 | 44 |

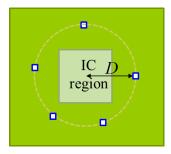

| Figure 6.2. The top view of the decap and IC locations for the L <sub>PCB_Plane</sub> analysis, (a) decap pairs are placed in a circle with the distance D to the IC region, (b) decap pairs are placed in a line with the distance D to the IC region    | 45 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 6.3. The L <sub>PCB_Plane</sub> change with (a) the number of decaps and different numbers of IC pins, (b) decap locations, (c) decap to IC distance                                                                                               | 45 |

| Figure 6.4. The physics-based circuit model of L <sub>PCB_Plane</sub> for the stack-up shown in Figure 6.1 (a) from PPP.                                                                                                                                  | 46 |

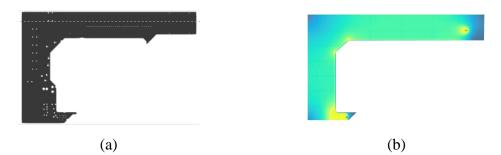

| Figure 6.5. (a). An irregular power net area fill shape from a real design, (b) the current distribution calculation based on PPP for the power net area fill shown in (a), (c) the physics-based circuit model for L <sub>PCB_Plane</sub> from PPP. [29] | 46 |

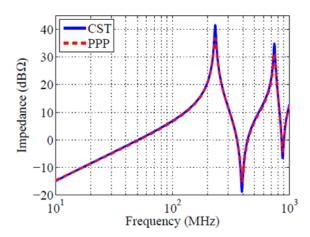

| Figure 6.6. PDN input impedance for the L <sub>PCB_Plane</sub> results comparison from PPP and CST [29]                                                                                                                                                   | 47 |

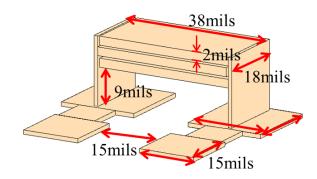

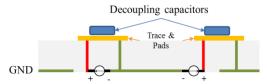

| Figure 7.1. The simplified 3 layer 0402 capacitor model with traces and pads. [25]                                                                                                                                                                        | 48 |

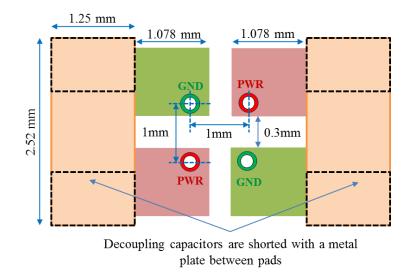

| Figure 7.2. Top view of the doublet decoupling capacitors connection method. The capacitor was modeled as a metal plate [25]                                                                                                                              | 49 |

| Figure 7.3. Side view of doublet decoupling capacitors connection method [25]                                                                                                                                                                             | 50 |

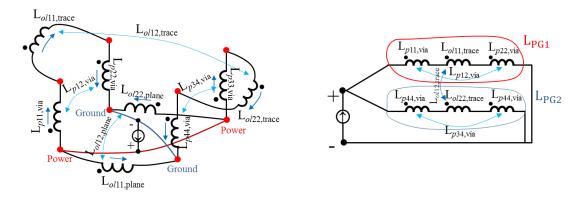

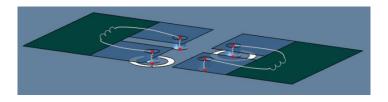

| Figure 7.4. (a) Reduced equivalent circuit for the doublet design, (b) Circuit diagram for the doublet design [25].                                                                                                                                       | 50 |

| Figure 7.5. Equivalent model imposed on the doublet geometry [25]                                                                                                                                                                                         | 50 |

| Figure 7.6. (a) Side view from the decap to PCB, (b) L <sub>above</sub> model used in the pre-<br>layout methodology.                                                                                                                                     | 52 |

| Figure 8.1. The physics-based circuit model with four parts assembled together for the geometry shown in Figure 3.6                                                                                                                                       | 53 |

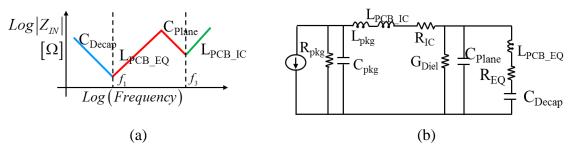

| Figure 9.1. (a) A generic response for a PCB-PDN, (b) behavior model based on the physics-based circuit model from Figure 8.1. [16]                                                                                                                       | 54 |

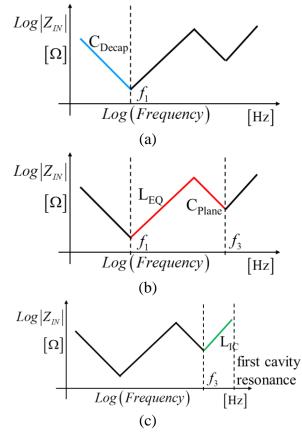

| Figure 9.2. Frequency segmentation of Z-parameter (a).Z1(0~f1), (b). Z2(f1~f3), (c). Z3(f3~first cavity resonance). [16]                                                                                                                                  | 56 |

| Figure 9.3. Equivalent circuit for frequency range 0~f1[16]                                                                                                                                                                                               | 57 |

| Figure 9.4. Equivalent circuit for frequency range f1~f3 [16]                                                                                                                                                                                             | 58 |

| Figure 9.5. Equivalent circuit for frequency range f <sub>3</sub> ~first cavity resonance frequency [16].                                                                                                                                                 | 58 |

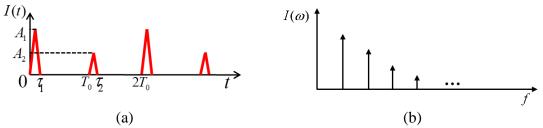

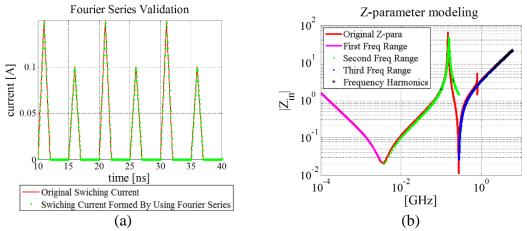

| Figure 9.6. Switching Current Profile in (a) Time domain, (b) Frequency domain. [16]                                                                                                                                                                      | 60 |

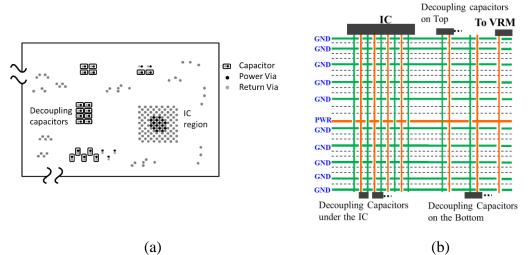

| Figure 9.7. Real high layer PCB board geometry (a). Top view of the board, (b). The stack up of the board with many decoupling capacitors placed on the top layer around the IC, bottom of the IC and on the bottom layer but away from the IC. [20]      | 67 |

| [ <sup>2</sup> ]                                                                                                                                                                                                                                          | 04 |

| Figure 9.8. (a) Compare signal formed by Fourier series with the original signal [10], |      |

|----------------------------------------------------------------------------------------|------|

| (b) Equivalent circuit validation for every frequency range. [16]                      | . 62 |

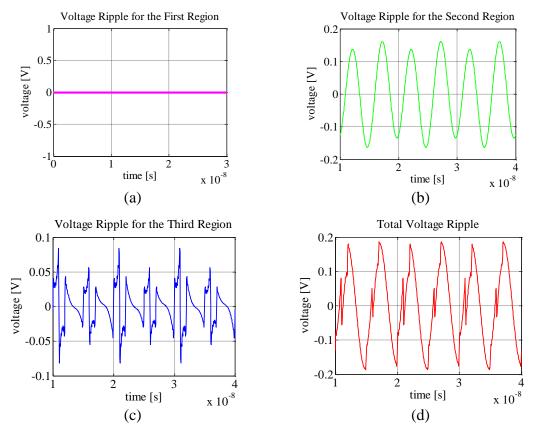

| Figure 9.9. Voltage ripple in time domain for (a) frequency 0~f1; (b) f1~f3; (3)       |      |

# LIST OF TABLES

| Table 5.1. Relative via locations and package size ([mils]) of the three decoupling capacitor placement patterns                   | . 31 |

|------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 5.2. The L <sub>PCB_Decap</sub> of one decap pair for the three 0201 decap packages                                          | . 38 |

| Table 5.3. The self and mutual inductances in the one decap pair for the three decap packages in size 0201                         | . 39 |

| Table 5.4. The L <sub>PCB_Decap</sub> [pH] per mil of one decap pair for the three decap packages of different sizes               | . 39 |

| Table 7.1. Comparison of macromodel inductances of 0402 capacitor model [25]                                                       | . 48 |

| Table 7.2. Self and mutual open loop inductances of the simplified circuit obtained using PMSR method for the doublet design [25]. | . 50 |

| Table 7.3. Labove equivalent inductance for the doublet design [25]                                                                | . 51 |

| Table 7.4. Decoupling capacitor of sizes 0805/0603/0402 for Labove design space                                                    | . 51 |

| Table 7.5. Labove [pH] for doublet layout with 0805/0603/0402 sizes                                                                | . 52 |

#### **1. INTRODUCTION**

Printed circuit board (PCB) power distribution network (PDN) design forms a critical part of system design for the high speed digital systems. PDN is used to deliver power to integrated circuits (ICs). A PDN design in a system often consists of multiple power/power-return planes, vias, and decoupling capacitors on printed circuit board (PCB). For high speed digital system, multiple DC supplies are commonly used in the system, resulting in complicated interconnections of DC supplies. Therefore, the PCBs in these systems require many routing and power/ground layers, often exceeding 20-30 layers. And at the same time, the PCBs function at higher frequencies and the components are placed more densely, which increases the interference between the components and makes the system more sensitive to the electromagnetic interference (EMI) problems and signal integrity (SI) problems which occur in these high-speed digital designs. Also, the maximum voltage ripple specifications become lower as the decrease of the power supply. Designing a good PCB PDN geometry is more critical and challenging in high speed digital system design.

EMI and SI problems of a PDN design come from different aspects [1]-[7]. For a system, switching current of ICs from power to power return (often denoted "ground" in designs) gives rise to significant noise in the supply voltage [8]-[9]. The voltage ripple of one DC supply can easily couple to other DC supplies, causing the voltage ripple on the other power nets. Also, the voltage ripple can couple to the nearby signals, which may be amplified later, and cause noise on IOs or disturb the functionalities of the signals. Another problem caused by voltage ripple is radiation. Electromagnetic field lines bend at the edge of the PCB, which causes radiation to space around the edge. Electromagnetic field lines also bend at the discontinuities on the boards, like vias, connectors, and IC packages, leading to reflection and radiation. Voltage ripple can enhance the radiation by coupling to radiating structures like the heat sinks, connector shields, cables, etc. Voltage ripple enhances the radiation to spread energy in the space, which increases the power consumption in a system.

The PDN performance is often analyzed based on the input impedance looking into the PCB from the IC, which is called PDN input impedance. The input impedance is compared to the target impedance to evaluate the PDN design. Target impedance is selected as the impedance profile which generates the maximum voltage ripple within tolerance [10].

When designing a PCB PDN, engineers would follow some guidelines from experience or 'rules of thumb'. Most of the guidelines come from two-layer or four-layer board analysis, and are not applicable to high-layer PCB PDN structures. While there are commercially available tools [11]-[13] and numerical algorithms [14]-[15] that provide post-layout analysis based on the geometry, like Altium Designer and Cadence Allegro. These tools contain lots of constraints to help designers avoid mistakes and achieve a better PCB layout design. However, most of the layout constraints come from experience based on four-layer or six-layer board analysis. And they can't analyze the performance of the PCB design by running an EM analysis to identify the EMC/EMI or SI problems by itself. More importantly, the results from the post layout simulation tools are not so easily correlate directly with the geometry details in the design. In most design scenarios, the designers have to run multiple simulations or perform large amount of measurements to test the how the performance of the PCB PDN is related to the geometry, and adjust the design incrementally. However, the process is time consuming due to the long simulation time and complexity of the geometries to adjust the geometry details and there is no systematic way of guiding the process.

For higher layer counted PCB PDN, many more decisions has to be made to meet the target impedance specifications, as stack-up, IC pin placement patterns, decap locations, etc. These geometry details have impacts on the equivalent inductance and IC interconnection inductance. For PCB PDN geometry, the impedance profile follows a generic trend as it is dominated by particular geometry details in different frequency range [16]. There are two important features in the PDN impedance profile. The middle frequency range impedance profile is dominated by the current path from the IC to the decaps through the power net area fill and back to the IC, and the higher frequency range impedance profile is dominated by the current path from the IC to the power net are fill and back to the IC [17].

Decoupling capacitors, referred as "decaps" in this paper for convenience, are used to reduce the PDN input impedance by providing sufficient charges to satisfy the current draw requirements of the IC. The decap placement details leave footprints in the PDN input impedance in the mid-frequency range. Adding decaps can lower the input impedance in this frequency range. The minimum values of the impedance in the frequency range is limited by the IC pin connection inductance. A pre-layout design methodology is developed based on the two current paths. The PCB PDN structures are segmented into four parts and every part is modelled using different methodologies based on the geometric characters of the part. With the switching current profile, the time domain voltage ripple is calculated based on the physics-based circuit model. In the end, all parts in the PCB PDN geometry are combined and a pre-layout methodology is proposed.

The pre-layout methodology which quantitatively reveals the connection between the PDN performance and geometry details is proposed in this thesis. The methodology enables designers to have a detailed and complete understanding of the influence of the geometries details before the layout, which can be used as guidelines during the design process.

#### 2. PHYSICS BASED METHODOLOGY FOR PCB PDN

The input impedance is modeled based on the physics based equivalent circuits extracted from different methods, due to the geometric details of different structures in the PCB PDN geometry. The basic structure of a PCB PDN geometry is a single cavity formed by two parallel plates. There are two methods used in the thesis based on the shape of the cavity, the cavity model [18] [19] and parallel plate PEEC (PPP) [21]-[24], PPP is able to extract the circuit model for irregular power shape, while the cavity model is applied to rectangular cavity. Apart from the cavities in the PCB PDN geometry, decoupling capacitors are used to lower the PDN input impedance to meet the target impedance. In this thesis, decoupling capacitors are referred as 'decaps' for convenience. However, decaps are not simple capacitances which can be attached to the PCB directly. Pads and traces are used to provide the connection from decaps to the PCB. Also, the decaps have parasitic parameters, but the ESL and ESR values are not sufficient to provide the information to approximate the influence of the decap parasitics on the PDN performance. The model for the connection from the top ground layer to the decaps is referred as L<sub>above</sub>, which is modelled based on PEEC.

#### 2.1. CIRCUIT EXTRACTION FORM CAVITY MODEL

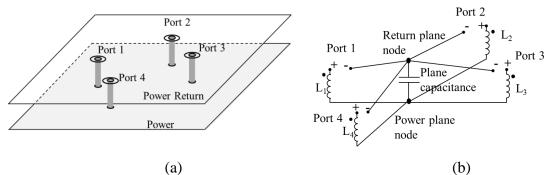

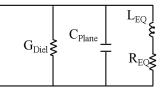

Two thin metal layers separated by a small distance form a cavity. The distance between the two layers needs to be electric small. The cavity geometry is modeled as planar circuit based on the cavity model [1][18]-[20]. Due to the assumptions on the geometry, electromagnetic principles are used to build a model, which is called the cavity model, to characterize the electric and magnetic fields inside the cavity. Figure 2.1 shows the one cavity with four vias and the equivalent circuit model for this geometry with four vias being set as ports. The circuit model is based on the transfer impedance between the vias of rectangular cavity from the cavity model. The via and the plane around it in the cavity is represented as an inductor. The cavity capacitance is calculated as plane-pair capacitance. For multi-layered PCB PDN geometries, the circuit modelling rule can be extended to include the vias and cavities in the physics-based circuit model.

Figure 2.1. (a) An open plane-pair cavity with four vias; (b). The equivalent circuit mode based on the cavity model in [17];

The formulation for component values in the equivalent circuit is explained below [17][18]. The impedance looking into a via i in a rectangular cavity when the source is placed at via j can be written as,

$$Z_{ij} = \frac{1}{j\omega C_{n}} + j\omega L_{ij}(\omega)$$

(1)

where,  $C_p$  is a parallel plate capacitance for the first cavity mode with (m, n) = (0, 0) given by

$$C_{p} = \varepsilon \frac{ab}{d}$$

(2)

and the inductance is found using,

$$L_{ij} = \frac{\mu d}{ab} \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} \frac{(2 - \delta_m)(2 - \delta_n)}{k_{mn}^2 - k^2} g_{mni} g_{mnj} \bigg|_{(m,n) \neq (0,0)}$$

(3)

where,

$$k_{mn}^{2} = \left(\frac{m\pi}{a}\right)^{2} + \left(\frac{n\pi}{b}\right)^{2} , \quad k^{2} = \omega^{2} \mu \varepsilon \text{, and}$$

$$g_{mni} = \cos\left(\frac{m\pi x_{i}}{a}\right) \cos\left(\frac{m\pi y_{i}}{b}\right) \operatorname{sinc}\left(\frac{m\pi W_{xi}}{2a}\right) \operatorname{sinc}\left(\frac{m\pi W_{yi}}{2b}\right).$$

(4)

Here, a, b, and d: Dimensions of cavity along the x, y, and z directions, respectively,  $(x_i,y_i)$ : Location of the i<sup>th</sup> port,

W<sub>xi</sub>, and W<sub>yi</sub>: i<sup>th</sup> Port dimensions along the x and y directions, respectively,

m, and n : Cavity mode indices in the x and y directions, respectively,

$\mu$ : permeability of the dielectric layer, and

$\varepsilon$ : permittivity of the dielectric layer.

$\delta_m$  and  $\delta_n$ : the Keronechker delta function.

The extracted inductance used in the model should be frequency dependence. But, it is found that the inductance value is relatively constant till 60% of the first cavity resonance frequency [18]. For low frequency approximation, it is acceptable to use a single inductance value at DC to find its contribution of the cavity impedance. The infinite summation can be truncated in practice as soon as target convergence is achieved. For the test structure used herein, the mode number m=n=800 is necessary to reach the target convergence within 5% [19].

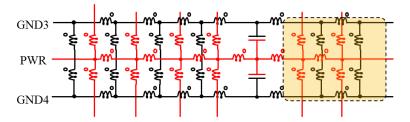

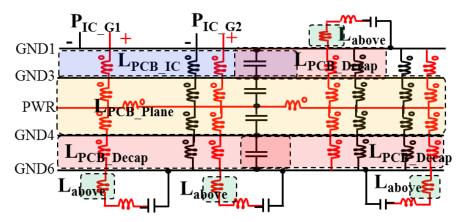

For multi-layer PCB PDN geometry, the circuit can be built the same way as the single cavity for every cavity. And the equivalent circuit models for all cavities can be assembled together to form the equivalent circuit model for the entire geometry. An example of multilayer planes with the connection of multiple power/ground vias between IC and decoupling capacitors is illustrated in Figure 2.2 (a). Its's one-to-one corresponding circuit model is shown in Figure 2.2 (b), where the capacitance and inductances for a plane pair calculated from (2) are connected in series with those for other plane pairs at the location of vias

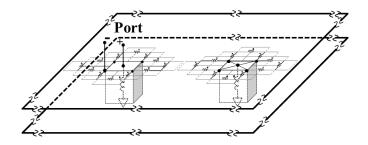

#### 2.2. . PARALLEL-PLATE PEEC

The partial element equivalent circuit (PEEC) methodology was proposed in [21]-[24], and has been developed into a mature modelling strategy. The key idea behind this approach is to divide the geometry into electrically small cells, which can be modelled with lumped circuits due to very small functional variation of field quantities along the cells. For different field components, there may be different types of cells as long as the nodes from different types of cells coincide to allow forcing voltage and current continuity at these nodes. An application of this methodology to the parallel plane structure in PCB stack-up, called plane-pair PEEC (PPP), where the planes were assumed to be thin metal sheets with equal and opposite currents on the top and bottom conductors. Orthogonal mesh cells are applied to both planes to form cell pairs which take advantage of the fast decay in the inductive coupling between the different elements [24]. Figure 2.3 shows the mesh for vias in a single cavity geometry by using the PPP approach.

Figure 2.2. (a) A multilayer power/ground structure with multiple via connections, and, (b) its corresponding circuit model from the cavity model.

Figure 2.3. The mesh used around the vias in one cavity for the inductance calculation based on PPP.

The geometry of two vias in one cavity is modelled using parallel-plate PEEC method, and the mesh used for the inductance calculation is shown around the vias in Figure 2.3. This method can be used to develop an equivalent circuit of the entire plane, and the voltage and current can be solved using the modified nodal analysis (MNA). The inductance sub-circuit is solved separately to find the equivalent inductance for a set of power vias and a set of shorting or return vias. The basic idea of partial element equivalent circuit (PEEC) methodology proposed in [21] is to divide the geometry into numerous electrically small cells, along which the field variation is very small. In these cells, the geometry can be modelled with lumped circuits. The circuit elements in the cells need to maintain the voltage and current continuity at the nodes.

The PPP approach converts electromagnetic problems into circuit problems, which can be solved in an efficient way, while maintain the accuracy. The speed and accuracy of PPP approach were discussed in [21] and [24]. The inductance term of every cell can be represented with partial self-inductance and partial mutual inductance. The plane capacitance model in (5) is applied to calculate the capacitance of the cells.

$$C_{p} = \frac{\varepsilon A}{d}, \qquad (5)$$

Where A is the cell area at each node, and d is the separation of the planes. The resistance of the plane is written as (6).

$$R_c = 2 \frac{\Delta x}{\sigma \Delta y \delta},\tag{6}$$

Here  $\sigma$  is the conductivity of the planes,  $\Delta x$  and  $\Delta y$  are the dimensions for the cell in the perpendicular direction which is parallel to the current directions. It assumes that skin-depth  $\delta = \frac{1}{\sqrt{\pi f \mu \sigma}}$  is smaller than conductor thickness.

An equivalent circuit of the entire plane can be developed using the modified nodal analysis (MNA) method. By applying Kirchhoff's voltage (KVL) and current laws (KCL), the circuit equation can be written as (7).

$$\begin{pmatrix} \overline{c} & \overline{A} \\ \overline{C} & \overline{A} \\ \overline{A^{T}} & \overline{L+R} \end{pmatrix} \begin{pmatrix} \overline{v} \\ \overline{c} \\ \overline{I} \end{pmatrix} = \begin{pmatrix} \overline{I} \\ \overline{c} \\ \overline{c} \\ 0 \end{pmatrix},$$

(7)

Where,  $\overline{A}$  is the incident matrix which stores all the connection information,  $\overline{I}_{i}$  is the external current source,  $\overline{L}$  is partial inductance matrix,  $\overline{R}$  is resistance matrix, and  $\overline{c}$  is capacitance matrix. The current  $\overline{I}$  and voltage  $\overline{V}$  at the notes can be calculated by solving the circuit equations. Then the current density of the planes is written as (8).

$$=_{J}^{=}\frac{\bar{I}}{w},$$

(8)

Here w is the mesh cell dimension.

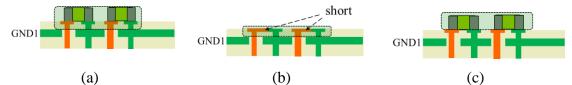

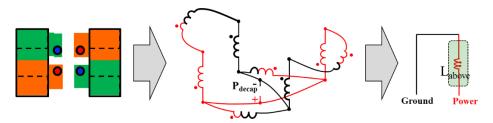

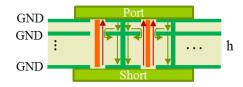

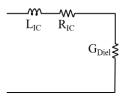

#### 2.3. PMSR FOR DECAP CONNECTION MODELING

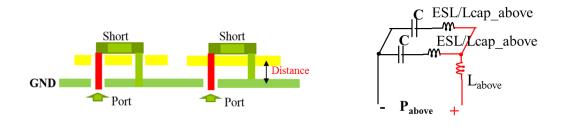

The Physics-based Model Size Reduction (PMSR) method is used to model the decap connection from the decap to the PCB using traces, pads, and vias above the top most or bottom most power-return planes [25]-[26]. A relatively simple circuit which correlates with the geometry is reduced from the conventional PEEC model based on PMSR. Nodes are selected from the complex PEEC model to be the final nodes after the reduction according to the geometry details. The original circuit model from the PEEC between the nodes is used to extract lumped RLGC elements for PMSR. Then all reduced circuit models are assembled again based on the node connectivity matrix from the

geometry. KCL and KVL principles are applied to the reduced equivalent circuit models. Due to the efficiency and accuracy of the PEEC till relatively high frequency, the PMSR method maintains the accuracy and efficiency, while implementing the geometry influence in the calculation.

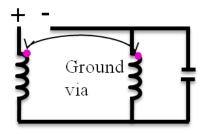

The connection from the decap to the PCB is separated into two parts. One part is the inductance from the decap pads to the ground layer of the PCB when the decaps are shorted, as shown in Figure 2.4 (b). The other one is the decap itself, as shown in Figure 2.4 (c). The inductance from the decap pad to the PCB is denoted asd  $L_{above}$ , and PMSR is applied to obtain the physics-based circuit model. For the decap itself, usually the ESL and ESR values provided by the vendors are not adequate for accurate modeling. The decap model itself can be modeled based on PEEC, as in [25].The physics based circuit model extraction process of  $L_{above}$  for the geometry with two decaps placed in pairs in can be extracted as Figure 2.5.

Figure 2.4. Decap connection above the PCB separation, (a) Decap connection definition, (b) Labove when the decaps are shorted, (c) Decap part in the decap conection.

Figure 2.5. The physics-based circuit model extraction based on the PMSR.

#### **3. PCB PDN DESIGN CRITERIA**

#### **3.1. GENERIC PCB PDN INPUT IMPEDANCE**

The PDN input impedance looking from the IC has a generic trend with frequency, as different geometry structures dominate in different frequency ranges. At relatively low frequency, the PDN input impedance is dominated by the decap capacitance, and the input impedance reduces with the frequency increasing. In this frequency range, the current comes from the IC port, goes to the power net area fill, passes the power net area fill and reaches the decaps. After passing the decaps, the current goes back to the power net area fill and then to the IC power-return. The equivalent inductance of the current path is defined as L<sub>PCB EQ</sub> in the thesis. As the frequency increases, the capacitance between the power net area fill with its neighboring power-return net starts to dominate the PDN input impedance. The plane capacitance calculated from (2) for rectangular power/power-return cavity, enables the current to come directly back to the IC power-return after reaching the power net area fill. The equivalent inductance of the current path from the IC to the power net are fill and back to the IC directly without reaching the decaps is defined as IC interconnection inductance  $L_{PCB IC}$ . At high frequencies, the  $L_{PCB IC}$  dominates the PDN input impedance. As frequency grows even higher, the cavity resonances start, and the cavity can't model PDN performance after cavity resonance.

The equivalent inductance  $L_{PCB_EQ}$  can be segmented into different parts, the decap interconnection inductance  $L_{PCB_Decap}$  of the current path from the power net area fill to the decap and back to the power net area fill, the IC interconnection inductance  $L_{PCB_IC}$ , the power net area fill inductance  $L_{PCB_Plane}$  of the current path from IC region in the power net area fill to the decap region and back to the IC region, and the decap connection inductance  $L_{above}$  from the decap to the PCB. The segmentation is explained in details in 3.4.

#### **3.2. TARGET INPUT IMPEDANCE DEFINITION**

PCB PDN design is mostly evaluated based on the input impedance looking into the PCB from the IC. The PDN input impedance is compared with the target impedance, which is selected as the impedance profile that generates the maximum voltage ripple within tolerance [10]. The definition of target impedance is based on the switching current profile. Intuitively, the target impedance can be defined as

$$Z_{\text{target}} = \frac{V_{\text{supply}} \times Percentage_{Specified}}{I_{switching}} \tag{9}$$

In this definition, the voltage ripple and switching current both change with time. But the target impedance is frequency domain concept. To resolve the problem, the maximum values of voltage and current are used in this definition. Then the target impedance is a constant through the entire frequency range, which is resistance. However, the PDN input impedance is frequency dependent, as shown in Figure 3.1. The requirement of lowering the PDN input impedance to a constant value through the entire the frequency range can lead to over-design in practice [10].

Figure 3.1. The generic PCB PDN input impedance. By adding decoupling capacitors, the mid frequency range inductance reduces.

The target impedance should be defined in a way which is related to the switching current profile in frequency domain. Usually IC has two modes, working and resting. In a PDN design, the number of ICs which switch varies with time. The switching current profile can be complex. For a simple approximation, the switching current can be modeled as the summation of triangle waves of different frequencies. The magnitudes of the frequency harmonics of the triangle waves decrease with the increase of the frequency. Then, the target impedance definition increases at higher frequencies. The target impedance can be defined as (10), [10]. The PDN input impedance and the target impedance is shown in Figure 3.1.

$$Z(f)_{\text{target}} = R + j\omega L \tag{10}$$

#### **3.3. SURFACE CURRENT ANALYSIS**

Surface current distribution for PCB PDN is closely related to the geometry. However, the discontinuity caused by vias changes the current distribution. Surface current distribution reveals the current path and the strength of the coupling between geometry structures. The current density distribution can be calculated based on the cavity model [19] and plane-pair PEEC [24].

In the cavity, the surface current distribution on the planes can be analyzed from the field distribution. The thickness of the cavity is electric small, the electric field inside the cavity only has  $\hat{z}$  component, which is listed below.

$$E_{z}(x,y)\Big|_{J=J_{j}} = j\omega\mu(\hat{J}_{j}\cdot\hat{z})\frac{1}{ab}\sum_{m}\sum_{n}\frac{(2-\delta_{m})(2-\delta_{n})}{(k_{x})(k_{y})}\frac{\left[\cos(k_{x}x)\cos(k_{y}y)\cos(k_{x}x_{j})\cdot\right]}{k^{2}-[(k_{x})^{2}+(k_{y})^{2}]} \quad (11)$$

Magnetic field can be calculated based on the electric field using Maxwell's equation as (12), [27].

$$\vec{H} = \frac{j}{\omega\mu} \nabla \times \vec{E} = \frac{j}{\omega\mu} \left[ \left( -\frac{\partial E_z}{\partial x} \right) \hat{y} + \frac{\partial E_z}{\partial y} \hat{x} \right]$$

$$= \frac{(\hat{J}_j \cdot \hat{z})}{ab} \left[ \sum_{m} \sum_{n} \frac{(2 - \delta_m)(2 - \delta_n)}{(k_x)(k_y)} \frac{\cos(k_y y_j)\sin(\frac{k_x W_{xj}}{2})\sin(\frac{k_y W_{yj}}{2})}{k^2 - [(k_x)^2 + (k_y)^2]} \hat{x} - \left[ \sum_{m} \sum_{n} \frac{4\sigma_m^2 \sigma_n^2}{(k_x)(k_y)} \frac{\cos(k_y y_j)\sin(\frac{k_x W_{xj}}{2})\sin(\frac{k_y W_{yj}}{2})}{k^2 - [(k_x)^2 + (k_y)^2]} \hat{y} \right] \right]$$

$$(12)$$

Then, surface current density can be represented as (13), [27].

$$\vec{J}(x_{i}, y_{i})\Big|_{J=J_{j}} = \frac{\hat{J}_{j}}{ab} \begin{bmatrix} \sum_{m} \sum_{n} \frac{(2-\delta_{m})(2-\delta_{n})}{(k_{x})(k_{y})} \frac{k_{y}f_{1}(x_{i}, y_{i}, x_{j}, y_{j})}{k^{2}-k_{mn}^{2}} \hat{y} + \\ \sum_{m} \sum_{n} \frac{(2-\delta_{m})(2-\delta_{n})}{(k_{x})(k_{y})} \frac{k_{x}f_{2}(x_{i}, y_{i}, x_{j}, y_{j})}{k^{2}-k_{mn}^{2}} \hat{x} \end{bmatrix}$$

(13)

Here,

$$k_{x} = \frac{m\pi}{a}, \quad k_{y} = \frac{n\pi}{b}, \quad k_{mn}^{2} = \left(\frac{m\pi}{a}\right)^{2} + \left(\frac{n\pi}{b}\right)^{2}, \quad k^{2} = \omega^{2}\mu\varepsilon \quad \text{,and}$$

$$f_{1}(x_{i}, y_{i}, x_{j}, y_{j}) = \cos(k_{x}x)\sin(k_{y}y)\cos(k_{x}x_{j})$$

$$\times \cos(k_{y}y_{j})\sin(\frac{k_{x}W_{xj}}{2})\sin(\frac{k_{y}W_{yj}}{2}), \quad (14)$$

$$f_{2}(x_{i}, y_{i}, x_{j}, y_{j}) = \sin(k_{x}x)\cos(k_{y}y)\cos(k_{x}x_{j})$$

$$\times \cos(k_{y}y_{j})\sin(\frac{k_{x}W_{xj}}{2})\sin(\frac{k_{y}W_{yj}}{2}).$$

**3.3.1. Test Geometry for Current Density Distribution.** The physics behind the segmentation of the geometry is based on the current paths in the PCB PDN. The current distribution along the planes of the geometry gives more intuitive understanding of how the geometry influences the mutual inductance between the vias in the cavity. A single rectangular cavity formed by a power layer and a power-return layer with a power via and a shorting power-return via is used as the test geometry to illustrate the coupling mechanism in different situations [27], as shown in Figure 3.2. One of the via is defined as a port and the other via is shorted to both plates of the cavity. The comparison is designed to show how the distance of the vias influence the coupling between them. The two vias are placed close (5mm) in one case, and are placed far away (25mm) in another case. The circuit model for the geometry is shown in Figure 3.3, with the values of self and mutual inductance for the different cases. The surface current density for the cases in Figure 3.3 is shown in Figure 3.4.

To calculate the surface current density  $J_{ij}$ , the plane is meshed into many sample points. The simplest mesh is uniform mesh, but it will take large number of mesh cells to

get relative accurate results. To reduce the number of samples while maintain the accuracy, sub-mesh is used at the discontinuities where the surface current changes a lot to capture the variations. In this case, denser mesh is applied around the via regions.

Figure 3.2. A plane-pair cavity with a power via and a shorting ground via placed with distance d, (a) top view of the test case, (b) stack-up of the test case. [27]

Figure 3.3. Circuit model for geometries shown in Figure 3.2.

Figure 3.4. Current density plot based on the cavity model for the geometry shown in Figure 3.2 with different d values, (a) d=5mm, (b) d=25mm. [27]

The current density distributions based on the cavity model for the two cases are shown in Figure 3.4. When the two vias placed closely, the current concentrates around the vias as shown in Figure 3.4 (a). When the two vias are placed far away, the current spreads to much larger area as shown in Figure 3.4 (b).

**3.3.2.** Current Distribution Comparison between the Cavity Model and Plane-Pair PEEC. The surface density distribution for the case with d=25mm based on the planepair PEEC is calculated and compared with the result based on the cavity model as shown in Figure 3.5. The results obtained from the two methods are identical, but the magnitude contour from the plane-pair PEEC provides more details than the one from the cavity model in the outside region. For the area near the vias, the contour shapes are different for the two methods, while the magnitudes are similar.

Figure 3.5. Current density comparison around the vias between cavity model and PP-PEEC for the geometry shown in Figure 3.2 for d=25mm, (a). the via region, (b).zoom-in region for the via center shown in (a). [27]

**3.3.3** Current Distributions in the PCB PDN Structures. These two cases of current distribution describes the current distribution in the IC/decap interconnection region and the power net area fill part respectively. As shown in Figure 3.4, when the two vias are placed closely, the shorting via provides the return path nearby. The surface current distribution is independent from the plane shape. In the IC or decap interconnection part, the power-return vias are close to the power vias, and the current concentrates around the

area, as the return path is nearby. Also, decaps are usually places at the leftover regions after the routing during the layout process, the distance from the decap to the IC ports are relatively larger than the distance from the power vias to the power-return vias in the decaps. The mutual inductances between the power vias and power-return vias of the IC and decap regions are negligible. The assumption that there is little or no mutual coupling between LPCB\_IC and LPCB\_Decap holds in most cases. When the two vias are placed far away, the surface current spreads along the planes and the inductance calculation is shape dependent when the vias are placed close to the edge. In the power net area fill, the current has to cross the planes from the corresponding IC region to the corresponding decap region in the part. The current path in Figure 3.4 (b) illustrates the current distribution in the power net area fill. The current distribution is strongly dependent on the power net area fill are usually cut into pieces with many voids embedded inside. The irregular shapes and the voids in the power net area fill can increase the LPCB\_Plane dramatically.

Thus in the PDN designs with power and power-return vias placed at large distance, which is comparable to the distance from the edge, the power plane shape matters [28]. If there are enough return vias placed nearby the power vias, the current path is much less dependent on the plane shape. In most PCB PDN geometry, the power area fills can be irregular shaped. If the power shape doesn't influence the current path, the calculation of the cavity model can still be applied to calculate the equivalent inductance of the current path passing the power shapes. For the cases where the power shapes influence the current path, the PPP can be applied to calculate the inductance.

When the return vias are placed closely, the current concentrates in the nearby area. The mutual inductance terms are influenced by the distance. This fact can be used to measure when to ignore or include the mutual terms between IC and decap vias. And due to the fact of the concentration of the current distribution when the vias are place closely, the decap connection inductance and the IC connection inductance path can be segmented separately, without considering the mutual inductance between them.

#### **3.4. GEOMETRY SEGMENTATION**

The two features,  $L_{PCB_EQ}$  and  $L_{PCB_IC}$  in the PCB PDN input impedance are critical to the PCB PDN design. Decaps are used in the PCB PDN design to provide enough charges and lower the PDN input impedance. It is observed that  $L_{PCB_IC}$  can be reduced by adding more decaps. For the current path of  $L_{PCB_EQ}$ , there are four inductance contribution portions which can be segmented, which are the IC interconnection inductance  $L_{PCB_IC}$ , decap interconnection inductance  $L_{PCB_Decap}$ , the inductance of the current crossing the power net area fill  $L_{PCB_Plane}$ , and the decap connection inductance from decap to the PCB  $L_{above}$ . The segmentation is based on the assumption that there is no or little coupling between each block. Under this assumption, every block can be modeled individually. The the  $L_{PCB_EQ}$  can be expressed as the summation of the four parts, as in (15). A general PDN stack-up with many decaps placed on the top layer, the bottom layer away from the IC and the bottom layer under the IC is shown in Figure 3.6. The segmentation of every part is defined in the figure.

$$L_{PCB\_EQ} = L_{PCB\_Decap} + L_{PCB\_IC} + L_{PCB\_Plane} + L_{above}$$

(15)

In the IC and decap regions, the power vias and ground vias are placed closely. The current concentrates and doesn't cross the power net area fill. In these regions, the mutual inductance between IC and decap regions can be ignored when the distance from the decaps to the IC is large enough.

$L_{PCB\_Decap}$  depends on the decaps to power net area fill distance, the number of decaps , the decap package pattern and placement pattern. The convergence rate of  $L_{PCB\_Decap}$  is influenced by the via placement patterns, pitch distance, package size, etc.

$L_{PCB_IC}$  depends on the IC to the power net area fill distance, the pin placement pattern, the number of the IC pins, and the pitch size of the pins. The convergence rate of  $L_{PCB_IC}$  is influenced by the via placement patterns and the pitch size.

The  $L_{PCB_Plane}$  contains decap part and IC part. Then it depends on all factors related to  $L_{PCB_Decap}$  and  $L_{PCB_IC}$ , including the number of IC pins, IC pin placement patterns, IC pitch, the number of decaps, decap placement patterns and decap pitch. It also depends on the stack-up of the power net area fill, and the distance between the IC and decaps, Compared to  $L_{PCB_IC}$  and  $L_{PCB_Decap}$ ,  $L_{PCB_Plane}$  is more complicated, since the current path in the power net area fill is complex, which will be explained later.

The relation between  $L_{PCB_IC}$  and  $L_{PCB_EQ}$  is based on current path. From experiment results,  $L_{PCB_EQ}$  will convergent to  $L_{PCB_IC}$  by adding decaps.

Figure 3.6. A stack-up of a high-layer count PCB PDN geometry with a power net fill and the definitions of the parts segmented from the PCB PDN geometry. [17]

#### **3.5. EQUIVALENT INDUCTANCE AS CRITERIA**

In PDN input impedance, two inductances, the equivalent inductance  $L_{PCB_EQ}$ , and the IC connection inductance  $L_{PCB_IC}$ , stand out because of different current paths [17]. Adding decaps can reduce the mid-frequency range equivalent inductance  $L_{PCB_EQ}$  to the  $L_{PCB_IC}$ . The convergence criteria of the  $L_{PCB_EQ}$  is defined as the ratio of the difference between  $L_{PCB_EQ}$  and  $L_{PCB_IC}$  to  $L_{PCB_IC}$ . From (15)  $L_{PCB_EQ}$  is the summation of  $L_{PCB_Decap}$ ,  $L_{PCB_Plane}$ ,  $L_{PCB_IC}$  and  $L_{above}$ . Then the convergence criteria can be expressed as ratio of the summation of  $L_{PCB_Decap}$ ,  $L_{PCB_Plane}$  and  $L_{above}$  to the  $L_{PCB_IC}$ . From the cavity model formulation in (3), the inductance contribution is proportional to the cavity thickness. An approximation of the thickness ration of the decap interconnection region, power net area fill and IC interconnection region can be used when the inductance contribution is largely influenced by the thinness. In general PCB PDN stack-up, either the distance from the decap to the power/power-return cavity h<sub>1</sub> or the power/power-return cavity thickness h<sub>2</sub> is much larger than the other, leading to either  $L_{PCB\_Decap}$  or  $L_{PCB\_Plane}$  being the dominant term in  $L_{PCB\_EQ}$ . In this case, the criteria can be evaluated approximatively based on the ratio of the thicknesses with acceptable precision.

#### 4. LPCB\_IC CONVERGENCE

#### 4.1. LPCB\_IC SEGMENTATION IN THE STACK-UP

$L_{PCB_IC}$  is defined as the IC interconnection inductance in the PCB. The current path in the block is from the IC port to the power net area fill and back to the IC port. The principle used to extract the  $L_{PCB_IC}$  from the total equivalent inductance  $L_{PCB_EQ}$  is to maintain the current path to be the same. By applying the principle, the modeling setup to extract  $L_{PCB_IC}$  is to put the port at the IC port, and put shorts at the locations of IC vias on the nearest power-return plane in the power/power-return cavity, as shown in Figure 4.1. In this way, the current path is forced to be the same as that in the definition.

Figure 4.1. IC interconnection inductance extraction in the PCB.

#### **4.2. IC PIN PLACEMENT PATTERNS**

The ICs have lots of power and power-return pins placed with a specific pitch size in a relatively small area. The number of IC power pins and power-return pins is designed by the package or IC designers. There are several common IC pin placement patterns, and three of them, defined as row, regular, and hexagonal, as shown in Figure 4.2, are analyzed in the thesis. The hexagonal placement patterns have different configurations with the different relative locations of the power and power-return vias. The placement patterns of row, regular, and hexagonal has the ratio of power to power-return vias to be 1. The power and power-return vias are placed in alternating way to take advantage of the mutual inductance since the current directions on the power vias and power-return vias are opposite. The power vias in the rectangular placement pattern are surrounded by the power-return vias, which maximize the mutual inductance influence on the IC interconnection inductance. This pattern is seen as another reference in the comparison of L<sub>PCB\_IC</sub> for different placement patterns. The pitch size for the IC vias is 1mm. In the comparison, the 1/n curve, which is the inductance by simply adding the power pins in the layout, is added to show the mutual inductance influence on the  $L_{PCB_IC}$ .

Figure 4.2. Five IC pin placement patterns with different power and power-return relative locations, (a). Row placement pattern with power and power-return vias placed in a row, (b). Regular placement pattern with power and power-return vias placed alternating, (c). Grid placement pattern with the unit cell of one power via surrounded by four power-return vias, (f). Hex placement pattern with power and power-return vias placed alternating in hexagonal pattern, (e) Hex1 placement pattern with another configuration of power and power-return vias as in (d).

**4.2.1. Circuit Reduction and Rigorous L**<sub>PCB\_IC</sub> **Formulation.** From the cavity model, the IC connection part can be modeled as shown in Figure 4.3. In the L<sub>PCB\_IC</sub> calculation, the circuit model can be simplified by combining all power vias into one power via and combining all ground vias into one ground via.

$L_{PCB_IC}$  is simulated based on the circuit model from the cavity model for one cavity. From (3), the inductance is proportional to the cavity thickness. Thus,  $L_{PCB_IC}$  can be scaled to different cavity thickness easily. The cavity thickness used in the model is 30 mils for the results shown in this session.

Figure 4.3 shows the methodology to find  $L_{PCB_IC}$  based on the circuit extracted from the cavity model. The power and ground vias are divided into two groups based on the assumption that the current direction is the same for all the vias in each group. Then, all power vias can be merged into one power via, and all groud vias can be merged into one ground via. The reduction is based on the voltage and current relation, as shown in (16) to (18).

Figure 4.3. The physics-based circuit model reduction for L<sub>PCB\_IC</sub>.

The KVL for each group is expressed as,

$$j\omega \mathbf{L}_{Group}\mathbf{I} = \mathbf{V} \tag{16}$$

where,

$$\mathbf{I} = \begin{bmatrix} I_1 & I_2 & \cdots & I_n \end{bmatrix},$$

$$\mathbf{V} = \begin{bmatrix} V_1 & V_2 & \cdots & V_n \end{bmatrix}$$

(17)

$$\mathbf{L}_{Group} = \begin{bmatrix} L_{11} & L_{12} & \cdots & L_{1n} \\ L_{21} & L_{22} & \cdots & L_{2n} \\ \vdots & \vdots & \ddots & \vdots \\ L_{n1} & L_{n2} & \cdots & L_{nn} \end{bmatrix}$$

(18)

$I_k$  is the current through the k<sup>th</sup> IC power/power-return via in the group, and,

$V_k$  is the voltage across the via looking from the port.

Assuming voltages across the parallel inductors are the same, then by inversing the L matrix, (16) is changed to

$$j\omega \mathbf{I} = \mathbf{L}_{Group}^{-1} \mathbf{V}$$

(19)

Since  $V_1 = V_2 = \cdots = V_n \triangleq V_{Group}$ , by adding  $I_i$ , (19) can be written as

$$j\omega L_{Group} I_{Total} = V_{Decap}$$

(20)

where,

$$I_{Total} = I_1 + I_2 + \dots + I_n$$

(21)

Then, a relationship can be defined between effective inductance  $L_{Group}$  and the inductance matrix, as,

$$L_{Group} = \left(\sum_{columns} \sum_{rows} \left[ \mathbf{L}_{Group} \right]^{-1} \right)^{-1}$$

(22)

Through the procedures, the power via inductors and ground via inductors are merged into one power via inductor and one ground via inductor in series. The  $L_{ij}$  matrix can be written as

$$\mathbf{L}_{PCB_{-}IC} = \begin{bmatrix} L_{PWR} & L_{PWR_{-}GND} \\ L_{PWR_{-}GND} & L_{PWR} \end{bmatrix}$$

(23)

Here  $L_{PWR}$  is the self-inductance of the one power via grouped from all power vias,  $L_{GND}$  is the self-inductance of the one ground via grouped from all ground vias, And  $L_{PWR\_GND}$  is the mutual-inductance between the groud via and the power via. Then  $L_{PCB\_IC}$  can be calculated as

$$L_{PCB\_IC} = L_{PWR} + L_{GND} - 2L_{PWR\_GND}$$

<sup>(24)</sup>

**4.2.2.** LPCB\_IC Simulation Results Comparison. A single cavity with the thickness of 40 mils is used to simulate the  $L_{PCB_IC}$  for the placement patterns shown in Figure 4.2. The  $L_{PCB_IC}$  modelling results comparison is shown in linear and loglog scales in Figure 4.4. 1/n curve is calculated as the first IC pin divided by the number of IC pins, which is the trend if adding the IC pins in parallel without considering the mutual inductances between the vias. Figure 4.4 (a) shows the convergence trend of  $L_{PCB_IC}$  by adding the number of IC pins, and Figure 4.4 (b) shows the convergence rate of  $L_{PCB_IC}$ . From both

comparisons, the  $L_{PCB_IC}$  of the placement patterns shown in Figure 4.4 is very close to 1/n curve with the cavity thickness is 40mils. Since  $L_{PCB_IC}$  is proportional to the cavity thickness, resulting in the difference of  $L_{PCB_IC}$  between different placement patterns increases with the cavity thickness. But 1/n curve is a good approximation for  $L_{PCB_IC}$  with the cavity thickness in the range of 30mils.

Figure 4.4. LPCB\_IC comparison for the IC pin placement patterns shown in Figure 4.2.

# 4.3. UNIT CELL APPROACH FOR LPCB\_IC APPROXIMATION

Unit cell approach can be used to calculate LPCB\_IC for the pattern of one power via surrounded by four power-return vias. The unit cell for the IC placement pattern shown in Figure 4.2 (c) is one power via surrounded by four ground vias. The return current for the power via mostly concentrates on the nearby power-return vias. Thus, the way to construct the  $L_{PCB_IC}$  formula of the pattern is based on adding the unit cell in parallel and using curve fitting to quantize the mutual inductance influence, as shown in(25).

$$L_{PCB\_IC\_grid} = h_1 \left( \frac{L_{self\_PUL,1unitcell}}{n_{ICpin}} + L_{Mutual,unitcell\_PUL} \right)$$

(25)

Here, the first term of (25) can be seen as the self-inductance of the cells, and the second term is the mutual inductance between the cells.

To calculate the first pair connection inductance, KCL and KVL are applied to the unit cell of four vias. In the formulation, the voltages and currents for the four power return vias are assumed to be the same. Figure 4.5 shows the name and location of the vias in the unit cell.

Figure 4.5. Unit cell definition in the IC pin placement pattern and the mutual inductance definitions

$$\begin{bmatrix} L_{P1} & M_{P1G1} & M_{P1G2} & M_{P1G3} & M_{P1G4} \\ M_{P1G1} & L_{G1} & M_{G1G2} & M_{G1G3} & M_{G1G4} \\ M_{P1G2} & M_{G1G2} & L_{G2} & M_{G2G3} & M_{G2G4} \\ M_{P1G3} & M_{G1G3} & M_{G2G3} & L_{G3} & M_{G3G4} \\ M_{P1G4} & M_{G1G4} & M_{G2G4} & M_{G3G4} & L_{G4} \end{bmatrix} \begin{bmatrix} I_{1} \\ I_{2} \\ V_{2} \\ V_{2} \end{bmatrix}$$

(26)

Where,

Assume  $I_2 = I_3 = I_4 = -I_1 / 4, V_{IC} = V_1 - V_2$ ,

$L_{p_i}$  is the self-inductance of the i<sup>th</sup> power via, i=1,

$L_{Gi}$  is the self-inductance of the i<sup>th</sup> power-return via, i=1,2,3,4,

$M_{P_{iGj}}$  is the mutual-inductance of the i<sup>th</sup> power via and j<sup>th</sup> power-return via,

$M_{GiGj}$  is the mutual-inductance of the i<sup>th</sup> power-return via and j<sup>th</sup> power-return via,

$V_i$  and  $I_i$  are the voltage and current for the i<sup>th</sup> via,

$V_{IC}$  is the voltage across the unit cell.

By solving the matrix, the unit cell LPCB\_IC is calculated as

$$L_{self_PUL, lunitcell} = L_{self, PWR} + \frac{L_{self, GND}}{4} - 2M_{PG} + \frac{M_{GG1}}{2} + \frac{M_{GG2}}{4}$$

(27)

Here  $M_{GG1} \triangleq M_{G1G4} = M_{G1G2} = M_{G2G3} = M_{G3G4}$ , and  $M_{GG2} \triangleq M_{G1G3} = M_{G2G4}$ .

Figure 4.6 shows the formulation of  $L_{PCB_IC}$  based on (25). The error introduced by the unit cell approach is not significant. The upper bound of  $L_{PCB_IC}$  is in the row IC pin pattern and the lower bound is in the grid IC pin pattern. During the design of IC interconnection inductance, these two cases can be used to calculate the range of  $L_{PCB_IC}$ . Since for the other cases, the 1/n curve is close to the  $L_{PCB_IC}$  calculated rigorously from the cavity model,  $L_{PCB_IC}$  can be calculated approximately using 1/n curve to calculate the number of IC pins during the design.

Figure 4.6. L<sub>PCB\_IC</sub> formulation validation shown in (25).

# 4.4. SELF AND MUTUAL INDUCTANCE EXTRACTION IN LPCB\_IC