# Scholars' Mine

### **Masters Theses**

Student Theses and Dissertations

Spring 2015

# **ESD** event locator

Syed Abrar Ul Huq

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons Department:

#### **Recommended Citation**

Huq, Syed Abrar Ul, "ESD event locator" (2015). *Masters Theses*. 7400. https://scholarsmine.mst.edu/masters\_theses/7400

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

### ESD EVENT LOCATOR

by

### SYED ABRAR UL HUQ

#### A THESIS

Presented to the Faculty of the Graduate School of the

## MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

## MASTER OF SCIENCE IN COMPUTER ENGINEERING

2015

Approved by

Dr. David J. Pommerenke, Advisor Dr. Yiyu Shi Dr. Daryl G. Beetner

Copyright 2015 SYED ABRAR UL HUQ All Rights Reserved

#### ABSTRACT

Electrostatic Discharge (ESD) presents one of the most common threats to electronic systems especially in the cases of high-speed digital systems. ESD event locator systems have been designed to determine the location of the source of the ESD event using different techniques. One such method of determining the origin of the ESD event, is the use of four antennas and a high-speed Analog to Digital Converter (ADC) system to capture the ESD events.

This thesis presents such an implementation which deals with the design of an analog front-end to a fast TI LM97600 ADC and a Virtex-5 Field-Programmable Gated Array (FPGA) based system to control the ADC and to capture and transfer the sampled data between the FPGA and a Personal Computer (PC). The thesis focuses on specific objectives of the ESD event locator system which include; first, to program the FPGA to capture and acquire data on the high-speed output lanes of the ADC, second to develop a trigger logic to store data only on the occurrence of an ESD event, third to develop robust code to transfer the data from the FPGA to the PC using communication protocols such as Universal Serial Bus (USB).

#### ACKNOWLEDGMENTS

I am extremely thankful to my advisor Dr. David Pommerenke for his constant support and the knowledge imparted by him, which has both helped me in my thesis as well as my own personal development as a student. I have learned innumerous things during my work in the EMC lab as a result of his advice. I would also to like to thank him for supporting my work with graduate research assistantship during my pursuit of my Master's degree.

I would also like to specially thank Dr. Yiyu Shi for recommending me for the research, for his constant guidance and advice on academic matters and also for serving on my research committee. I would also like to thank Dr. Daryl Beetner for his advice and for accepting my request to serve on my research committee.

I would like to thank John Lee from Samsung Electronics Co. Ltd. for his support and guidance in performing the research. I would also like to thank the other faculty members in the EMC lab for their guidance and teaching and for providing an excellent research environment. I would also like to thank my colleagues in the EMC lab for their teamwork and assistance on all aspects of my research work.

Lastly, I'd like to thank my family members for their constant support and encouragement.

## TABLE OF CONTENTS

Page

v

| ABSTRACT iii               |                                |    |  |

|----------------------------|--------------------------------|----|--|

| ACKNOWLEDGMENTS iv         |                                |    |  |

| LIST OF ILLUSTRATIONS viii |                                |    |  |

| LI                         | ST OF TABLES                   | х  |  |

| SE                         | ECTION                         |    |  |

| 1                          | INTRODUCTION                   | 1  |  |

| 2                          | DESIGN CONCEPT                 | 4  |  |

| 3                          | HARDWARE                       | 7  |  |

|                            | 3.1. ANTENNA AND RF BOARD      | 7  |  |

|                            | 3.2. TRIGGER BOARD             | 9  |  |

|                            | 3.3. POWER BOARD               | 14 |  |

|                            | 3.4. MAIN BOARD                | 16 |  |

| 4                          | DATA ACQUISITION               | 22 |  |

|                            | 4.1. OVERVIEW                  | 22 |  |

|                            | 4.2. WV5 DLL                   | 22 |  |

|                            | 4.3. FILES REQUIRED            | 24 |  |

|                            | 4.4. APPLICATION INTERFACING   | 24 |  |

|                            | 4.4.1. Initialization          | 25 |  |

|                            | 4.4.2. Register Initialization | 27 |  |

|   |      | 4.4.3. | Synchronization Request    | 30 |

|---|------|--------|----------------------------|----|

|   |      | 4.4.4. | Channel and Byte Alignment | 31 |

|   |      | 4.4.5. | Data Capture               | 32 |

|   | 4.5. | RESU   | LTS                        | 35 |

| 5 | DAT  | TA STO | PRAGE ON FPGA              | 39 |

|   | 5.1. | OVER   | VIEW                       | 39 |

|   | 5.2. | ANAL   | YSIS OF AVAILABLE MEMORY   | 40 |

|   | 5.3. | MEM    | ORY DESIGN                 | 41 |

|   |      | 5.3.1. | Memory Type                | 42 |

|   |      | 5.3.2. | Memory Implementation      | 44 |

|   |      | 5.3.3. | BRAM Address Generation    | 46 |

|   | 5.4. | RESU   | LTS                        | 47 |

| 6 | TRI  | GGER   | IMPLEMENTATION             | 49 |

|   | 6.1. | OVER   | VIEW                       | 49 |

|   | 6.2. | TRIG   | GER SIGNALS                | 50 |

|   | 6.3. | SIMPI  | LE TRIGGER                 | 50 |

|   |      | 6.3.1. | Implementation             | 51 |

|   |      | 6.3.2. | Address Storage            | 51 |

|   |      | 6.3.3. | Drawbacks                  | 52 |

|   | 6.4. | PRET   | RIGGER I                   | 53 |

|   |      | 6.4.1. | Design                     | 54 |

|   |      | 6.4.2. | Implementation             | 55 |

|   |      | 6.4.3. | Address Storage            | 57 |

|   |      | 6.4.4. | Drawbacks                  | 57 |

|   | 6.5. | PRET   | RIGGER II                  | 57 |

vi

|        | 6.5.1. | Design         | 58 |

|--------|--------|----------------|----|

|        | 6.5.2. | Implementation | 58 |

|        | 6.5.3. | Drawbacks      | 60 |

| 6.6.   | RESU   | LTS            | 60 |

|        | 6.6.1. | Simulations    | 60 |

| BIBLIC | GRAP   | НҮ             | 63 |

| VITA   |        |                | 64 |

## LIST OF ILLUSTRATIONS

| Figu | re                                                          | Page |

|------|-------------------------------------------------------------|------|

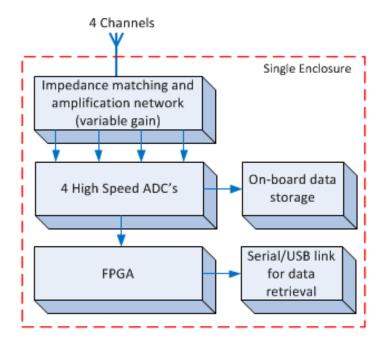

| 1.1  | System Block Diagram                                        | . 2  |

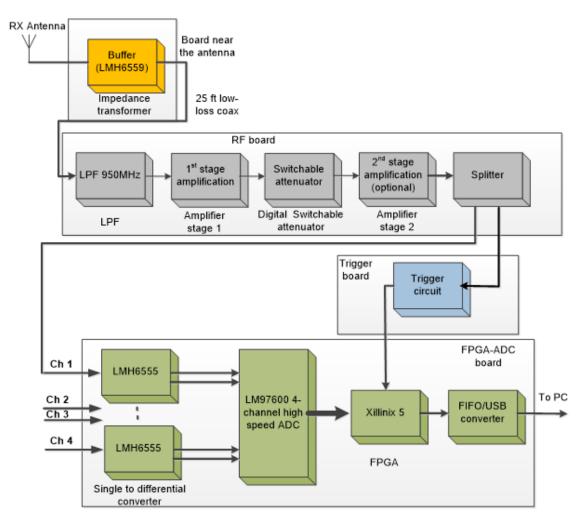

| 2.1  | Block diagram of the ADC-FPGA based data acquisition system | . 5  |

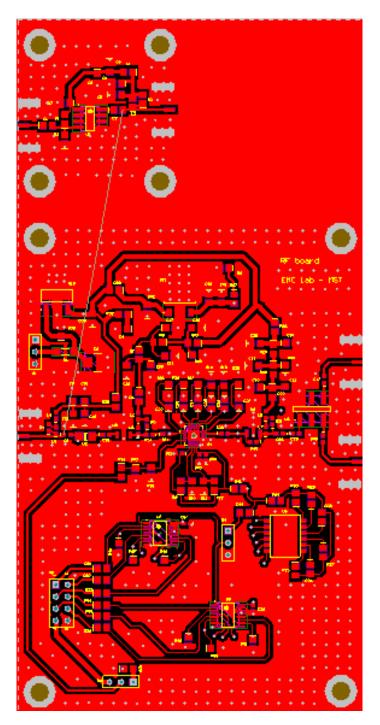

| 3.1  | Antenna and RF Board                                        | . 8  |

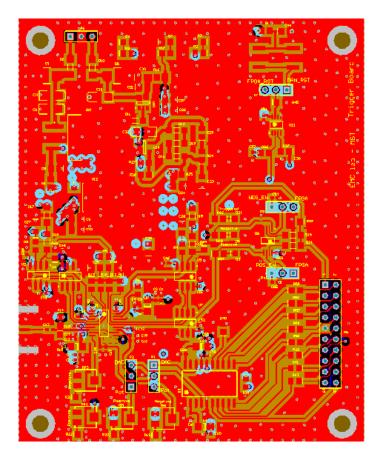

| 3.2  | Trigger Board                                               | . 10 |

| 3.3  | Power Scheme                                                | . 14 |

| 3.4  | Power Sequencing for the ADC                                | . 16 |

| 3.5  | Power Sequencing for the FPGA                               | . 17 |

| 3.6  | Power Board                                                 | . 18 |

| 3.7  | Main Board                                                  | . 19 |

| 4.1  | High-Level Archtecture of WV5                               | . 23 |

| 4.2  | Interaction between application and WV5 DLL                 | . 24 |

| 4.3  | LM97600 Configuration Register                              | . 28 |

| 4.4  | SPI Interface Configuration Register                        | . 29 |

| 4.5  | SPI Interface Manual Register                               | . 30 |

| 4.6  | Synchronization Control Register                            | . 31 |

| 4.7  | GTX Reset Register                                          | . 32 |

| 4.8  | Byte Alignment Registers                                    | . 33 |

| 4.9  | Channel Alignment Registers                                 | . 34 |

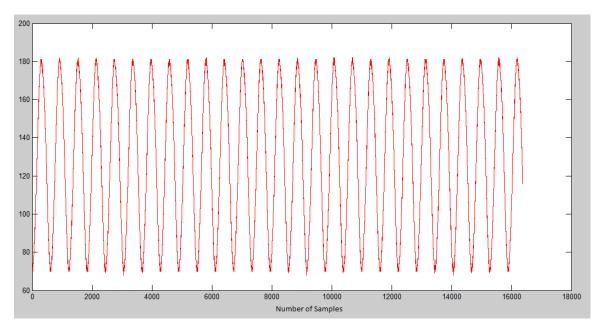

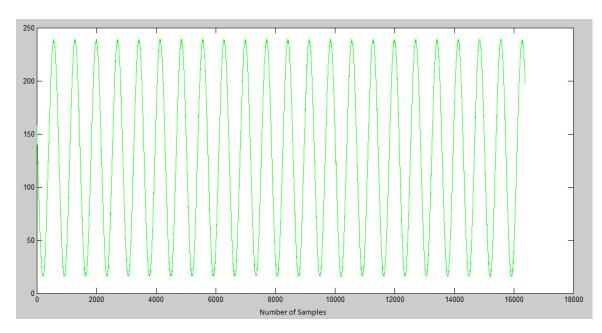

| 4.10 | Signal from the first channel                               | . 36 |

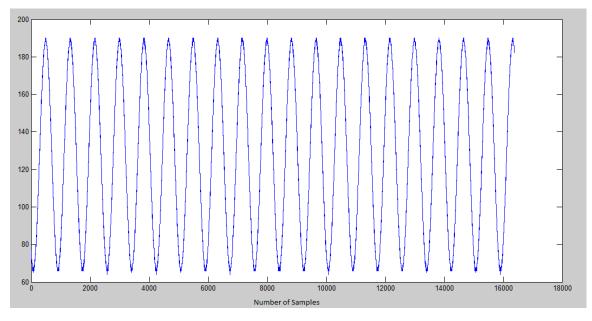

| 4.11 | Signal from the second channel                              | . 36 |

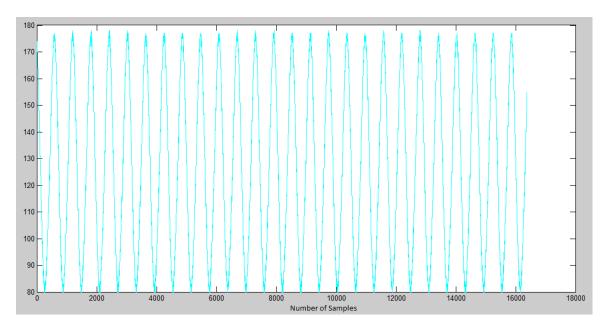

| 4.12 | Signal from the third channel                               | . 37 |

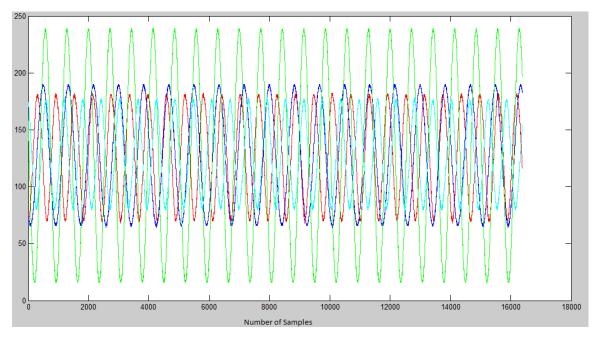

| 4.13 | Signal from the fourth channel                              | . 37 |

| 4.14 | Signals from all 4 channels                                 | . 38 |

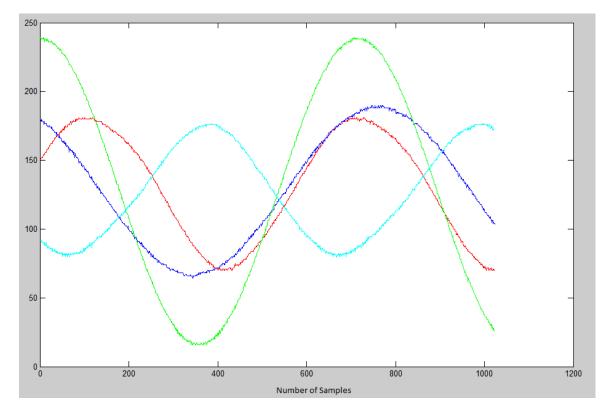

| 4.15 | Waveforms captured from all 4 channels                      | . 38 |

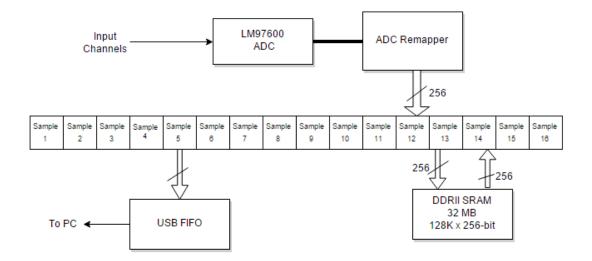

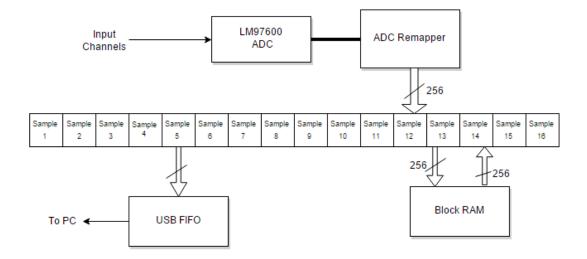

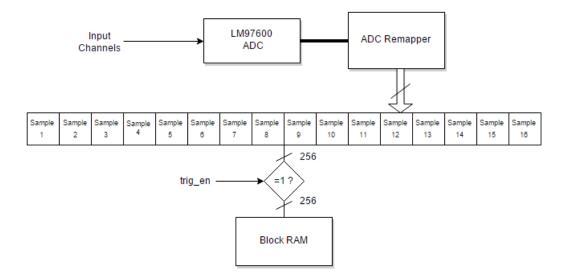

| 5.1 | Data flow path of the LM97600RB  | 42 |

|-----|----------------------------------|----|

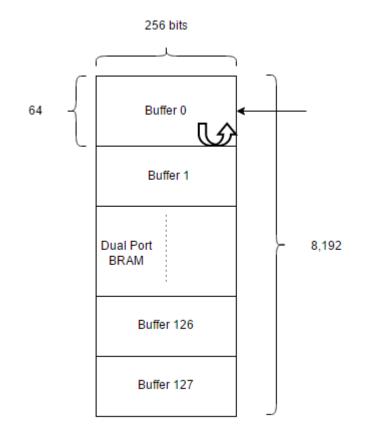

| 5.2 | Data sample storage in Block RAM | 45 |

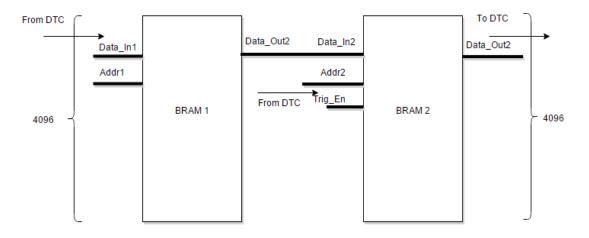

| 5.3 | Block RAM Generation 1           | 45 |

| 5.4 | Block RAM Generation 2           | 46 |

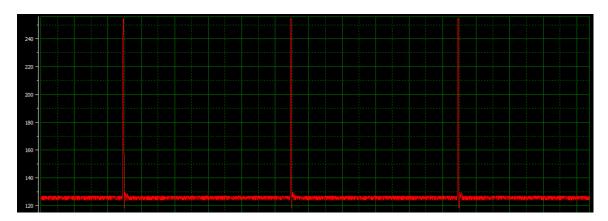

| 5.5 | Data captured from BRAM          | 48 |

| 6.1 | Simple Trigger Implementation    | 52 |

| 6.2 | FIFO Generator                   | 53 |

| 6.3 | Pre Trigger I Design             | 55 |

| 6.4 | Simple Dual Port RAM             | 56 |

| 6.5 | Design of PreTrigger II          | 59 |

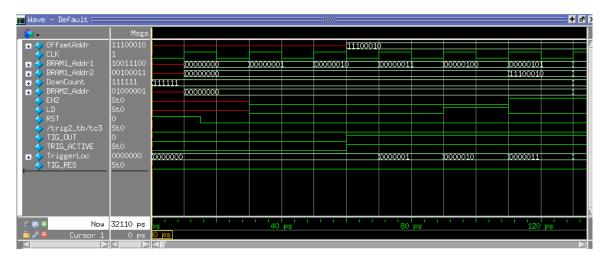

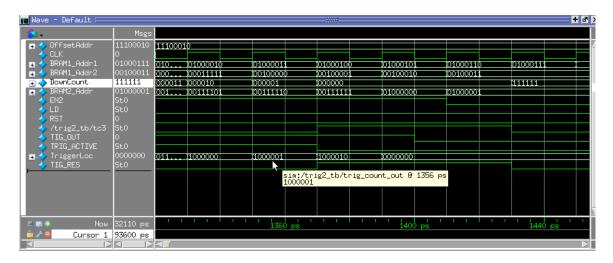

| 6.6 | Simple Trigger Simulation        | 61 |

| 6.7 | PreTrigger I Simulation          | 61 |

| 6.8 | PreTrigger II Simulation 1       | 62 |

| 6.9 | PreTrigger II Simulation 2       | 62 |

### LIST OF TABLES

| Table | e                                                      | Page |

|-------|--------------------------------------------------------|------|

| 4.1   | Files Required                                         | . 25 |

| 5.1   | Memory Consumption of the LM97600RB                    | . 40 |

| 5.2   | Memory Consumption of the Virtex-5 FPGA including BRAM | . 47 |

| 6.1   | Trigger Signals to the FPGA                            | . 50 |

#### 1. INTRODUCTION

Electrostatic discharge (ESD) is one of the most common events which results in damage and malfunctioning of devices such as Integrated Circuits (IC) due to its current and field. Static electricity can be induced by the human body by simply walking across a carpet, the effect also called triboelectric charging, which in turn leads to an ESD event when a metal is touched by the human body. An extreme example of an ESD event would be a lightning bolt. While the discharge of static electricity from the human body may not be a visible or a violent event, they may easily result in damage to ICs. The system level block diagram is shown in Figure 1.1.

In order to reduce the negative impact of ESD events, it is important and necessary to determine the origin and location of the ESD event. This would minimize the risk by allowing us to isolate or remove the device or entity responsible for the ESD event. This is especially important in environments such as electronics manufacturing environments which are highly susceptible to ESD and can cause potential problems.

Initially, identification of ESD events was performed as well as the strength of the ESD events was measured in an actual IC manufacturing environment, but determining the actual location of the ESD event was not performed. An ESD Event Locator System (EELS) was also built which involves the use of four EMI detectors as well as the use of a high-speed real-time digital oscilloscope. This is based on the principle of the Global Positioning System (GPS) on a smaller scale which determines the location of the ESD event to a resolution of 1 cm in each direction. The main issues in the system are the ease of installation and the overall cost of the system as it is based on an expensive real-time oscilloscope. Additional methods involve the use of four EMI detectors involving the principle of trilateration-based estimation as

Figure 1.1. System Block Diagram

well as the relation between the EMI strength and distance from ESD sources, in an EMI-based strength system. This method applies to smaller test area. However, the received signal strength indicator (RSSI) system applies to a larger test area and also uses the reverse GPS principle involving the use of mobile and stationary nodes to determine the location of the ESD event.

This paper discusses an alternative to the EELS which uses four EMI detector but rather than using a high-speed real-time digital oscilloscope, we replace it with high-speed sampling ADCs. The ESD locator system is made cost-effective and also provides ease of installation and use. These ADCs along with the front-end analog receivers can be mounted in a single enclosure with a single power-supply to reduce the complexity of the system. Provisions can also be made to directly use the system with a laptop that processes and saves the data in a suitable format. While the paper discusses the principles behind the working of the system, it focuses on the implementation of the ADCs and using the high-speed ADCs to detect and capture the ESD events.

#### 2. DESIGN CONCEPT

An ESD event locator system uses reverse time of arrival process to localize ESD events in a 3D space. A previously implemented system included 4 antennas to receive and capture radiated emission generated by the ESD event. The system essentially used a high-speed sampling scope to capture and store the data which can be processed later. An inherent difficulty of the system was high cost of the oscilloscope and its under-utilization for this purpose, so the current approach uses high-speed sampling ADC's instead of the scope. The high-level block diagram of the system is shown in Figure 2.1.

The input closed loop buffer is used to match the input impedance with the antenna. A biased tee network is used to power the remote input buffer from the next stage though the coax cable. Next, the high dynamic range of GALI84+ device is used to increase the signal strength to an acceptable level. The device provides a gain of around 25 dB from DC-6GHz with P1dB of 21dBm. A wideband bias choke is used to isolate the RF and DC at the output of the amplifier. A digital switchable attenuator can be controlled in steps of 0.5dB up to 31.5 dB either from FPGA or using manual DIP switches. Optional amplification stage is provided to further improve the signal level.

The amplified signal is provided through a resistive splitter to a Trigger circuit and an ADC input. The Trigger circuit utilizes a window detector to produce logic high when the signal exceeds the threshold. A differential PECL comparator along with a PECL latch provides the window detector with the ability to capture signals with pulse widths as low as 500ps as required for ESD signal detection. The reference levels of the comparator can be controlled through an on-board DAC from the FPGA

Figure 2.1. Block diagram of the ADC-FPGA based data acquisition system

or manually through potentiometers. The trigger signal forces the FPGA to capture ADC sampled data.

The ADC is a single/dual/quad channel high performance ADC that digitizes signals at sampling rates up to 5/2.5/1.25 GSPS. The digital output samples are transmitted to the FPGA at 50-Gbps using 8B/10B on 10 LVDS pairs. The input data from the RF stage is provided to the ADC through a high-speed single-ended differential driver. A fully integrated delta-sigma PLL and VCO IC is used to provide a 2.5 GHz low-jitter AC coupled differential clock signal to all converters in ADC. The ADC can be controlled in extended control mode through a SPI interface from FPGA.

The rocket I/O trans-receiver provided in Xilinx Virtex 5 FPGA is utilized to receive digital samples from the ADC. The data from the ADC is temporarily stored in on-chip SRAM before being pushed though the FIFO/USB converter to PC. An on-board PROM facilitates storage of FPGA configuration during power-off. FPGA I/O ports are used to interface the ADC, PLL, trigger, and RF board control signals.

To power the ADC, FPGA, and other peripherals, a lower noise regulated power scheme provides power-up and power-down sequencing of 8 different supplies.

#### 3. HARDWARE

#### 3.1. ANTENNA AND RF BOARD

The RF board will be near the antenna to provide impedance matching with the antenna and buffer the signal to be sent over the cable to the ADC board. The layouts of the board is shown in 3.1 [6].

LMH6559 (U1) is a closed loop buffer used as an impedance transformer to match the antenna source impedance to the cable impedance. For board 1, power supply is provided by coax cable feed. The coax cable carries DC from the board 2 to board 1. Here it is decoupled using the ferrite beads L1 and L2. C2 blocks the DC from entering the buffer. L1 and L2 filters the DC from AC and provides it to the VCC (pin 1). Also it is used to provide a bias to the input using R1 and R2.

Port 1 connects the 25ft coax cable from board 2 to board 1. L4 and L3 ferrite beads form the filter that is used to the DC to the cable feed. A low pass filter U2 (LFCN 850+) is used to filter out higher frequency component greater than 1GHz. U3 is a GALI84+ wideband amplifier with high dynamic range. It provides 25.6dB gain @100MHz with P1db as 21.9dBm in the range of DC-6GHz. The output pin of the U3 is RF out and bias, so DC bias is provided using a L6-L5 ferrite beads and filtering network. The next IC is U4 (Dat-31R5-PP+) which is digitally switchable attenuator. It provides 31.5dB of attenuation in steps of 0.5dB. It can be controlled using 6 bit parallel interface. It can handle up to 24dBm of power. The board provides both the provision for controlling it from FPGA (software) and using manual DIP switches. Another optimal amplifier stage is provided if more gain is required. It is the same amplifier as before with the same biasing configuration.

Figure 3.1. Antenna and RF Board

U7 and U8 (SN54LV157A) are data selectors to select digital inputs either from the FPGA (Through P5 header) or from the 6-DIP switch (U9). A 3-pin header P4 is used to select between the FPGA and the DIP switch inputs.

#### 3.2. TRIGGER BOARD

With a constant stream of 50 GSps of data from the ADC, it would be challenging if not altogether impossible to transmit and process all the data inside the FGPA in real time. However, only data around an ESD pulse is meaningful, so the majority of the data can be ignored. To simplify the design, a trigger circuit was needed to monitor the analog input and trigger on desired input signals. This would allow the FPGA to capture only the desired data while removing the need to do any data processing. The objective was to design a circuit that could detect a pulse as small as 1ns while ignoring as much non-ESD phenomena as possible.

The first step was to determine what type of trigger method to implement. One of the most basic solutions was to create a simple comparator. However, an ESD pulse could be positive or negative. The next option was to implement an adjustable window comparator. With the voltages adjustable, the circuit could easily be tune above the noise floor to prevent being triggered on undesired signals. The layout of the trigger board is shown in Figure 3.2 [6].

Since an ESD pulse has a fairly unique profile, other triggering methods were considered that would help differentiate between random noise and an ESD event. One such method was to monitor the rise and fall times using a capacitor as a differentiator. Another option was to create a circuit to measure the width of a pulse and only trigger on those signals that fall within a specific range.

However, the simple window comparator was chosen as the most practical solution to design first. The window detector was implemented using the PECL

Figure 3.2. Trigger Board

ADCMP562 comparator. TLL, CMOS, and even LVDS were not fast enough to trigger on a 1ns ESD pulse so PECL was the only option. Although faster comparators exist, the ADCMP562 was chosen because its propagation delay of 700ps would reduce the possibility of it ringing and triggering on undesired signals. Other reasons the ADCMP562 was selected are that it has a latch input and internal hysteresis that can be controlled by an external pin which will help the circuit latch on the correct signal level.

To use the hysteresis pins, 50k potentiometers were placed on the pin to GND. Originally a DAC was going to control the hysteresis, but it was decided manual control would suffice since hysteresis would not need to be changed all the time. The input to the comparator was expected to be a low plus and minus voltage signal and the comparator input voltage range was -2 to 3V. However, to avoid having to supply negative voltage references, the input was biased to 1.5V with a capacitor in series and pull-up and pull-down resistors. The standard input range then became 0-3V.

For the comparator circuit to be useful at all, the positive and negative reference signals had to be adjustable. Potentiometers were placed on the board to allow for manual adjustment. For automatic adjustments from FPGA a DAC was placed on the trigger board. A simple jumper pin selects between manual and automatic (FPGA) mode. On the first design, the DAC was connected incorrectly. By default the DAC is current driven and to use it in voltage mode there was only one small diagram in the datasheet that showed that the output and reference signals must be swapped from the standard configuration (OUT was then connected to the input and REF was the output).

The next step was to design a circuit that guarantees that the trigger signal will be received by the FPGA. The simplest method seemed to be to integrate a low pass filter to lengthen the pulse. However, this would not be the most stable method and it would be difficult to lengthen the pulse long enough for TTL logic to recognize it. Even then it requires the FPGA to be able to capture a very fast pulse. To avoid these challenges, the latch input on the ADCMP562 was utilized. The trigger board uses the MC10EL31 PECL D flip flop with a propagation delay of 475 ps to latch the comparator. The D flip flop also allows the trigger circuit to be reset after a latch.

An interesting caveat with the MC10EL31was how the D input needed to be pulled high. On simple TTL logic, this is no issue. But for this chips PECL levels, a high input at 25 degrees Celsius is 3.870 to 4.190V. Although a resistor divider circuit definitely could have been implemented, 2 diodes with the total voltage drop equal to 0.81 to 1.13V were connected to 5V with the hope of using less current than a resistor divider circuit. To guarantee that the diodes sustained the correct voltage drop, a resistor was placed from the D input to GND. This resistor could possibly be removed or set to a very high value.

The interfacing buffers to the FPGA are all TTL so any signals connecting to the FPGA must be converted to or from PECL. The SN65ELT21 was used to translate the output trigger signals to 5V. The SY10ELT20VZG was used to convert the 5V reset output from the FPGA to PECL logic levels.

To enable or disable the positive and negative triggers, the dual AND gate 74HC2G08 was implemented. Jumpers were placed on the board to allow the channels to be enabled or disabled manually or to select FPGA control. Since there is no disable on the comparator, the AND gate just passes the trigger signal or blocks it. Finally, two diodes are used to OR the signals together so there is only one trigger signal going to the FPGA.

The final step was the power supply circuit. For 5V the LDO UA7805 was implemented. The 3V was supplied from a simple 3V LDO called the BA30BC0FP-E2. The -5V LDO MIC5270 supplied the -5V. However, the ADCMP562 comparator required -4.96 to -5.45V. Although a -5.2V LDO would have worked better, no simple LDO was discovered with that output voltage. To add to the challenge, no -5V LDO guaranteed high enough accuracy not to go above -4.96. So a diode was placed on the GND pin of the MIC5270 to drop the voltage slightly. Finally, a 3V sinking source was required for the PECL terminations. Since PECL voltage levels are always higher than 3V, the supply will only be sinking current. For this application, a negative output adjustable LDO was implemented. However, the input and GND pins were swapped to make it positive 3V. Since the device can only sink 200mA, diodes were placed on the output signal to add a voltage drop and allow the device to sink more current

The trigger board was implemented on 4 layers. The top and the bottom layers are the signal layers. The Second layer is the GND layer and the forth layer is the power layer. The main challenge of the layout was the PECL termination and the high speed signals (the comparator input and the latch). All the single trace high speed signals are 17mils wide and the differential lines are 12mils wide with 10mils separation where possible. The differential pairs were routed to be as close as possible in length and as short as possible. The termination resistors were placed on the input side of the differential traces.

The main expectation was to be able to latch on a 1ns signal when the input exceeds the positive or negative references levels. The majority of the testing was done on a function generator that provided a trapezoidal pulse with a rise and fall time of down to 0.1ns and a pulse width of down to 0.1ns. The signal was fed directly into the trigger board and the inverted signal was fed into the scope.

The power supplies all provided the correct voltages, but they got warmer than expected. The trigger board was designed to be powered with +-12V, but with that much voltage drop across the LDOs, the board became almost too hot to touch. So during testing the voltage input was close to +-7.8V.

When the potentiometer on the hysteresis pin was set to zero ohms, the trigger circuit did not work. With zero resistance the hysteresis will be at a maximum and so the input would never exceed the hysteresis value. However, with the hysteresis set too low it could be possible for the comparator to be latched on a low level and therefore it would miss the trigger signal. So for the circuit to work well the hysteresis must be set lower than the desired input and higher than the noise. Testing showed 20mV or 20k ohms to be a good comprise.

As mentioned above, the DAC did not work at all during the first power up. However, only two pins for each channel were swapped. When connected correctly, the following data was collected from the DAC over the range of the output.

The trigger board implemented one of the most basic methods to latch on an ESD pulse. However, it was successful in triggering on even less than a 1ns pulse and

seemed to do quite well with not triggering on random noise. All of the other sections of the design including the power supply, the enable circuit, the reset, and the DAC functioned correctly.

#### 3.3. POWER BOARD

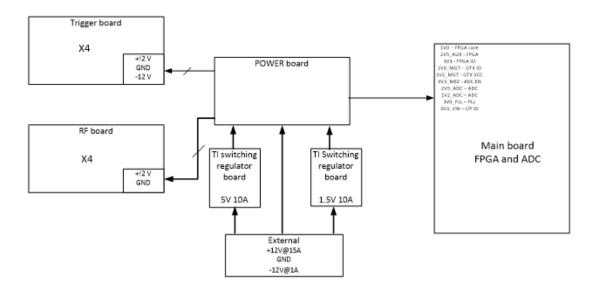

Power for the FPGA and ADC board is separated on a new board for ease of debug and to reduce the complexity of the main board. The board also provides power to the Trigger boards as well. The LM97600 ADC requires power sequencing when it is turned on and the power sequencing is implemented for both the ADC as well as the FPGA. The power sequence of the Power Board is shown in Figure 3.3.

The Power board is responsible for supplying power to the four RF Boards, four Trigger Boards and the Main Board. The RF Boards and the Trigger Boards take power supplies of  $\pm$  12V while to provide the different power supplies to the Main Board for the FPGA and the ADC, it takes  $\pm$  5V and  $\pm$  1.5V.

Figure 3.3. Power Scheme

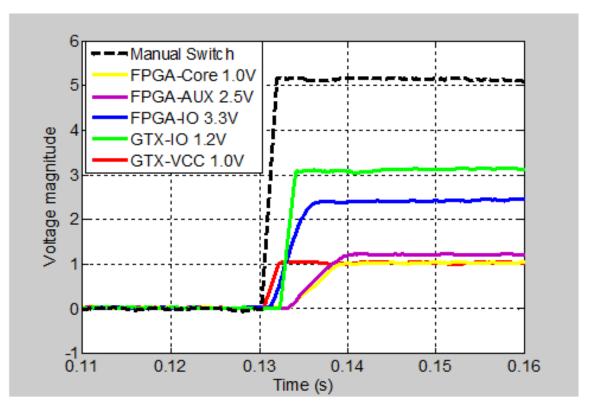

The master input switch and enable for the power board consists of a 5V input to a 3.3V LDO which is the TPS73733 while a switch S1 is used as an enable to generate a 3V3 which acts as bias for the power sequence of the FPGA.

The power sequence of the FPGA consists of using the 3V3 as a bias. The FPGA Core takes a core voltage of 1 V and it uses the U9 TPS74901 which is a linear regulator with a programmable soft-start. It is open for a start time of 0.1 ms for the FPGA core voltage. The FPGA Aux takes a voltage of 2.5 V and uses the same regulator for a delayed start of 5ms.

The voltage to the IO banks of the FPGA is provided by the FPGA IO voltage which uses a 3.3 V linear regulator without any delayed start. The power supply for the GTX\_IO and the GTX\_VCC for the GTX Transceivers of the FPGA require a delayed start and use the TPS74901 for a start time delay of 6ms. The power sequencing for the FPGA is shown in Figure 3.5.

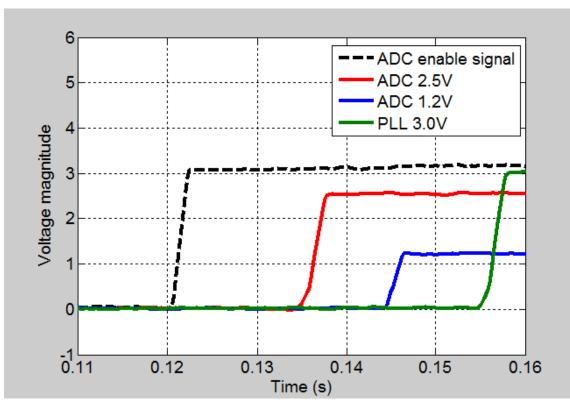

The power sequencing for the ADC is much more critical than the FPGA for the correct working of the ADC, so power sequencing circuits had to be designed for the ADC as well. The enable for the ADC used the 3V3 TPS73733 LDO which would be powered on after the FPGA was powered on. This would give a 3V3\_MEZ to be used for generating the sequence of signals for the ADC.

The LM3880 is a simple sequencer IC which would give a power sequences with a delay of 10ms, 20ms and 30ms. The first sequence would be for the 2V5 for the ADC which used a low noise voltage regulator, the LP3878MR IC. This would take an input voltage of 5V. The second sequence would use the TPS74901 for the 1V2 ADC with a delay of 20ms. The third and final sequence would be for the 3V0 PLL which would involve a delay of 30ms and use the low noise LP3878MR IC as well. The power sequencing of the ADC is shown in Figure 3.4 and the layout of the Power Board is shown in 3.6 [6].

Figure 3.4. Power Sequencing for the ADC

#### 3.4. MAIN BOARD

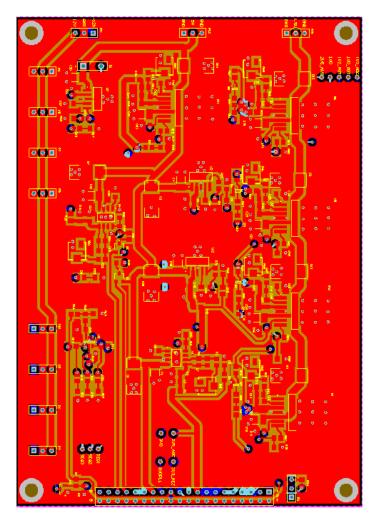

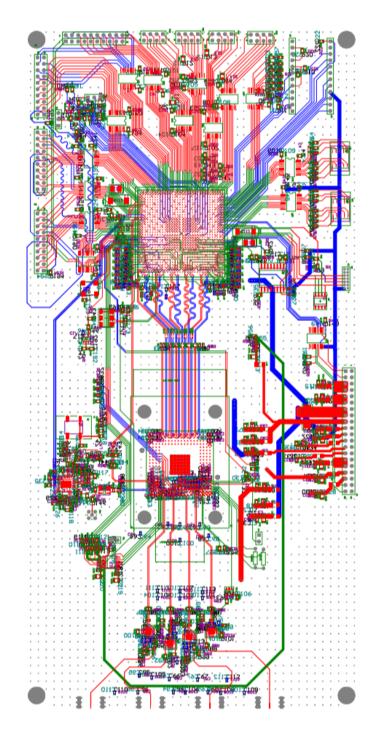

The Main Board is an 8-layer board which forms the primary data acquisition system and consists of an ADC and an FPGA that is interfaced to the ADC. It interfaces with the all the other boards such as the RF Boards and the Trigger Boards in order to complete the ESD Event Locator system. The layout of the Main Board is shown in Figure 3.7 [6].

The design of the board was referenced from the LM97600RB which uses the LM97600 ADC and the Virtex-5 FPGA for the data sampling and subsequent acquisition. The LM97600 is a high-speed 7.6-bit ADC with a maximum sampling rate of GS/s with 4 input channels to it. It operates in Single, Dual and Quad-mode with speeds of 5 GS/s, 2.5 GS/s and 1.25 GS/s respectively in the various modes. It

Figure 3.5. Power Sequencing for the FPGA

has a 10-lane high speed serial data output which uses LVDS to transfer out the data from the ADC.

The primary reason for the choice of this ADC was the availability of 4 channels on the ADC for each of the 4 signals from the antennas. The data from the ADC is encoded in 8b10b format. This ADC greatly reduces the synchronization challenges associated with the other ADCs. The system reduces to a single ADC and FPGA for the signal capture on all the four antennas. This would drive down the cost drastically, but the complexity in terms of handling data from ADC and FPGA design increases significantly..

The Virtex-5 FPGA, specifically the XC5VFX70T, was chosen as the FPGA to interface with the LM97600 due to the availability of 16 high-speed RocketIO GTX Transceivers which would be used to capture the data samples on the 10 output lanes

Figure 3.6. Power Board

of the high speed ADC. The GTX Transceivers are able to handle speeds from 150 Mb/s to 6.5 Gb/s which makes it an excellent option to be used with the ADC. The Virtex-5 FPGA would be responsible for interfacing and controlling the LM97600 for data capture and storage of the data samples as well as modifying the registers of the ADC via SPI lines setup between the FPGA and the ADC.

The Virtex-5 FPGA is volatile which means that the FPGA has to be reloaded with the FPGA image each time the Main Board is booted up. A Flash EPROM is

Figure 3.7. Main Board

placed on the Main Board to automatically load the FPGA image onto the FPGA each time the Main Board is re-booted.

The FPGA is provided with a clock oscillator of 100 MHz and the FPGA is also programmed with a PLL to provide clocks for the various modules present in the FPGA code. The GTX Transceivers have their own 200 MHz clock oscillator connected to the banks of the FPGA consisting of the GTX Transceivers.

There is a JTAG interface provided on the Main Board and connected to the FPGA for debugging and programming purposes. This allows the Main Board to be troubleshooted when the FPGA is being programmed to verify the proper working of the ADC and the FPGA. In order to transfer data from the FPGA to the PC, a USB FTDI IC is provided to interface with the FPGA to read/write to the registers of the FPGA and subsequently transfer off the data from the internal memory of the FPGA to the PC for post-processing.

The IO pins of the Virtex-5 FPGA are also responsible for interfacing with the trigger board since the trigger board will send the trigger signal to the FPGA for the FPGA to capture the ESD signals from the ADC on the occurrence of the trigger signal. The FPGA is also responsible for resetting the trigger board once the data samples have been acquired. In the automatic mode, the FPGA is also responsible for setting the reference voltages of the comparator via the DAC provided on the trigger board. The Main Board provides pin connectors for these signals from the four trigger boards.

The Main Board also provides pin connectors for the control of the 6-bit Digital Attenuators on the RF Boards and these are also set by the FPGA if they are in manual mode.

The ADC is provided with a 2.5 GHz PLL and VCO and low jitter for the four converters in the ADC. The PLL is also interfaced through SPI lines with the

Virtex-5 FPGA for extended control. The power supplies for the FPGA and the ADC are from the power board as has been previously discussed.

#### 4. DATA ACQUISITION

#### 4.1. OVERVIEW

The data acquisition portion of the project refers to the acquisition of the data samples from the ESD events which are stored on the Block RAM (BRAM) of the FPGA. Since the FPGA is only responsible for the capture and the storage of the data samples on the occurrence of the trigger signal, we require the transfer of the data samples from the BRAM of the FPGA to the Personal Computer using a communication protocol such as a Universal Serial Bus (USB). The Virtex-5 FPGA on the Main Board is responsible for the storage of the data samples and a USB Microcontroller (MCU) is located on the Main Board which interfaces with the FPGA for communication between the PC and the Main Board.

The objective was to transfer the data samples to the PC using a software such as MATLAB© which would enable the post-processing of the data samples for determining the location of the ESD event. WaveVision 5©, a data analysis and data acquisition software from Texas Instruments®, was used as a reference to manipulate the registers of the FPGA as well as the registers LM97600 Analog-Digital Converter to achieve the final objective of acquiring the data from the BRAM of the FPGA.

#### 4.2. WV5 DLL

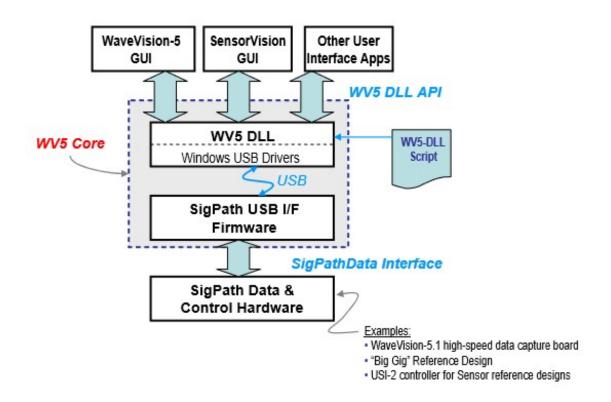

The WV5 DLL provides a set of functions that will allow the caller to configure and communicate with the data I/O boards and the devices connected to those I/O boards as illustrated in the high-level architecture of WV5 in the Figure 4.1. The main objective of the DLL is to provide access to the data both generated and consumed

Figure 4.1. High-Level Archtecture of WV5

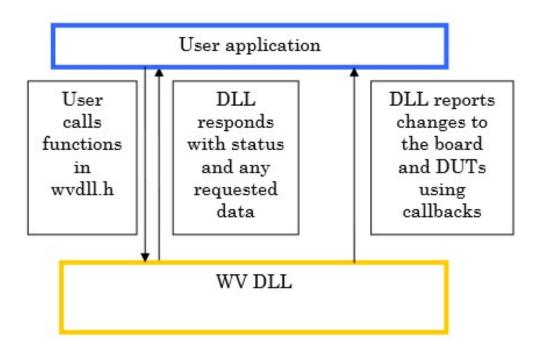

by the device under test (DUT). The interaction between the application and WV DLL is illustrated in Figure 4.2.

The WV5 DLL gives the option to interface with the board by using alternative applications such as MATLAB© in order to gather the samples from the FPGA. In the figure above, the WaveVision-5 GUI application can be replaced with an alternative application such as MATLAB/textcopyright as long as the WV5 DLL is present and use the APIs provided by the wv5.dll to communicate with the board. The interaction between the application and the WV DLL is also illustrated in Figure 5.2. The WV DLL provides a set of APIs using which the communication between the PC and the Main Board is established, the registers of the FPGA and the ADC are modified and finally the data acquisition takes place.

Figure 4.2. Interaction between application and WV5 DLL

### 4.3. FILES REQUIRED

The application to interface with the Main Board requires the presence of the files in Table 4.1:

#### 4.4. APPLICATION INTERFACING

MATLAB© was used to interface with the hardware and to acquire data from the FPGA to the PC using the API functions provided by the WV DLL with the presence of the files mentioned in Table 5.2. This forms the core of the second part of the thesis which is to acquire the data from the Main Board to the PC in order to perform post-processing on the signals. This section describes the various API functions used to successfully communicate to the Main Board from the PC using the

| Name                                               | Description                  |

|----------------------------------------------------|------------------------------|

| wvdll.dll                                          | DLL                          |

| libcint.dll                                        | C Scripting Engine           |

| wv5.sys                                            | Windows Communication        |

|                                                    | Driver                       |

| wv5.inf                                            | Information file             |

| wvdll.h                                            | Programmer's interface       |

| hardware\firmware_images\wv4.x_cy7c68013a.bix      | Cypress Microncontroller     |

|                                                    | Image                        |

| hardware\fpga_images\spio5.5_xc5vsx95t_lm97600.bit | FPGA Image                   |

| hardware\scripts\image_map.xml                     | File to map boards and de-   |

|                                                    | vices to their support files |

Table 4.1. Files Required

USB communication protocol. As previously mentioned, the Main Board is equipped with a USB microcontroller which provides a hardware interface to the FPGA from where the samples are acquired.

4.4.1. Initialization. The initialization section involves loading the API functions of the WV DLL library and then subsequently loading the API functions in a series of steps to initialize and interface with the FPGA board by identifying the board connected, loading the MCU image and then finally loading the FPGA image onto the FPGA. Since the FPGA is volatile, it needs to be loaded with the FPGA image each time the Main Board is booted up. The initialization routine was written in the file labelled Initialization.m. The APIs used in the initialization routine are listed below and their purpose defined. The APIs are listed in the order of their use in the initialization routine.

WvBoardEnum ('ulongPtr', 'cstringPtrPtr', 'WvVersionNumberPtr')

This API enumerates the boards that are connected to the USB and lists the number of boards connected, their names and the board names.

# WvBoardOpen ('ulong', 'cstring', 'ulongPtr', 'WvVersionNumberPtr')

This API will open the board for access and determine the Cypress MCU on the board and it's version and will load the required Cypress MCU firmware by selecting it from the firmware images folder.

# WvBoardDUTEnum ('ulong', 'ulongPtr', 'cstringPtrPtr')

The API will determine the number of DUTs present on the board and will list the names of the DUTs present on the board.

# WvBoardLoadFPGA ('ulong', 'ulong', 'cstring', 'WvVersionNumberPtr')

This API will load the FPGA image from the FPGA images folder based on the DUT name and in our case, it is the LM97600 DUT.

# WvBoardReadDUTInfo ('ulong', 'ulong', 'WvDUTInfoPtr', 'WvVersionNumberPtr')

This API will gather information on the DUT such as the version number of the DUT based on the DUT that is selected.

# WvGetSamplingFrequency ('ulong', 'ulong', 'ulong', 'doublePtr')

This API will determine the sampling frequency of the DUT which for the LM97600 is 5GS/s. The initialization is completed at this stage and the Main Board and the FPGA is ready for the data to be acquired.

4.4.2. Register Initialization. This section deals with configuring the registers of the LM97600 since the ADC uses all four of its converters and there are 4 channels from which receives an input. The 4 inputs are from the 4 antennas which all capture the ESD event. In order to use all the 4 channels and to configure the inputs to the different channels so that the ADC is operating in the Quad mode, the register has to be set as specified in the datasheet which is shown in Figure 4.3.

The FPGA communicates with the LM97600 ADC through the Serial Peripheral Interface (SPI) and the WV DLL provides APIs for communicating with the ADC registers via the Cypress MCU and the Virtex-5 FPGA. In order modify the configuration register to work in the Quad mode, low-level API functions are used to write to the registers. The configuration register is a 16-bit register and the Quad-mode requires the bits 6:15 modified based on the datasheet specifications. The functions used for this purpose are described below. The library provides two ways to write to the ADC registers. The first method is using the API method and the second method is using the manual method which uses bit-banging to configure the ADC register via SPI. One of the two methods has to be selected and this is done by configuring the SPI Interface Configuration Register of the FPGA shown in Figure 4.4. The FPGA also uses the SPI Manual Control Register shown in Figure 4.5, for bit-banging and the two methods are described below. The API method requires that the all the bits of the SPI Interface Configuration Register are set to the value 16. The SPI Address High and te SPI Address Low registers are written with the addresses and the values that need to be written to the registers. However, issues were experienced using the API method and the ADC registers were unable to be written to, using this method. The API function used for writing to the register of the FPGA is shown below.

| Addr: 0  | 1h (0 00 | 01b) |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                          |                              |                                                              |                            |                      |          |           |          |          | P          | OR state | : 0000h |

|----------|----------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------|----------------------------|----------------------|----------|-----------|----------|----------|------------|----------|---------|

| Bit      | D15      | D14  | D13 | D12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D11                                                                                                                                                      | D10                          | D9                                                           | D8                         | D7                   | D6       | D5        | D4       | D3       | D2         | D1       | D0      |

| Name     | Mo       | de   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                          | Input                        | Select                                                       |                            |                      |          | DC        | Res      | TPM      | Res        | BMP      | STA     |

| POR      | 0        | 0    | 0   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                        | 0                            | 0                                                            | 0                          | 0                    | 0        | 0         | 0        | 0        | 0          | 0        | 0       |

| Bits 15: | 14       |      |     | 00 =<br>01 =<br>10 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Single A<br>Dual AD<br>Quad Al                                                                                                                           | DC (Sam<br>C (Sam<br>DC (Sam | he opera<br>mples at<br>ples at F<br>nples at I<br>No not us | 2xFclk)<br>clk)<br>Fclk/2) | ie as foll           | ows:     |           |          |          |            |          |         |

| Bits 13: | 6        |      |     | 11 = Invalid setting. Do not use.         Input Select: Depending on the ADC Mode selection, determines which inputs are used as follows:         Mode = Single ADC         Selected input for all converters set by bits 7:6.         Other bits unused.         00 = Input 1         01 = Input 2         10 = Input 3         11 = Input 4         Mode = Dual ADC         Selected input for converters A and C set by bits 7:6         Selected input for converters B and D set by bits 9:8         Other bits unused.         00 = Input 1         01 = Input 3         11 = Input 4         Mode = Quad ADC         Selected input for converter A set by bits 7:6         Selected input for converter A set by bits 7:6         Selected input for converter A set by bits 7:6         Selected input for converter A set by bits 7:6         Selected input for converter A set by bits 7:6         Selected input for converter B set by bits 7:6         Selected input for converter C set by bits 11:10         Selected input for converter D set by bits 13:12         Other bits unused.         00 = Input 1         01 = Input 2         10 = Input 3 |                                                                                                                                                          |                              |                                                              |                            |                      |          |           |          |          |            |          |         |

| Bit 5    |          |      |     | The<br>Setti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                          | etting of                    | ob select<br>ob selects<br>selects D                         |                            |                      |          |           | i.       |          |            |          |         |

|          |          |      |     | Must                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | be set to                                                                                                                                                |                              |                                                              |                            |                      |          |           |          |          |            |          |         |

| Bit 3    |          |      |     | Setti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ADC Test Pattern Mode Select<br>Settings this bit to 1b replaces the normal ADC output with a configurable test pattern output as set by<br>Register Dh. |                              |                                                              |                            |                      |          |           | set by   |          |            |          |         |

| Bit 2    |          |      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | rved<br>be set ti                                                                                                                                        | o Ob.                        |                                                              |                            |                      |          |           |          |          |            |          |         |

| Bit 1    |          |      |     | Setti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                          |                              | 'bumps" o<br>This bit r                                      |                            |                      |          |           |          | order of | the interl | eaved    |         |

| Bit 0    |          |      |     | Setti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | AD Adjus<br>ng this bi<br>ted via F                                                                                                                      | t to 1b e                    | mables t<br>Ch.                                              | he built i                 | n t <sub>AD</sub> ad | justment | circuitry | . The ar | nount of | aperture   | delay a  | dded is |

Figure 4.3. LM97600 Configuration Register

| Address   | Register | Reset       | Bit 7                                                                                                                                                                                                                                                                                                                   | Bit 6                     | Bit 5                                                                                                                                        | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|

| 0xD022    | SPI CFG  | 8'h00       | -                                                                                                                                                                                                                                                                                                                       | -                         | SCK                                                                                                                                          | _SL   | BDL   |       | SDS   |       |

| Bit [5:4] | R/W      | SCK_SL[1:0] | Clock Frequency Select These bits select the<br>clock frequency for the ADC SPI interface.<br>When these bits are all 0, manual mode is<br>selected and all the accesses to the ADC are<br>performed by bit-banging the appropriate<br>bits in the SPI_MCTL register. SCK_SL<br>encodings are shown in the table below. |                           |                                                                                                                                              |       |       |       |       |       |

| Bit [3]   | R/W      | BDL         | Bidirectional Data Line When this bit is set<br>to 1, the SPI interface uses one bidirectional<br>signal rather than two separate signals for<br>input and output. The MOSI signal becomes<br>bidirectional and the MISO signal is unused.                                                                              |                           |                                                                                                                                              |       |       |       |       |       |

| Bit [2:0] | R/W      | SDS         | target dev<br>interface.<br>one devic                                                                                                                                                                                                                                                                                   | rices to be<br>In the cur | elect These bits select one of 8<br>to be accessed by the SPI<br>he current implementation only<br>present and therefore these bits<br>to 0. |       |       |       |       |       |

Figure 4.4. SPI Interface Configuration Register

# WvNewestHardwareWrite ('ulong', 'ulong', 'WvDebugAccessMethod', 'ulong', 'ulong', 'ulong', 'ulong', 'ulong', 'ulong')

This API allows writing to the registers of the FPGA as well as communicate to the ADC registers throught the SPI lines between the FPGA and the LM97600 ADC. The ADC configuration register is set to Quad-Mode using this method.

This API allows writing to the registers of the FPGA as well as communicate to the ADC registers through the SPI lines between the FPGA and the LM97600 ADC. The ADC configuration register is set to Quad-Mode using this method.

In the bit-banging method, the above API is repeatedly called and the SCLK and the SDO are repeatedly asserted and de-asserted to pass the data to the ADC registers until the bits that need to be asserted are all sent resulting in the ADC being set into Quad-Mode. This process has to be repeated every time the Main Board is powered on and the FPGA is programmed. The first method using the API functions failed to set the registers in Quad-mode but the second method of bit-banging set the

| Address | Register | Reset | Bit 7                                                                                                                                                                                                                                                                                                                                                   | Bit 6        | Bit 5                         | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------|-------|-------|-------|-------|-------|

| 0xD021  | SPI_MCTL | 8'h00 | -                                                                                                                                                                                                                                                                                                                                                       | -            | EBD                           | OBEN  | SCS   | SCLK  | MOSI  | MISO  |

| Bit [5] | R/W      | EBD   | External Buffer Direction Control This bit<br>is effective only when the BDL bit in the<br>SPI_CFG register is set to 1 and Manual<br>Mode is selected. It controls the direction of<br>an external buffer that may be placed on the<br>SPI data line. It must be 0 while data is<br>being written to the SPI target and 1 while<br>data is being read. |              |                               |       |       |       |       |       |

| Bit [4] | R/W      | OBEN  | Output Buffer Enable When set to 1, the<br>serial data output buffer is enabled. This bit<br>is used in Manual Mode only                                                                                                                                                                                                                                |              |                               |       |       |       |       |       |

| Bit [3] | R/W      | SCS   |                                                                                                                                                                                                                                                                                                                                                         | nal. This b  | t This bit d<br>it is used ir |       | nip   |       |       |       |

| Bit [2] | R/W      | SCLK  |                                                                                                                                                                                                                                                                                                                                                         | nal. This bi | t This bit d<br>it is used in |       |       |       |       |       |

| Bit [1] | R/W      | MOSI  | Master Output / Slave Input This bit drives<br>the serial data output signal This bit is used<br>in Manual Mode only                                                                                                                                                                                                                                    |              |                               |       |       |       |       |       |

| Bit [0] | R/W      | MISO  |                                                                                                                                                                                                                                                                                                                                                         |              | e Output T<br>al data inpu    |       | ms    |       |       |       |

Figure 4.5. SPI Interface Manual Register

configuration register of the LM97600 ADC to work in Quad-mode.

4.4.3. Synchronization Request. The DUT which is the LM97600 and the Main Board were ready for data to be captured on all the 4 channels, however the FPGA SERDES Receiver has to be configured before the data being captured is considered valid. The synchronization is required when switching between internal and external clocking or when the frequency is changed. Synchronization will cause the GTX Receivers in the FPGA to be configured for the data rate that is set. This synchronization request must be performed before the start of data capture which would otherwise result in invalid data being captured by the FPGA. The Synchronization Control Register is shown in Figure 4.6

| Address              | Register | Reset | Bit 7                                                               | Bit 6                                                                                                                                                                                                            | Bit 5                                                     | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------------|----------|-------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------|-------|-------|-------|-------|

| 0x <mark>D0A1</mark> | SYNC_CTL | 8'h00 | SYNC                                                                | EXT                                                                                                                                                                                                              |                                                           | DELAY |       | PS    |       |       |

| Bit [7]              | R/W      | SYNC  | Sync pulse will be asserted and then this bit will be self cleared. |                                                                                                                                                                                                                  |                                                           |       |       |       |       |       |

| Bit [6]              | R/W      | EXT   | Setting EXT will set the pulse to a static high level.              |                                                                                                                                                                                                                  |                                                           |       |       |       |       |       |

| Bit [5:3]            | R/W      | DELAY | setting to<br>delays. D<br>selection<br>Effective                   | Sync pulse has a delay compensation<br>g to compensate for FPGA routing<br>s. Delay will influence the phase shift<br>ion by advancing the phase shift.<br>tive phase shift is determined by<br>0] - DELAY[2:0]. |                                                           |       |       |       |       |       |

| Bit [2:0]            | R/W      | PS    |                                                                     | ed by PS[2                                                                                                                                                                                                       | ulse phase shift setting is<br>by PS[2:0] as shown in the |       |       |       |       |       |

Figure 4.6. Synchronization Control Register

The synchronization is performed by performing two register modifications in the FPGA those of which have been shown in the figures. The EXT bit of the Synchronization Control Register needs to be asserted for the synchronization request to initiate and the EXT bit is automatically reset after the synchronization.

The second register that is modified is the GTX Reset Register which resets the GTX transceiver logic as well as the buffer of the transceiver by asserting the lowest 2 bits of the register sequentially.

The *WvNewestHardwareWrite* API is used to manipulate the registers of the FPGA by setting the addresses and the values to be written to them. While the synchronization request is completed at this stage, verification needs to be performed to confirm that the synchronization request is completed. This is performed by the ChanByteAlign routine.

**4.4.4. Channel and Byte Alignment.** The Byte and Channel Alignment routine is performed to verify that the synchronization request is completed successfully. This is done by reading the byte alignment registers and the channel alignment

| A1ddress | Register | Reset    | Bit 7                                                                                                                                                        | Bit 6                   | Bit 5                                                | Bit 4       | Bit 3 | Bit 2 | Bit 1  | Bit 0    |

|----------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------|-------------|-------|-------|--------|----------|

| 0xD0F7   | GTX_RST  | 8'h00    | -                                                                                                                                                            | -                       | -                                                    | -           | -     | -     | RX_RST | BUFF_RST |

| Bit [1]  | R/W      | RX_RST   | transcei<br>clear aft                                                                                                                                        | ver Rx lo<br>er the res | ill reset th<br>gic. This<br>et is assen<br>modules. | bit will se |       |       |        |          |

| Bit [0]  | R/W      | BUFF_RST | Setting this bit will reset the<br>transceiver elastic buffer. This bit<br>will self clear after the reset is<br>asserted to the GTX transceiver<br>modules. |                         |                                                      |             |       |       |        |          |

Figure 4.7. GTX Reset Register

registers as illustrated in the figures. The lower 5 bits of the byte alignment registers and the lower 5 bits of the channel alignment registers are all set if the synchronization request is completed successfully.