# Scholars' Mine

**Masters Theses**

Student Theses and Dissertations

Spring 2012

# Sputter deposition of thin-film capacitors onto low temperature co-fired ceramic substrates

Jack Murray

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Ceramic Materials Commons

Department:

#### **Recommended Citation**

Murray, Jack, "Sputter deposition of thin-film capacitors onto low temperature co-fired ceramic substrates" (2012). Masters Theses. 5294.

https://scholarsmine.mst.edu/masters\_theses/5294

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# SPUTTER DEPOSITION OF THIN-FILM CAPACITORS ONTO LOW TEMPERATURE CO-FIRED CERAMIC SUBSTRATES

by

## JACK EDWIN MURRAY

## A THESIS

Presented to the Faculty of the Graduate School of the MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

MASTER OF SCIENCE IN CERAMIC ENGINEERING

2012

Approved by

Wayne Huebner, Advisor Matthew J. O'Keefe, Co-Advisor Robert W. Schwartz

## **PUBLICATION THESIS OPTION**

This thesis has been prepared with three papers for publication. A general introduction is given on pages 1-15. The first paper was accepted for publication in the Proceedings of the 2011 International Symposium on Microelectronics and is located on pages 16-29. The second paper was submitted to Materials Letters and is located on pages 30-38. The third paper will be submitted to Thin Solid Films and is located on pages 39-55.

#### **ABSTRACT**

Single layer thin film capacitor structures were fabricated on the surface of low temperature co-fired ceramic (LTCC) substrates using sputter deposition. The capacitor structures had areas between  $\sim 10^4 \, \mu \text{m}^2$  to  $\sim 10^6 \, \mu \text{m}^2$  and featured  $\sim 200 \, \text{nm}$  Al or Pt electrodes with 150-1500 nm Al<sub>2</sub>O<sub>3</sub> dielectric layers. Impedance analysis and currentvoltage testing were carried out to determine the effect of electrode material and dielectric thickness upon capacitor performance. Capacitance values for devices with Al electrodes ranged from ~10 to ~700 pF, depending on capacitor area and dielectric thickness, and the fit to expected values was better than devices with Pt or mixed (one Al, one Pt) electrodes. Dielectric loss increased with increasing Al<sub>2</sub>O<sub>3</sub> thickness, most likely due to cracking in thick (>1 μm) sputtered films. All measured loss values for the sputter deposited  $Al_2O_3$  (tan $\delta \sim 0.02$ ) were greater than bulk  $Al_2O_3$  (tan $\delta \sim 0.001$ ). Transmission electron microscopy (TEM) and energy dispersive spectroscopy (EDS) were utilized to examine selected capacitor structures. Electron beam induced crystallization of amorphous Al<sub>2</sub>O<sub>3</sub> was observed during the selected area diffraction (SAD) patterns. TEM examination and impedance analysis both confirm that functional capacitors with Al electrodes and 300 – 1000 nm thick Al<sub>2</sub>O<sub>3</sub> dielectric layers can be fabricated on LTCC substrates using sputter deposition.

#### ACKNOWLEDGMENTS

I am very grateful for the guidance and support of my advisor Dr. Wayne Huebner and co-advisor Dr. Matthew J. O'Keefe. Without their patience and timely advice I would not be as prepared to enter the workforce as I am today. I would also like to thank Dr. Robert Schwartz for being a committee member and an interested supporter throughout my time in the department. The experience I have gained working with Drs. Huebner and O'Keefe in microelectronics will help me greatly in future career endeavors.

I would also like to thank my colleagues who helped along the way in all of my research endeavors. Dr. Travis McKindra provided invaluable experience and patient explanation of all things related to sputter deposition. Kristina Wilder provided experimental help along the way as well. Ron Haas was a great help in maintaining the sputter system throughout my time working in the MRC. I would like to thank Honeywell FM&T for generous financial support.

My family and friends have been very supportive during my college career, making the good times better and helping through the hard times. I dedicate this thesis to them.

# TABLE OF CONTENTS

|                                                                                            | Page |

|--------------------------------------------------------------------------------------------|------|

| PUBLICATION THESIS OPTION                                                                  | iii  |

| ABSTRACT                                                                                   | iv   |

| ACKNOWLEDGMENTS                                                                            | v    |

| LIST OF ILLUSTRATIONS                                                                      | viii |

| LIST OF TABLES                                                                             | X    |

| SECTION                                                                                    |      |

| 1. INTRODUCTION                                                                            | 1    |

| 1.1. LOW TEMPERATURE CO-FIRED CERAMIC SUBSTRATES                                           | 1    |

| 1.2. SPUTTER DEPOSITION                                                                    | 2    |

| 1.3. Al <sub>2</sub> O <sub>3</sub> DIELECTRIC                                             | 4    |

| 1.4. THIN FILM MIM CAPACITORS                                                              | 8    |

| 1.5. RESEARCH DIRECTION                                                                    | 10   |

| 1.6. REFERENCES                                                                            | 11   |

| PAPER                                                                                      |      |

| 1. SPUTTER DEPOSITION OF THIN FILM MIM CAPACITORS FOR RF BYPASS AND FILTERING APPLICATIONS | 16   |

| 1.1. INTRODUCTION                                                                          | 17   |

| 1.2. EXPERIMENTAL                                                                          | 17   |

| 1.3. RESULTS AND DISCUSSION                                                                | 21   |

| 1.3.1. Low Frequency and DC Testing                                                        | 21   |

| 1.3.2. High Frequency Testing                                                              | 22   |

| 1.4. CONCLUSIONS                                                                           | 23   |

| 1.5. REFERENCES                                                                            | 29   |

| 2. ELECTRON BEAM INDUCED CRYSTALLIZATION OF SPUTTER DEPOSITED AMORPHOUS ALUMINA THIN FILMS | 30   |

| 2.1. INTRODUCTION                                                                          | 30   |

| 2.2. EXPERIMENTAL                                                                          | 31   |

| 2.3. RESULTS AND DISCUSSION                                                                | 32   |

| 2.4. CONCLUSIONS                                                                           | 35   |

| 2.5. REFERENCES                                                                                                  | 37 |

|------------------------------------------------------------------------------------------------------------------|----|

| 3. EFFECT OF ELECTRODE MATERIAL AND DIELECTRIC THICKNESS ON THE PERFORMANCE OF SPUTTER DEPOSITED NANO CAPACITORS | 39 |

| 3.1. INTRODUCTION                                                                                                | 39 |

| 3.2. EXPERIMENTAL PROCEDURE                                                                                      | 41 |

| 3.3. RESULTS AND DISCUSSION                                                                                      | 42 |

| 3.3.1. TEM Examination                                                                                           | 42 |

| 3.3.2. Electrical Testing                                                                                        | 43 |

| 3.4. CONCLUSIONS                                                                                                 | 47 |

| 3.5. REFERENCES                                                                                                  | 48 |

| SECTION                                                                                                          |    |

| 2. CONCLUSION                                                                                                    | 56 |

| VITA                                                                                                             | 57 |

# LIST OF ILLUSTRATIONS

| Fig  | ure Page                                                                                                                                                                                                                                                                                           |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT  | TRODUCTION                                                                                                                                                                                                                                                                                         |

| 1.1. | Example LTCC multilayer structure with embedded electronic devices. [3] The entire LTCC system is mounted on a printed circuit board (PCB)                                                                                                                                                         |

| 1.2. | Schematic of physical sputtering process at the sputtering target. [13]                                                                                                                                                                                                                            |

| 1.3. | Crystal structure of Al <sub>2</sub> O <sub>3</sub> in a hexagonal arrangement with trigonal unit cell highlighted with dashed lines. [17]                                                                                                                                                         |

| 1.4. | Example MIM capacitor layout with W and TiN electrodes and alumina Al <sub>2</sub> O <sub>3</sub> dielectric layers. [46]                                                                                                                                                                          |

| PA   | PER 1                                                                                                                                                                                                                                                                                              |

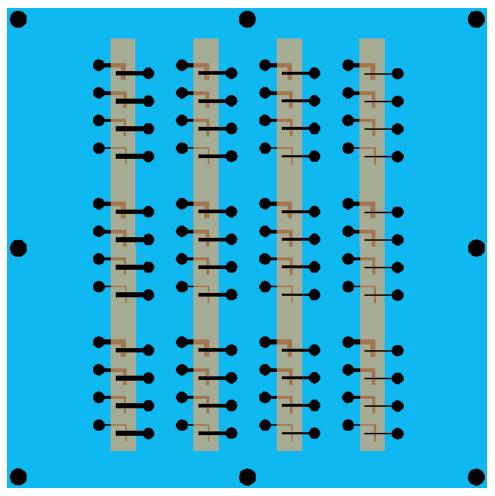

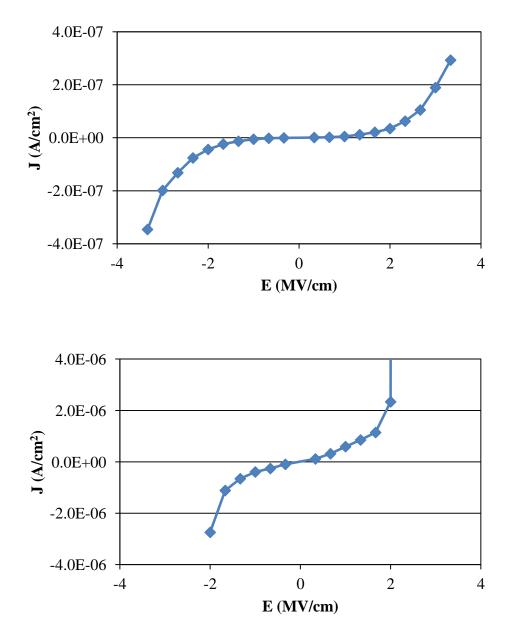

| 1.1. | Design of LTCC substrates featuring thin film capacitors made for low frequency testing. The first metal layer is shown in black, the second layer (dielectric) is tan, and the third layer (metal 2) is black                                                                                     |

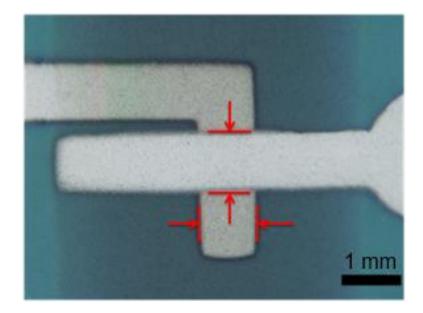

| 1.2. | Optical micrograph of individual capacitors. The red dimensions indicate where measurements were taken using ImageJ. The top image is of a capacitor that was tested at low frequency. The bottom image is an example of the capacitors that were tested with a high frequency 3-point probe setup |

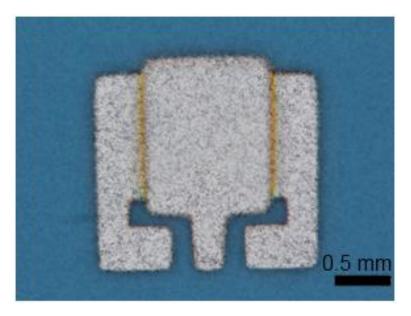

| 1.3. | Electric field vs current density for capacitors with areas of $5x10^{-3}$ cm <sup>2</sup> (top) and $8x10^{-3}$ cm <sup>2</sup> (bottom).                                                                                                                                                         |

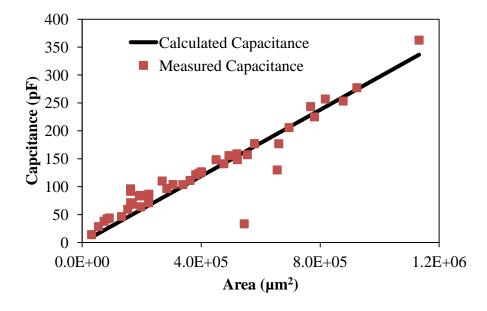

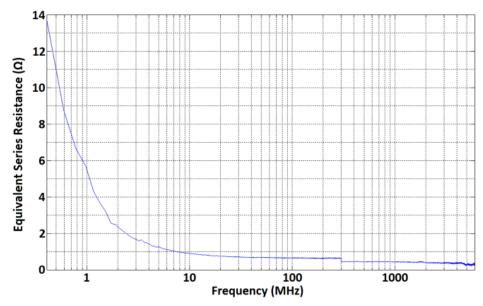

| 1.4. | Capacitance vs. area (top) and loss vs. area (bottom) for the low frequency test devices                                                                                                                                                                                                           |

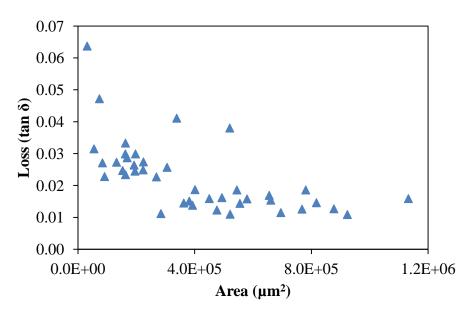

| 1.5. | Top Smith chart is raw measurement (a). Lower chart (b) shows measured impedance after de-embedding of LR interconnect parasitics                                                                                                                                                                  |

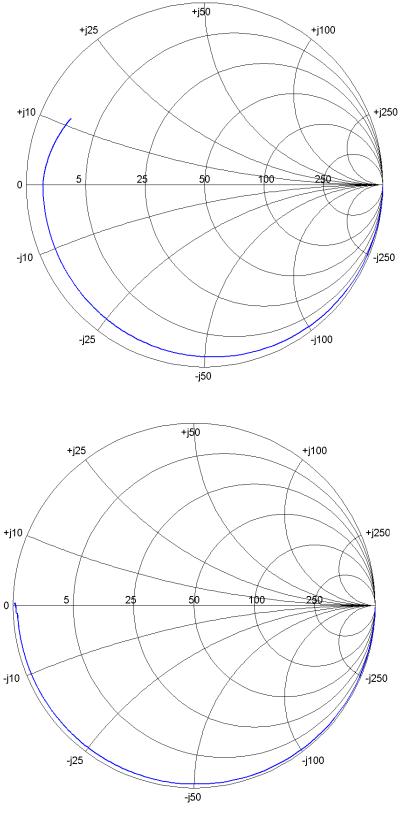

| 1.6. | Equivalent series resistance (ESR) versus frequency for the 1.0x10 <sup>-2</sup> cm <sup>2</sup> capacitor                                                                                                                                                                                         |

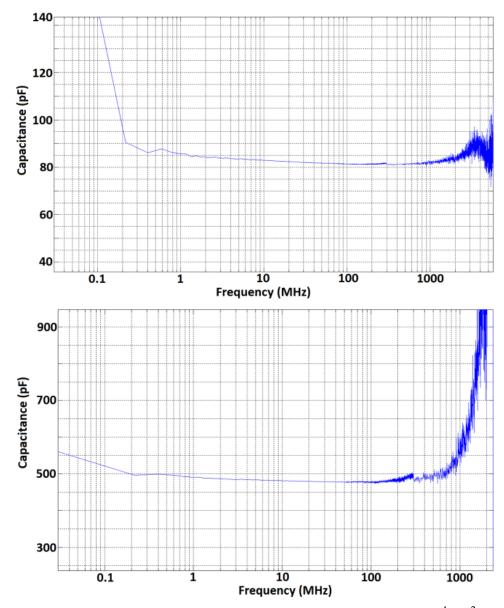

| 1.7. | Capacitance vs. frequency for capacitors with areas of $6.5 \times 10^{-4}$ cm <sup>2</sup> (top) and $1.0 \times 10^{-2}$ cm <sup>2</sup> (bottom).                                                                                                                                               |

| PAl  | PER 2                                                                                                                                                                                                                                                                                              |

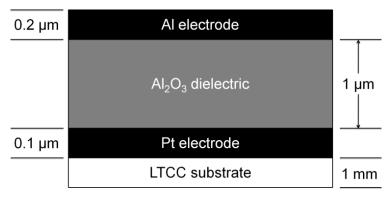

| 2.1. | Schematic of the thin film capacitor layout used in this study, with approximate layer thicknesses                                                                                                                                                                                                 |

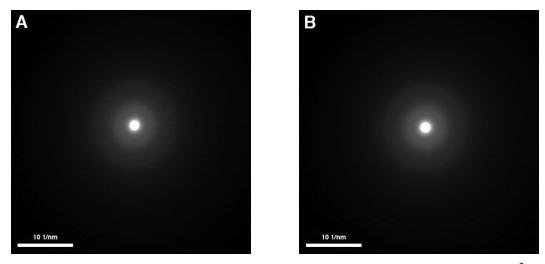

| 2.2. | SAD patterns from Al <sub>2</sub> O <sub>3</sub> thin film using a beam current of 1.7 A/cm <sup>2</sup> : a) initially and b) after 10 minutes                                                                                                                                                    |

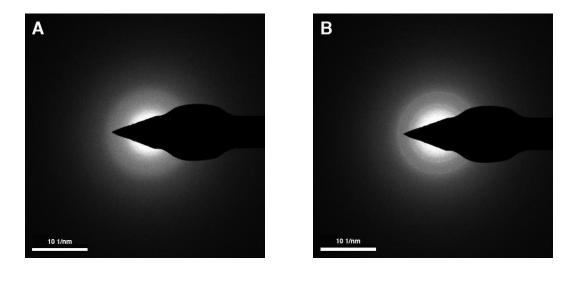

| 2.3. SAD patterns from Al <sub>2</sub> O <sub>3</sub> thin film: a) 13.0 A/cm <sup>2</sup> initially, b) after 2 minutes, and c) after 16 minutes.                                                                                                                                                                                                                                                                                                                                                                                                              | 34       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.4. TEM micrographs illustrating crystallized Al <sub>2</sub> O <sub>3</sub> : a) bright-field overview of crystallized area and b) dark-field detail of crystallized area after 16 minutes of electron beam exposure.                                                                                                                                                                                                                                                                                                                                         |          |

| PAPER 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

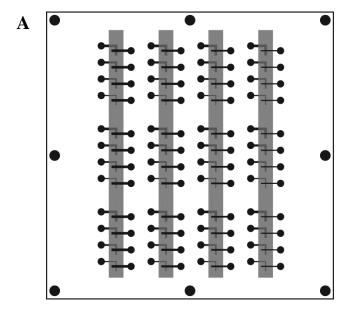

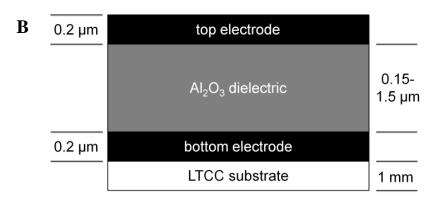

| 3.1. Diagrams of (a) capacitors on LTCC substrate, and (b) cross section of an example capacitor showing approximate layer thicknesses.                                                                                                                                                                                                                                                                                                                                                                                                                         | 50       |

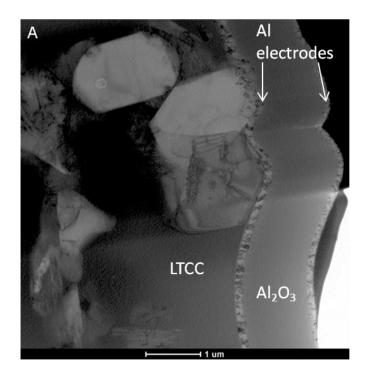

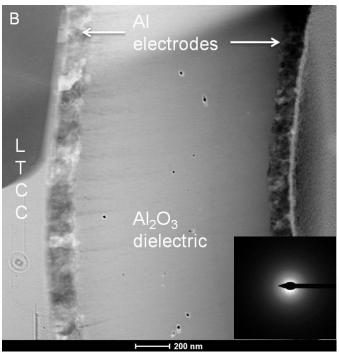

| 3.2. Al-Al <sub>2</sub> O <sub>3</sub> -Al capacitor, (a) TEM bright field overview and (b) STEM detail images with a CBED pattern from the amorphous Al <sub>2</sub> O <sub>3</sub> region                                                                                                                                                                                                                                                                                                                                                                     | 51       |

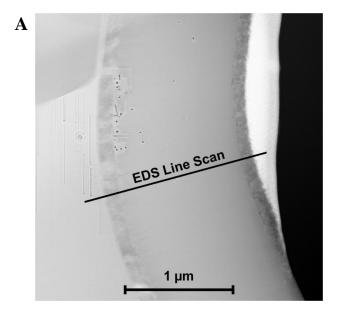

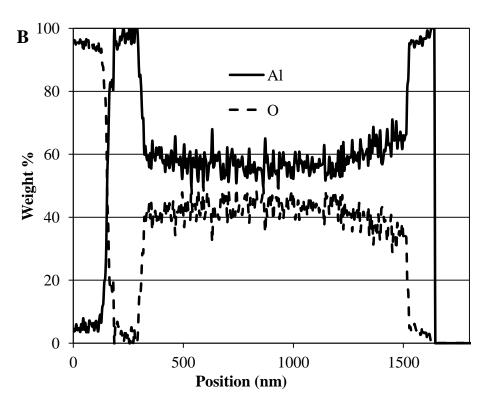

| 3.3. TEM image (a) illustrating the line scanned by EDS and the atomic map (b) of Al and O in the capacitor structure.                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

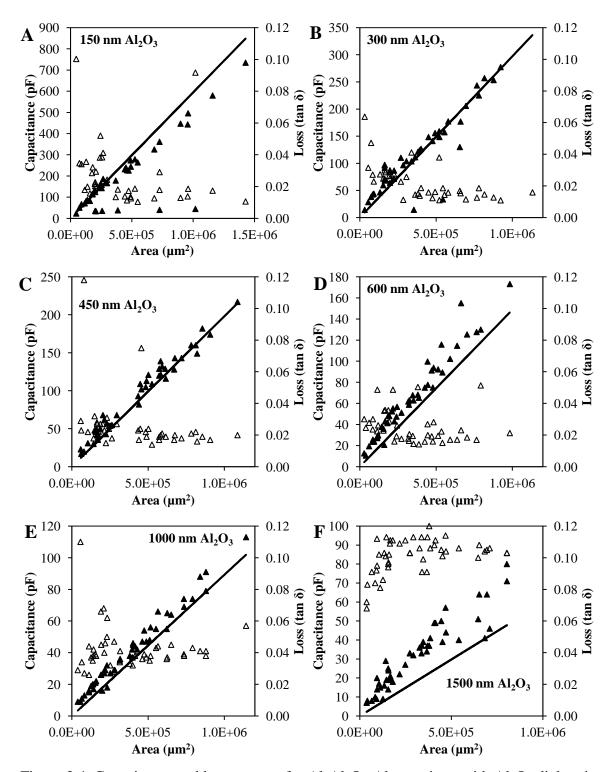

| 3.4. Capacitance and loss vs. area for Al-Al <sub>2</sub> O <sub>3</sub> -Al capacitors with Al <sub>2</sub> O <sub>3</sub> dielectric thicknesses of (a) 150 nm, (b) 300 nm, (c) 450 nm, (d) 600 nm, (e) 1000 nm, an (f) 1500 nm. Closed triangles represent capacitance, open triangles represent loand lines represent the calculated capacitance. Note the capacitance scale differences between each plot.                                                                                                                                                 | OSS      |

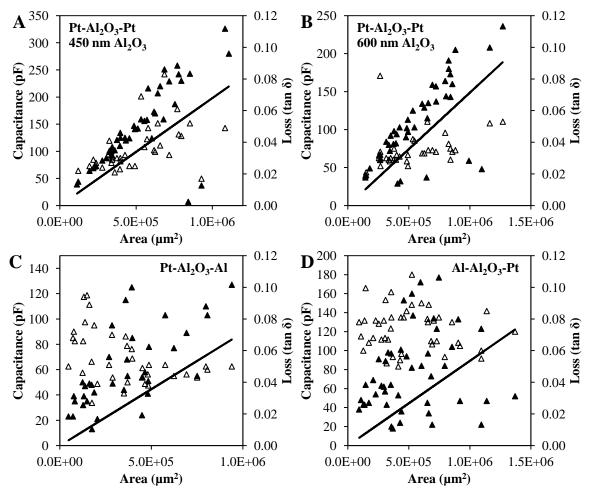

| 3.5. Capacitance and loss vs. area for Pt-Al <sub>2</sub> O <sub>3</sub> -Pt capacitors with Al <sub>2</sub> O <sub>3</sub> dielectric thicknesses of (a) 450 nm and (b) 600 nm. Dissimilar metal electrodes were use with configurations of Pt-Al <sub>2</sub> O <sub>3</sub> -Al (c) and Al-Al <sub>2</sub> O <sub>3</sub> -Pt (d) and dielectric thicknesses of and 1000 nm. Closed triangles represent capacitance, open triangles represent loss and lines represent the calculated capacitance. Note the capacitance scale differences between each plot. | <b>;</b> |

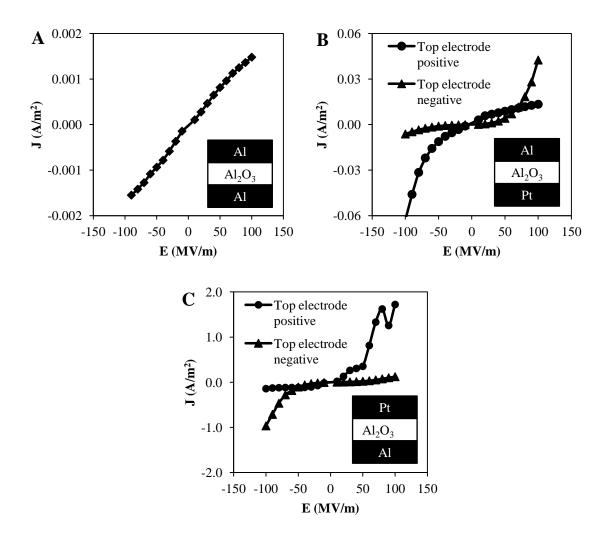

| 3.6. Electric field vs. current density for capacitors with 1 μm Al <sub>2</sub> O <sub>3</sub> dielectric layer and (a) Al-Al <sub>2</sub> O <sub>3</sub> -Al layout, (b) Pt-Al <sub>2</sub> O <sub>3</sub> -Al layout and (c) Al-Al <sub>2</sub> O <sub>3</sub> -Pt layout.                                                                                                                                                                                                                                                                                   |          |

# LIST OF TABLES

| Table                                                                    | Page |

|--------------------------------------------------------------------------|------|

| PAPER I                                                                  |      |

| 1.1. Temperature coefficient of capacitance for 3-point probe capacitors | 29   |

#### 1. INTRODUCTION

#### 1.1. LOW TEMPERATURE CO-FIRED CERAMIC SUBSTRATES

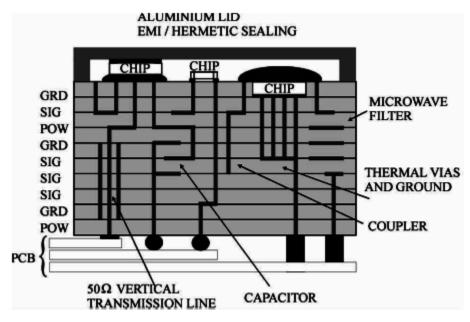

Low temperature co-fired ceramics (LTCCs) are made up of multiple layers of tape cast ceramics, often with additions of low melting point (<900 °C) glass. Uses for LTCC technology include microfluidic [1] and microelectronic [2-6] applications. For microelectronic applications LTCC technology is used as an alternative to traditional printed circuit board technology, where passive circuit elements can be integrated between layers with connecting layers of conductive materials. An example of an LTCC system is shown in Figure 1.1. The circuit elements and systems illustrated in Figure 1.1 include hermetically-sealed surface-mounted chips, integrated capacitors, and metallic interconnects.

Figure 1.1. Example LTCC multilayer structure with embedded electronic devices. [3] The entire LTCC system is mounted on a printed circuit board (PCB).

A variety of compositions exist for LTCC materials [7], but most are made up of a ceramic, such as  $Al_2O_3$  or cordierite, with fluxing oxides and low melting temperature glasses. The firing temperature must be less than the melting point of any conductive materials used in the full LTCC system, which is usually ~950 °C. Any of the substrate materials used in LTCC applications must possess satisfactory electrical properties for high frequency (100 MHz to 300 GHz) operation, including low loss and a non-dispersive permittivity. The conductive materials in LTCC systems consist of pastes of metallic conductors that are fired with the ceramic substrate. Common metals in LTCC systems are Cu, Ag, and Au, or their alloys [8] due to their high melting point (1085, 961, and 1064°C respectively [9]) and low resistivity (1.7, 1.6, and 2.3x10<sup>-8</sup>  $\Omega$  m respectively [10]). Pastes are formed by dispersing metal powder into organic binders. Full sintering of the paste leaves behind a connected system of metal particles or a non-porous metal layer, depending on the paste composition.

After an LTCC system is laminated, the resulting stack (ceramic layers and conductive paste) is fired in one step. Care must be taken to pick materials with similar thermal expansion coefficients and sintering kinetics, as well as low chemical reactivity. Deformation during co-firing, resulting in warped packages, is not uncommon and much of the research effort in LTCC technology is focused on alleviating this concern. Methods have been developed to measure the camber or warpage of LTCC systems during firing [11], which help with understanding the different sintering kinetics of conductive paste and ceramic constituents. The surface roughness of LTCC substrates is  $\sim 1 \mu m$  [8] which is much higher than atomically smooth Si substrates used in other areas of microelectronics. Recent efforts have also focused on eliminating glass from LTCC compositions due to the poor performance of most glasses at high frequencies, as well as possible reactions with metal phases [4, 5].

#### 1.2. SPUTTER DEPOSITION

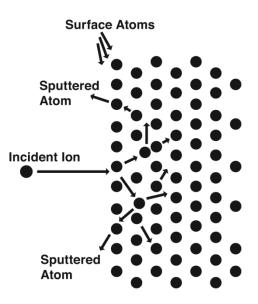

Sputter deposition is a physical vapor deposition (PVD) technique where a solid target material is deposited as a solid onto a substrate under high vacuum. Sputtering is considered a physical, rather than chemical, process because the material does not typically undergo any chemical composition changes during deposition. During

sputtering, incident atoms, usually ions, strike the surface of the target material. If the incident atoms have sufficient energy they will cause the ejection of target atoms after colliding with the surface. The process is illustrated in Figure 1.2. Most sputter systems supply the incident ions in the form of a plasma and attract the ions with voltage applied to the target which is located at the cathode. The substrate and chamber are grounded, to ensure safe operation. Atoms are ejected from the surface of the target and deposited throughout the vacuum chamber in a line of site direction [12].

Figure 1.2. Schematic of physical sputtering process at the sputtering target. [13]

The steps in the sputter deposition process are evacuation of the vacuum chamber, backfill with working gas, ignite the plasma, clean the target, and finally deposit material. Sputtering must take place in ultra high vacuum conditions to ensure that the mean free path of sputtered atoms is sufficient to travel from the target to the substrate [14]. The working gas, usually Ar or Ne, is ionized to create the plasma. Higher sputter yield is realized with higher mass gases, so Ar is the most widely used working gas [14]. The

working gas is ionized by applying a large voltage to it. A DC or RF power supply applies the voltage to the cathode, depending on the material to be deposited. A wide variety of materials can be sputtered, including metals, insulators and semiconductors. Typically DC sputtering is used to deposit metals and RF (13.56 MHz) sputtering is used to deposit insulators.

## 1.3. Al<sub>2</sub>O<sub>3</sub> DIELECTRIC

Several characteristics of aluminum oxide ( $Al_2O_3$ ) are important to understand to allow for effective use in dielectric applications. The crystal structure of  $Al_2O_3$  plays a part in many of its properties and varies depending on processing characteristics, such as temperature and deposition technique. Other structural characteristics include the defects and stoichiometry deviations that result from various processing techniques. Also useful is an understanding of the electrical properties of  $Al_2O_3$ , including dielectric constant, band gap, resistivity, and dielectric breakdown strength, and their variation depending on structure and processing. Various electrical phenomena occur at different thicknesses of  $Al_2O_3$  films and must be accounted for when their use is desired for a specific application. This section highlights these characteristics.

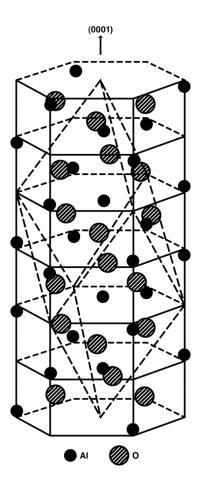

In normal bulk conditions  $Al_2O_3$  is a crystalline material ( $\alpha$ - $Al_2O_3$ ) with a trigonal crystal structure and a space group of  $3 \frac{2}{m}$  [15]. Figure 1.3 shows the crystal structure of  $\alpha$ - $Al_2O_3$  in a hexagonal arrangement, with the trigonal unit cell outlined in dashed lines. Many polymorphs of  $Al_2O_3$  exist at different temperatures and are formed from different processing conditions [16]. When thin films of  $Al_2O_3$  are deposited, they are often arranged in amorphous or nanocrystalline structures.

The electrical properties of  $Al_2O_3$  are sufficient for use as a dielectric or insulating material in a variety of applications. Pure  $\alpha$ - $Al_2O_3$  exhibits a non-dispersive dielectric constant, K, of 10 [18]. Only the electronic and ionic polaraization mechanisms are active, contributing ~30% and 70% of the overall K. Relative to other ceramic capacitor materials, such as  $TiO_2$  or  $BaTiO_3$ ,  $Al_2O_3$  is considered a low-K material [19] but in Si microelectronic applications where  $Al_2O_3$  would replace  $SiO_2$  or  $Si_3N_4$  it is considered a high-K dielectric [20]. The band gap of  $Al_2O_3$  is 6.31 eV [17] which makes it an electrical insulator. In fact, 99.9% pure  $Al_2O_3$  features exceptional electrical resistivity

$(1x10^{13} \Omega \text{ m})$  which degrades when impurities are present [19]. Thin films of  $Al_2O_3$  feature high dielectric breakdown strengths, often in the range of several MV/cm [31, 33, 34].

Figure 1.3. Crystal structure of  $Al_2O_3$  in a hexagonal arrangement with trigonal unit cell highlighted with dashed lines. [17]

Two main thickness regimes of  $Al_2O_3$  thin films have been studied since the late 1960's. The thinnest films are tens of nm thick. In early examples these films were fabricated by evaporation from solid  $Al_2O_3$  sources [21, 22], or were oxidized from Al by

thermal or anodic methods [23, 24]. Later, Al<sub>2</sub>O<sub>3</sub> films of similar thicknesses were deposited by RF magnetron sputtering [25, 26] or pulsed laser deposition (PLD) [27]. Current research into replacements for SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> in metal-insulator-metal (MIM) capacitors for Si microelectronics also involves Al<sub>2</sub>O<sub>3</sub> films tens of nanometers thick, discussed further below. Thicker Al<sub>2</sub>O<sub>3</sub> films, with thicknesses in the hundreds of nm, have been deposited by anodic oxidation of Al [28] or evaporation [29], but the vast majority have been synthesized by sputter deposition [30-34].

Films of Al<sub>2</sub>O<sub>3</sub> with thicknesses around 10 nm exhibit unique characteristics that are not measured (or observed) at greater thicknesses. Antula [21] examined an apparent positive ionic space charge in Al<sub>2</sub>O<sub>3</sub> films between 6 and 34 nm thick. Films were deposited by the evaporation of Al in an O<sub>2</sub> atmosphere, yielding Al<sub>2</sub>O<sub>3</sub>. After deposition the films were aged in atmospheric pressure at temperatures from 150-200°C and times between 2 and 6 hours. Current-voltage testing indicated an ionic space charge in the Al<sub>2</sub>O<sub>3</sub> that disappeared after aging. Birey [22] examined the dielectric properties of Al<sub>2</sub>O<sub>3</sub> films between 6 and 1000 nm in thickness. The Al<sub>2</sub>O<sub>3</sub> films were again deposited by the evaporation of Al in an  $O_2$  atmosphere. The resultant dielectric loss was exceptionally high for the capacitors, with values between 10 and 60%. The anomalous results from both of these studies can be attributed to the use of reactive evaporation as the deposition method. Pinholes, low density and high residual film stress are common defects of reactive evaporated films due to the limited control over processing parameters [35]. The positive ionic space charge [21] can be attributed to the migration of Al ions into the porous Al<sub>2</sub>O<sub>3</sub> layer and high dielectric loss [22] is most likely due to defects in the  $Al_2O_3$  film from processing.

Voltage-controlled negative resistance (VCNR) was detected in thermally and anodically oxidized Al<sub>2</sub>O<sub>3</sub> films less than 10 nm thick by Dittmer [24]. Similar results were found by Rahman et al. [25] in sputter deposited Al<sub>2</sub>O<sub>3</sub> films around 10 nm in thickness. VCNR occurs when the applied voltage leads to a current response opposite what is implied by Ohm's Law, negative current slope with increasing voltage, for example. In both cases, the Al<sub>2</sub>O<sub>3</sub> films were part of a sandwich structure with an Al bottom electrode and a Au top electrode. In the first case [24], multilayer Al<sub>2</sub>O<sub>3</sub> films fabricated using multiple deposition methods had properties such as porosity that differed

between successive layers. VCNR was thought to occur because of Al rich regions in the Al<sub>2</sub>O<sub>3</sub> films as well as Au precipitates in porous Al<sub>2</sub>O<sub>3</sub>. The complex electronic structure resulting from the non-stoichiometric films obscures the actual mechanism for VCNR. Further confusing the issue are the results from Rahman et al. [25] which only observed VCNR in Al-Al<sub>2</sub>O<sub>3</sub>-Au structures below pressures of 0.1 Torr. The study featured sputter deposited Al<sub>2</sub>O<sub>3</sub> films which are far less porous than the thermally and anodically oxidized films studied by Dittmer, which should lead to a more easily understood electronic structure. No explanation was offered for the pressure dependence of VCNR. Partial dielectric breakdown is now thought to be the cause of VCNR in Al-Al<sub>2</sub>O<sub>3</sub>-Au structures. Hickmott [36] proposed that conducting channels develop in the Al<sub>2</sub>O<sub>3</sub> and these contribute to a positive charge region at the Al-Al<sub>2</sub>O<sub>3</sub> interface. Voltages above a certain threshold overcome the positive charge and result in decreasing electric current.

Both reactive and direct sputter deposition of Al<sub>2</sub>O<sub>3</sub> films with thicknesses in the hundreds of nanometers have been utilized for microelectronic applications. Yip et al. [34] investigated the effect of different top electrodes on the dielectric strength of Al-Al<sub>2</sub>O<sub>3</sub>-x capacitor structures where x was either Al, Au, Ni, Cu, or Ag. In all electrical testing the bottom Al electrode was the cathode. Devices with an Al top electrode featured the highest dielectric strength (4.5 MV/cm) with decreasing strength for each of the other top electrode materials. Electric field enhanced diffusion of the electrode materials into the RF sputter deposited Al<sub>2</sub>O<sub>3</sub> layer is thought to cause the differing dielectric strengths of the devices. Also, the addition of an Al layer between the dielectric and the top electrode increased the dielectric strength by acting as a diffusion barrier. Although it is supposed that there are open sites and defects in amorphous Al<sub>2</sub>O<sub>3</sub> structures that allow for easier diffusion, there is no estimate of the reduction in diffusion energy required. Furthermore, dielectric strength was tested at room temperature while diffusion rates were listed at 1473 K with no estimate of the increased diffusion energy provided by the applied electric field.

Several studies have been carried out to investigate the effect of oxygen addition and sputtering pressure during the RF sputtering of  $Al_2O_3$ . Segda et al. [31] found that  $Al_2O_3$  films with the stoichiometry closest to ideal were deposited by RF sputtering in a pure Ar atmosphere. The addition of  $O_2$  led to oxygen-rich films with atomic ratios of up

to  $Al_2O_{3.50}$ , as measured by X-ray fluorescence. Greater sputter pressure (1.0 Pa, as opposed to 0.1 Pa) led to less Ar incorporation in the  $Al_2O_3$  films due to the reduced mean free path of the Ar atoms with higher pressure. Increasing sputter power was found to reduce the molar fraction of Ar in the resulting  $Al_2O_3$  films. Similar results were found by Voigt et al. [33] who determined that the  $Al_2O_3$  films with the highest breakdown fields (~2.5 MV/cm) were deposited by RF sputter deposition in a pure Ar environment. A further requirement for satisfactory films is the "conditioning" of the  $Al_2O_3$  target by sputtering in a mixed  $Ar/O_2$  atmosphere prior to deposition.

#### 1.4. THIN FILM MIM CAPACITORS

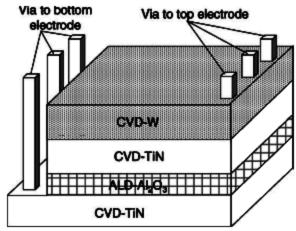

A thin film capacitor is made up of electrode and dielectric layers usually less than several micrometers thick. When the capacitor is arranged in a stack with a bottom electrode layer, a single dielectric layer, and a top electrode layer (or layers) it is known as a metal-insulator-metal (MIM) capacitor. Capacitors arranged in the MIM layout are used for energy storage [37], dynamic random access memory (DRAM) [38-40], and radio frequency (RF) and mixed signal integrated circuits [41-50]. Commonly the dielectric thickness ranges from several nanometers to several hundreds of nanometers, depending on the application. A representative MIM capacitor structure is shown in Figure 1.4, with TiN and W electrodes, Al<sub>2</sub>O<sub>3</sub> dielectric layer and via structures visible. MIM capacitors are fabricated using a variety of chemical vapor deposition techniques such as plasma enhanced chemical vapor deposition (PECVD) [41] and atomic layer deposition (ALD) [37-40, 42, 46, 48, 49, 51-53]. Physical vapor deposition techniques such as pulsed laser deposition (PLD) [43] and sputter deposition [45, 50, 54] are also used to fabricate MIM capacitors.

The most common dielectric materials used in current MIM capacitors are oxides and nitrides of Si [41-47], which are cost effective and straightforward to fabricate on Si surfaces. A drawback of using these materials is their low dielectric constant (3.0 for SiO<sub>2</sub> and 7.5 for Si<sub>3</sub>N<sub>4</sub>). Constant miniaturization of devices has led to a desire for thinner dielectric layers. To facilitate higher capacitance with thinner dielectric layers, high-K dielectric materials have been researched for use in MIM capacitors.

Figure 1.4. Example MIM capacitor layout with W and TiN electrodes and alumina Al<sub>2</sub>O<sub>3</sub> dielectric layers. [46]

Lee et al. [38] used ALD to deposit 50 nm W bottom electrodes and 11 nm ZrO<sub>2</sub> dielectric layers for use in MIM capacitors. Top Pt electrodes were e-beam evaporated onto the surface and the resulting structures were characterized by TEM and electrical testing. A thin (~1 nm) interfacial oxide, made up of WO<sub>x</sub> with a small amount of Zr, was detected. The K value of the dielectric stack was calculated to be 22-25, which includes the ZrO<sub>2</sub> and the interfacial layer. Kim et al. [51] used ALD to deposit ZrO<sub>2</sub> dielectric layers with thicknesses of 6, 8, and 10 nm at temperatures from 225 to 275 °C. All of the dielectric layers were annealed at 400 °C after deposition to increase the crystallinity of the ZrO<sub>2</sub> films. TiN electrodes were used to created MIM structures. A K value of ~43 was obtained for the 8 nm ZrO<sub>2</sub> layer deposited at 275 °C. In both studies, crystalline films of ZrO<sub>2</sub> were deposited with one study obtaining a higher K than the commonly accepted value of 25.

$Al_2O_3$  is also a common high-K material under investigation for MIM capacitor use. Bajolet et al. [46] studied the effect of electrode post-treatment on MIM capacitors. CVD was used to deposit TiN electrodes and ALD was used to deposit a 20 nm  $Al_2O_3$  dielectric layer. When TiN is deposited by CVD the resulting films contain enough carbon to degrade the conductivity so post treatment in a  $N_2/H_2$  plasma is required to reduce the carbon content. However, post treatment of the top electrode led to nitrogen diffusion into the  $Al_2O_3$  layer, and a resultant degradation of dielectric properties,

including higher dielectric loss and higher leakage current. Meng et al. [40] used ALD exclusively to deposit similar capacitor structures, with TiN electrodes and a 5 nm Al<sub>2</sub>O<sub>3</sub> dielectric layer. Since ALD was used to deposit the electrodes, no plasma post treatment was required. TEM analysis did not show an interfacial layer between the TiN electrodes and the Al<sub>2</sub>O<sub>3</sub> dielectric layer. The lack of an interfacial layer was confirmed by capacitance calculations, assuming a dielectric constant of 9 for the Al<sub>2</sub>O<sub>3</sub> dielectric. The calculations could be improved by assuming a dielectric constant of 10 for the Al<sub>2</sub>O<sub>3</sub> dielectric. Both studies indicate the suitability of constructing MIM capacitors with ALD Al<sub>2</sub>O<sub>3</sub> dielectric films and TiN electrodes.

Another high-K dielectric material for use in MIM capacitor applications is HfO<sub>2</sub>. Hu et al. [43] used PLD to deposit HfO<sub>2</sub> onto a Ta electrode at 200 °C. Al was used as a top electrode. The dielectric constant of the HfO<sub>2</sub> in the MIM capacitor arrangement was 18 across a frequency range of 500 Hz to 1 MHz. A drawback with using pure HfO<sub>2</sub> as a dielectric material in MIM capacitors is its low crystallization temperature, which degrades the leakage current and dielectric breakdown characteristics by creating disorder at grain boundaries in addition to a volume change [42]. Zhu et al [42] got around this problem by depositing four different stack or laminate structures with alternating layers of ALD HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>. The MIM structures featured TiN electrodes and dielectric layers near 50 nm. Laminate structures with 1 nm Al<sub>2</sub>O<sub>3</sub> layers around 10 nm HfO<sub>2</sub> layers stacked up to 56 nm in total thickness had the best leakage current and dielectric breakdown characteristics of all of the tested combinations.

#### 1.5. RESEARCH DIRECTION

This work addresses the sputter deposition of thin film capacitor structures onto LTCC substrates and is divided into three sections. First, the fabrication and electrical testing of MIM capacitors with two different layouts was investigated. The capacitors were fabricated on the surface of LTCC substrates and featured 300 nm thick  $Al_2O_3$  dielectric layers with 200 nm thick Al electrodes. Electrical testing was carried out at low (DC and <15 MHz) and high (<1 GHz) frequency to characterize the resulting devices. Successful sputter deposition fabrication of thin film capacitor structures onto the rough (~1  $\mu$ m) surface of LTCC substrates was demonstrated.

Second, this work documents the electron beam induced crystallization of amorphous  $Al_2O_3$  in a capacitor structure. Crystallization occurred when capturing selected area diffraction patterns in a transmission electron microscope (TEM). The crystallized  $Al_2O_3$  region was visible in selected area diffraction patterns and subsequent TEM images. Crystal growth occurred upon further beam exposure, indicating the thermal nature of the crystallization process. This represents an opportunity to spatially modify and control the microstructure of  $Al_2O_3$ , thus affecting the properties over a nanometer scale range.

Third, this work investigates how the choice of electrode material affects thin film capacitor properties. Capacitors with Al, Pt, or both Al and Pt electrodes and  $Al_2O_3$  dielectric layers of various thicknesses were fabricated by sputter deposition and subsequently underwent electrical testing. Devices with Pt electrodes exhibited higher dielectric loss and a larger deviation from expected capacitance values than devices with Al electrodes.

#### 1.6. REFERENCES

- 1. Peterson, K.A., et al., *Novel Microsystem Applications with New Techniques in Low-Temperature Co-Fired Ceramics*. International Journal of Applied Ceramic Technology, 2005. **2**(5): p. 345-363.

- 2. Jantunen, H., et al., Compositions of MgTiO<sub>3</sub>-CaTiO<sub>3</sub> ceramic with two borosilicate glasses for LTCC technology. Journal of the European Ceramic Society, 2000. **20**: p. 2331-2336.

- 3. Jantunen, H., *Design aspects of microwave components with LTCC technique*. Journal of the European Ceramic Society, 2003. **23**(14): p. 2541-2548.

- 4. Valant, M., Glass-free low-temperature cofired ceramics: calcium germanates, silicates and tellurates. Journal of the European Ceramic Society, 2004. **24**(6): p. 1715-1719.

- 5. Subodh, G. and Sebastian, M.T., *Glass-Free Zn*<sub>2</sub>*Te*<sub>3</sub>*O*<sub>8</sub> *Microwave Ceramic for LTCC Applications*. Journal of the American Ceramic Society, 2007. **90**(7): p. 2266-2268.

- 6. Dernovsek, O., et al., *LTCC glass-ceramic composites for microwave application*. Journal of the European Ceramic Society, 2001. **21**: p. 2001.

- 7. Sebastian, M.T. and Jantunen, H., *Low loss dielectric materials for LTCC applications: a review.* International Materials Reviews, 2008. **53**(2): p. 57-90.

- 8. Imanaka, Y., *Multilayered Low Temperature Cofired Ceramics (LTCC) Technology*, 2005, New York, NY: Springer.

- 9. *Melting, Boiling, Triple, and Critical Points of the Elements*, in *CRC Handbook of Chemistry and Physics*, W.M. Hayes, Editor, 2012, CRC Press/Taylor and Francis: Boca Raton, FL.

- 10. Electrical Resistivity of Pure Metals, in CRC Handbook of Chemistry and Physics, W.M. Hayes, Editor, 2012, CRC Press/Taylor and Francis: Boca Raton, FL.

- 11. Lu, G.-Q., Sutterlin, R.C., and Gupta, T.K., Effect of Mismatched Sintering Kinetics on Camber in a Low-Temperature Cofired Ceramic Package. Journal of the American Ceramic Society, 1993. **76**(8): p. 1907-1914.

- 12. Rohde, S.L., Sputter Deposition, in Surface Engineering, 1994, ASM International.

- 13. Seshan, K., ed. *Handbook of Thin-Film Deposition Processes and Techniques*. 2 ed. 2002, Noyes Publications: Norwich, NY.

- 14. Stuart, R.V., *Vacuum Technology, Thin Films, and Sputtering: An Introduction*, 1983, New York: Academic Press.

- 15. Standards, J.C.o.P.D., *Powder diffraction file; inorganic volume,* 1972, Swarthmore, PA: Joint Committee on Powder Diffraction Standards.

- 16. Levin, I. and Brandon, D., *Metastable Alumina Polymorphs: Crystal Structures and Transition Sequences*. Journal of the American Ceramic Society, 1998. **81**(8): p. 1995-2012.

- 17. Ching, W.Y. and Xu, Y.-N., First-Principles Calculation of Electronic, Optical, and Structural Properties of α-Al<sub>2</sub>O<sub>3</sub>. Journal of the American Ceramic Society, 1994. **77**(2): p. 404-411.

- 18. Fredersikse, H.P.R., *Permittivity (Dielectric Constant) Of Inorganic Solids*, in *CRC Handbook of Chemistry and Physics*, W.M. Hayes, Editor, 2012, CRC Press/Taylor and Francis: Boca Raton, FL.

- 19. Moulson, A.J. and Herbert, J.M., *Electroceramics: Materials, Properties, Applications*, 2003, Chichester, United Kingdom: John Wiley and Sons.

- 20. Gerritsen, E., et al., Evolution of materials technology for stacked-capacitors in 65nm embedded-DRAM. Solid-State Electronics, 2005. **49**(11): p. 1767-1775.

- 21. Antula, J., Effect of Positive Ionic Space Charge on Electrical Capacitance and Schottky Current in Thin Al<sub>2</sub>O<sub>3</sub> Films. Thin Solid Films, 1969. **4**(4): p. 281-289.

- 22. Birey, H., *Dielectric properties of aluminum oxide films*. Journal of Applied Physics, 1978. **49**(5): p. 2898-2904.

- 23. Bardhan, A.R., et al., *Electron transport mechanisms in very thin*  $Al_2O_3$  *films*. International Journal of Electronics, 1976. **40**(4): p. 313-321.

- 24. Dittmer, G., Electron Conduction, Electron Emission and Electroluminescence of MIM Sandwich Structures with Al<sub>2</sub>O<sub>3</sub> Insulating Layers. Thin Solid Films, 1972. **9**(2): p. 141-172.

- 25. Rahman, A. and Raven, M.S., *Electrical Characteristics of RF-Sputtered Al*<sub>2</sub>O<sub>3</sub> *MIM Structures*. Thin Solid Films, 1980. **71**(1): p. 7-13.

- 26. Rajopadhye, N.R., Dake, S.B., and Bhoraskar, S.V., *Characterization of Al<sub>2</sub>O<sub>3</sub> films deposited by various methods*. Thin Solid Films, 1986. **142**(1): p. 127-138.

- 27. Katiyar, P., Jin, C., and Narayan, R.J., *Electrical properties of amorphous aluminum oxide thin films*. Acta Materialia, 2005. **53**(9): p. 2617-2622.

- 28. Stark, I., Stordeur, M., and Syrowatka, F., *Thermal conductivity of thin amorphous alumina films*. Thin Solid Films, 1993. **226**(1): p. 185-190.

- 29. Manaila, R., Devenyi, A., and Candet, E., *Structural order in amorphous aluminas*. Thin Solid Films, 1984. **116**(1-3): p. 289-299.

- 30. Deshpandey, C. and Holland, L., *Preparation and Properties of Al*<sub>2</sub>O<sub>3</sub> *Films by DC and RF Magnetron Sputtering*. Thin Solid Films, 1982. **96**(3): p. 265-270.

- 31. Segda, B.G., Jacquet, M., and Besse, J.P., *Elaboration, characterization and dielectric properties study of amorphous alumina thin films deposited by r.f. magnetron sputtering.* Vacuum, 2001. **62**(1): p. 27-38.

- 32. Shinzato, S., et al., *Internal Stress in Sputter-Deposited Al<sub>2</sub>O<sub>3</sub> Films*. Thin Solid Films, 1982. **97**(4): p. 333-337.

- 33. Voigt, M. and Sokolowski, M., *Electrical properties of thin rf sputtered aluminum oxide films*. Materials Science and Engineering B, 2004. **109**(1-3): p. 99-103.

- 34. Yip, G., et al., Effect of metal contacts on the electrical characteristics of  $Al_2O_3$  dielectric thin films. Applied Physics Letters, 2008. **92**(12): p. 122911.

- 35. Mattox, D.M., *Vacuum Deposition, Reactive Evaporation, and Gas Evaporation*, in *Surface Engineering*, 1994, ASM International.

- 36. Hickmott, T.W., *Temperature dependence of voltage-controlled negative resistance and electroluminescence in Al–Al<sub>2</sub>O<sub>3</sub>–Au diodes.* Journal of Applied Physics, 2008. **104**(10): p. 103704.

- 37. Banerjee, P., et al., *Nanotubular metal–insulator–metal capacitor arrays for energy storage*. Nature Nanotechnology, 2009. **4**(5): p. 292-296.

- 38. Lee, S.-Y., et al., *Atomic layer deposition of ZrO*<sub>2</sub> *on W for metal–insulator–metal capacitor application*. Applied Physics Letters, 2003. **82**(17): p. 2874.

- 39. Kim, W.D., et al., *Growth Characteristics of Atomic Layer Deposited TiO*<sub>2</sub> *Thin Films on Ru and Si Electrodes for Memory Capacitor Applications*. Journal of the Electrochemical Society, 2005. **152**(8): p. C552.

- 40. Meng, S., et al., *Leakage mechanisms and dielectric properties of Al<sub>2</sub>O<sub>3</sub>/TiN-based metal-insulator-metal capacitors*. Applied Physics Letters, 2003. **83**(21): p. 4429.

- 41. Babcock, J.A., et al., *Analog Characteristics of Metal-Insulator-Metal Capacitors Using PECVD Nitride Dielectrics*. IEEE Electron Device Letters, 2001. **22**(5): p. 230-232.

- 42. Zhu, C., Cho, B.J., and Li, M.F., *Atomic Layer Deposited High-K Films and Their Role in Metal-Insulator-Metal Capacitors for Si RF/Analog Integrated Circuit Applications*. Chemical Vapor Deposition, 2006. **12**(2-3): p. 165-171.

- 43. Hu, H., et al., A High Performanced MIM Capacitor Using HfO<sub>2</sub> Dielectrics. IEEE Electron Device Letters, 2002. **23**(9): p. 514-516.

- 44. Chen, S.B., et al., *High-Density MIM Capacitors Using Al*<sub>2</sub> $O_3$  *and AlTiO*<sub>x</sub> *Dielectrics.* IEEE Electron Device Letters, 2002. **23**(4): p. 185-187.

- 45. Tsai, K.-C., et al., *High-Reliability Ta*<sub>2</sub>*O*<sub>5</sub> *Metal—Insulator—Metal Capacitors with Cu-Based Electrodes*. Journal of The Electrochemical Society, 2006. **153**(5): p. G492.

- 46. Bajolet, A., et al., *Impact of TiN post-treatment on metal insulator metal capacitor performances*. Microelectronic Engineering, 2006. **83**(11-12): p. 2189-2194.

- 47. Ng, C.H., et al., *MIM Capacitor Integration for Mixed-Signal/RF Applications*. IEEE Transactions on Electron Devices, 2005. **52**(7): p. 1399-1409.

- 48. Hu, H., et al., MIM Capacitors Using Atomic-Layer-Deposited High-K  $(HfO_2)_{1-x}(Al_2O_3)_x$  Dielectrics. IEEE Electron Device Letters, 2003. **24**(2): p. 60-62.

- 49. Ding, S.-J., et al., *RF*, *DC*, and Reliability Characteristics of ALD HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> Laminate MIM Capacitors for Si RF IC Applications. IEEE Transactions on Electron Devices, 2004. **51**(2): p. 886-894.

- 50. Brassard, D., L. Ouellet, and M.A. El Khakani, *Room-Temperature Deposited Titanium Silicate Thin Films for MIM Capacitor Applications*. IEEE Electron Device Letters, 2007. **28**(4): p. 261-263.

- 51. Kim, J., et al., *Physical and electrical characterization of high-K ZrO*<sub>2</sub> *metal-insulator–metal capacitor*. Thin Solid Films, 2008. **516**(23): p. 8333-8336.

- 52. Baristiran Kaynak, C., et al., Single SrTiO<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub>/SrTiO<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub> based MIM capacitors: Impact of the bottom electrode material. Microelectronic Engineering, 2011. **88**(7): p. 1521-1524.

- 53. Klootwijk, J.H., et al., *Ultrahigh Capacitance Density for Multiple ALD-Grown MIM Capacitor Stacks in 3-D Silicon*. IEEE Electron Device Letters, 2008. **29**(7): p. 740-742.

- 54. Fan, W., et al., Materials science and integration bases for fabrication of  $(Ba_xSr_{1-x})TiO_3$  thin film capacitors with layered Cu-based electrodes. Journal of Applied Physics, 2003. **94**(9): p. 6192.

#### **PAPER**

## 1. SPUTTER DEPOSITION OF THIN FILM MIM CAPACITORS FOR RF BYPASS AND FILTERING APPLICATIONS

Jack Murray, Wayne Huebner, Matthew J. O'Keefe, Kristina Wilder Missouri University of Science and Technology Rolla, MO

> Ryan Eatinger, William Kuhn Kansas State University Manhattan, KS

Daniel S. Krueger, J. Ambrose Wolf Honeywell Federal Manufacturing and Technologies Kansas City, MO

(Paper published in Proceedings of the 2011 International Symposium on Microelectronics)

Keywords: LTCC, Sputter deposition, thin-film, capacitor

#### **ABSTRACT**

Thin film capacitors for RF bypass and filtering applications were sputter deposited onto low temperature co-fired ceramic (LTCC) substrates. The capacitors were configured in a metal-insulator-metal (MIM) design featuring 200 nm thick Al electrodes and a 300 nm thick Al<sub>2</sub>O<sub>3</sub> dielectric layer, with dimensions varied between ~150x150  $\mu$ m and ~750x750  $\mu$ m. DC current-voltage measurements (E  $\leq$  5 MV/cm) coupled with impedance analysis ( $\leq$ 15 MHz) was used to characterize the resulting devices. More than 90% of the devices functioned as capacitors with high DC resistance (>20 M $\Omega$ ) and low loss (tan  $\delta$  <0.1). A second set of capacitors were made under the same experimental conditions with device geometries optimized for high frequency ( $\geq$ 200 MHz) applications. These capacitors featured temperature coefficient of capacitance (TCC) values between 500 and 1000 ppm/°C as well as low loss and high self-resonant frequency performance (ESR <0.6  $\Omega$  at self-resonance of 5.7 GHz for 82 pF).

Capacitance and loss values were comparable between the capacitor structures of similar areas at the different frequency regimes.

#### 1.1. INTRODUCTION

Physical vapor deposition techniques, such as sputter deposition, offer many advantages over other techniques for thin film deposition, namely chemical vapor deposition or plating. These advantages include the ability to deposit a wide variety of materials, thickness uniformity of deposited films, and good film adhesion [1]. Due to the physical nature of the process (solid source to solid substrate), there are none of the potentially toxic by-products that are associated with other processes. Sputter deposition is also a robust process that can use a wide variety of substrate materials.

Low temperature co-fired ceramic (LTCC) substrates consist of multilayer, tape cast, ceramic and glass dielectric materials with metal interconnects and vias. Passive devices can be used on the surface of an LTCC substrate, or be integrated within internal layers and fired in one step [2, 3]. One firing step is only possible if the densification temperature of the LTCC material is less than the melting point of the metal interconnects. A variety of different compositions are under investigation for LTCC applications and many of them densify at temperatures less than the melting point of common metals such as Cu and Au [4]. Surface roughness is much greater for LTCC substrates than Si wafers (~1 µm for LTCC compared to ~1 nm for Si) but sputtering is known for conformal deposition of thin films [1]. Whether on the surface or integrated internally on a substrate, thin film capacitors offer a size advantage over surface mounted devices. In this paper two different designs of MIM capacitor structures were sputter deposited onto LTCC substrates. Both designs utilized the same materials with the same layer thicknesses but different physical layouts. Electrical testing was carried out in different frequency regimes to characterize the capacitors.

#### 1.2. EXPERIMENTAL

All capacitors were deposited on fired 11x11 cm LTCC substrates. Each substrate was cleaned by immersion and agitation in acetone, methanol, and de-ionized water for 3 minutes. Capacitors were sputter deposited through physical masks in three

separate layers, a 200 nm thick Al bottom electrode, a 300 nm thick Al<sub>2</sub>O<sub>3</sub> dielectric layer and a 200 nm thick Al top electrode. Sputter deposition was carried out with a Denton Discovery 18 system at Missouri S&T. Aluminum electrode layers were deposited from a 99.99% pure metallic target at a power of 300 W using a DC power supply. The Al<sub>2</sub>O<sub>3</sub> dielectric layer was deposited from a 99.9% pure ceramic target at a power of 200 W using a RF power supply. Layer thicknesses were measured using a Tencor Alpha Step 200 profilometer. All depositions were carried out in an atmosphere of 99.999% pure Ar at a working pressure of 8 mtorr. No substrate heating was used during deposition.

Masks were fabricated at Towne Technologies, Inc using a bilayer Cu/Ni configuration. The first set of masks featured metal electrodes with widths of approximately 150, 380, 530 and 750 µm (Figure 1.1). Combining the electrode widths led to 48 capacitors with 9 different areas. The second set of masks featured shapes optimized for high frequency electrical testing. This design featured 150 capacitor structures, but not all of the devices were testable due to incomplete pattern transfer during deposition. The results from four different capacitor device sizes were measured and are reported herein.

After deposition optical micrographs were taken of each capacitor. Figure 1.2 shows example images from both device designs. The  $Al_2O_3$  layer is faintly visible in the top image as a vertical stripe that darkens the LTCC substrate. In the bottom image the  $Al_2O_3$  dielectric layer is visible as a slight discoloration on the vertical edges of the top Al layer. ImageJ software was used to measure the width of each electrode and the capacitor area was calculated.

The DC resistance, R, was measured for each capacitor with a Keithly 2002 digital multimeter. These resistance measurements were used as a first indication of capacitor performance. A R= 20 M $\Omega$  was arbitrarily chosen as a dividing line between potential capacitors and non-functioning devices. Current-voltage measurements were carried out with a HP 4140B pA Meter. Capacitors were tested from -100V to 100V in an alternating fashion (10V, -10V, 20V, etc). Results are reported as current density, J (A/cm²), vs. electric field, E (MV/cm). The testing voltages correspond to electric field values between -3.3 and 3.3 MV/cm. Capacitance and tan  $\delta$  were measured at 10 kHz with a HP 4194A Impedance analyzer.

Figure 1.1. Design of LTCC substrates featuring thin film capacitors made for low frequency testing. The first metal layer is shown in black, the second layer (dielectric) is tan, and the third layer (metal 2) is black.

Figure 1.2. Optical micrograph of individual capacitors. The red dimensions indicate where measurements were taken using ImageJ. The top image is of a capacitor that was tested at low frequency. The bottom image is an example of the capacitors that were tested with a high frequency 3-point probe setup.

#### 1.3. RESULTS AND DISCUSSION

One capacitor design was made for testing at DC and low ( $\leq$ 15 MHz) frequencies (see Figure 1.2 top), and another design was made for testing at high ( $\leq$ 1 GHz) frequencies (Figure 1.2 bottom). Impedance analysis was carried out on both device designs along with current-voltage testing on the low frequency samples.

The actual sizes of the capacitors were larger than the size of the mask openings due to lifting of the physical masks during deposition. Therefore, all of the devices were measured optically in order to determine actual capacitor dimensions. The mean percent error between the measured areas and the design areas was 55% with a standard deviation of 44%. The capacitors made for high frequency testing were also larger than expected. Due to the finer feature size of the high frequency capacitors, >90% of the devices were unusable due to poor pattern transfer.

1.3.1. Low Frequency and DC Testing. Initial testing of the fabricated devices indicated that 41 of the 48 potential capacitors had  $R \ge 20 \text{ M}\Omega$ . This result was later verified by capacitance and loss measurements which indicated the same number of capacitors featured low loss and capacitance values matching the measured areas. Testing was not carried out to find the reason for device failure.

Figure 1.3 illustrates the J vs. E results for capacitors with areas of  $5x10^{-3}$  cm<sup>2</sup> and  $8x10^{-3}$  cm<sup>2</sup>. Both capacitors exhibited nonlinear current response at E values greater than  $\pm 2$  MV/cm and the larger capacitor broke down at E=2.3 MV/cm. The linear portion is indicative of Ohmic conduction, while the nonlinear portion could indicate a variety of conduction mechanisms, such as Schottky emission or space-charge-limited current. Current response was an order of magnitude greater for the larger capacitor, indicating lower resistance from Ohm's law:

$$\rho = \frac{E}{J} \tag{1}$$

where E is the electric field (V/cm), J is the current density (A/cm<sup>2</sup>), and  $\rho$  is the resistivity ( $\Omega$  cm). From the linear portion, the smaller capacitor featured a resistivity of

$1.8 \times 10^{14} \Omega$ -cm while the larger capacitor featured a resistivity of  $1.9 \times 10^{12} \Omega$ -cm. These resistivity values are near the bulk value of  $10^{13} \Omega$ -cm and indicate that both capacitors are insulating to DC voltages.

Figure 1.4 shows the collected capacitance and loss data for all functioning capacitors. Capacitance values increased from 14 to 363 pF with area (Figure 1.4 top). All capacitors featured loss values less than 0.07 with 85% below 0.03 (Figure 1.4 bottom). The theoretical capacitance for each device area was calculated from the following equation:

$$C = \frac{\varepsilon_0 KA}{t} \tag{2}$$

where C is capacitance (F),  $\epsilon_0$  is the permittivity of free space (F/m), K is the dielectric constant, A is the capacitor area (m²), and t is the dielectric thickness (m). Equation 2 was used to calculate the theoretical capacitance of each capacitor, using measured area and dielectric thickness. The K of the thin film  $Al_2O_3$  was assumed to be equal to the bulk value of 10. The line in Figure 1.4 (top) shows the theoretical capacitance calculated by equation 2. Most of the capacitors lie along the theoretical capacitance vs. area line, indicating that the dielectric constant of thin film  $Al_2O_3$  was very close to the bulk value. Rearranging equation 2 allows for the calculation of the dielectric constant. The 10 kHz capacitance values were used to calculate the dielectric constant for each functioning capacitor. The mean dielectric constant was 12.0 with a standard deviation of 3.4.

1.3.2. High Frequency Testing. High frequency measurements were carried out using a 6 GHz HP 8753E vector network analyzer (VNA) and 18 GHz ground-signal-ground GGB Industries probes. A GGB CS-9 calibration substrate was used to correct internal VNA errors and a de-embedding structure equivalent to that of the bottom capacitor in Figure 2.2. The dielectric was removed to measure and remove interconnect series-resistances and series-inductances from the measurements.

Capacitors with areas of  $6.5 \times 10^{-4}$  cm<sup>2</sup> and  $1.0 \times 10^{-2}$  cm<sup>2</sup> were measured. Raw measured results for the larger capacitor from 0.1 MHz to 6 GHz are shown in Figure 1.5a, and the de-embedded result with the series R and L removed is shown in Figure 1.5b. Note that the interconnect had an R  $\geq$  1  $\Omega$  due to the relatively thin metal films used, but for the capacitor itself the equivalent series resistance, ESR, is  $< 0.5 \Omega$ .

De-embedded ESR and capacitance versus frequency are shown in Figures 1.6 and 1.7 respectively. Both capacitors featured a stable frequency range from ~1 MHz to over 500 MHz where the capacitance varied less than 5%. Variations seen outside this frequency range may be due to measurement limitations of the S-parameter equipment used, although the larger capacitor has a self-resonant frequency limitation seen at ~2 GHz.

The temperature coefficient of capacitance, TCC, was also measured for capacitors built using the high-frequency design with areas of  $6.5 \times 10^{-4}$ ,  $2.6 \times 10^{-3}$ ,  $5.8 \times 10^{-3}$ , and  $1.0 \times 10^{-2}$  cm<sup>2</sup>. The capacitance of each was measured at a frequency of 1 kHz and at temperatures of 25, 50, 75, and 100°C. Results, including the TCC and the change in capacitance over the 75°C temperature range are listed in Table 1.1. All of the capacitors feature less than 6.5% capacitance change over the 75°C temperature range. While the change in capacitance is higher than what is required for Electronic Industries Alliance (EIA) class I capacitors, all of the capacitors fall within the range of F type EIA class II capacitors.

#### 1.4. CONCLUSIONS

Sputtering was used to deposit 2 different thin film capacitor designs onto LTCC substrates. The first design featured nonlinear current density vs. electric field response, as well as low (<0.06) tan  $\delta$  values. These capacitors also featured capacitance values that suggested the thin film dielectric constant of  $Al_2O_3$  was approximately 12, slightly higher than the bulk value of 10. Capacitance values from the second layout featured a stable frequency range from 1 to > 500 MHz where the capacitance varied less than 20 pF. The same capacitors also featured <6.5% variation in capacitance from 25 to  $100^{\circ}$ C. The high-frequency capacitor design featured self-resonant frequencies of up to 2 GHz for a 0.5 nF device, and low loss with ESR of approximately 0.5 Ohms in the GHz range.

De-embedding structure measurements suggest that even lower values of ESR may be achievable with thicker metal film depositions.

Figure 1.3. Electric field vs current density for capacitors with areas of  $5x10^{-3}$  cm<sup>2</sup> (top) and  $8x10^{-3}$  cm<sup>2</sup> (bottom).

Figure 1.4. Capacitance vs. area (top) and loss vs. area (bottom) for the low frequency test devices.

Figure 1.5. Top Smith chart is raw measurement (a). Lower chart (b) shows measured impedance after de-embedding of LR interconnect parasitics.

Figure 1.6. Equivalent series resistance (ESR) versus frequency for the  $1.0 \times 10^{-2} \text{ cm}^2$  capacitor.

Figure 1.7. Capacitance vs. frequency for capacitors with areas of  $6.5 \times 10^{-4}$  cm<sup>2</sup> (top) and  $1.0 \times 10^{-2}$  cm<sup>2</sup> (bottom).

| Area                 | Temperature          | Capacitance |  |

|----------------------|----------------------|-------------|--|

|                      | Coefficient          | change      |  |

| cm <sup>2</sup>      | 1/K                  | %           |  |

| $6.5 \times 10^{-4}$ | $8.6 \times 10^{-4}$ | 6.5         |  |

4.4

5.7

6.3

$2.6 \times 10^{-3}$   $5.8 \times 10^{-4}$

$5.8 \times 10^{-3}$   $7.6 \times 10^{-4}$

$1.0x10^{-2}$   $8.4x10^{-4}$

Table 1.1. Temperature coefficient of capacitance for 3-point probe capacitors.

# 1.5. REFERENCES

- 1. ASM Handbook Vol. 5: Surface Engineering, ASM International, Sputter deposition chapter, 1994.

- 2. K. Delaney, J. Barrett, J. Barton, and R. Doyle, "Characterization and Performance Prediction for Integral Capacitors in Low Temperature Co-Fired Ceramic Technology," IEEE Transactions on Advanced Packaging, Vol. 22, No. 1, pp.68-77, 1999.

- 3. A. Baker, M. Lanagan, C. Randall, E. Semouchkina, G. Semouchkin, K. Rajab, R, Eitel, R. Mittra, S. Rhee, P. Geggier, C. Duschl, and G. Fuhr, "Integration Concepts for the Fabrication of LTCC Structures," International Journal of Applied Ceramic Technology, Vol. 2, No. 6, pp. 514–520, 2005.

- 4. M. Sebastian, and H. Jantunen, "Low loss dielectric materials for LTCC applications: a review," International Materials Reviews, Vol. 53, No. 2, pp. 57-90, 2008.

# 2. ELECTRON BEAM INDUCED CRYSTALLIZATION OF SPUTTER DEPOSITED AMORPHOUS ALUMINA THIN FILMS

Jack Murray, Kai Song, Wayne Huebner, and Matthew O'Keefe

Missouri University of Science and Technology Department of Materials Science and Engineering Rolla, MO 65409 USA

(Paper submitted to Materials Letters)

Keywords: crystallization, amorphous, alumina, thin-film, capacitor

# **ABSTRACT**

Crystallization of amorphous alumina ( $Al_2O_3$ ) in a thin film capacitor structure was induced by the electron beam of a transmission electron microscope (TEM). The crystallization was initially observed while collecting selected area diffraction (SAD) patterns after 2 minutes of beam exposure at an accelerating voltage of 200 keV and a beam current density of  $13.0 \text{ A/cm}^2$ . After 16 minutes of beam exposure, distinct ring patterns associated with crystal growth were evident in the SAD pattern. Bright field and dark field TEM images confirmed that crystallization occurred, with crystals growing up to  $\sim 50 \text{ nm}$  in diameter.

#### 2.1. INTRODUCTION

The crystalline form of alumina ( $\alpha$ -Al<sub>2</sub>O<sub>3</sub>) is thermodynamically stable but amorphous alumina can be deposited by certain techniques in thin film form. Amorphous alumina has been deposited by a variety of techniques including pulsed laser deposition (PLD) [1] and sputter deposition [2-7]. Each of these deposition techniques is a form of physical vapor deposition (PVD), where the target material is vaporized and deposited onto the substrate with little to no change in chemical composition. Amorphous alumina is also deposited by anodization of aluminum [8], but the films are often porous and contain impurities from the anodization process.

Previous work has demonstrated the ability of an electron or ion beam to crystallize amorphous materials, including metal alloys [9-12], semiconductors [13], and insulators [3, 8, 13]. Electron or ion beam induced crystallization of amorphous alumina has been reported in the literature in only a few instances. One study involved the crystallization of amorphous anodic alumina coatings on Al under an electron beam in a TEM at an accelerating voltage of 100 kV [8]. This study does not mention the beam current necessary for crystallization and the anodic films contained impurities from the anodization solution. Another study documented the crystallization of sputter deposited amorphous alumina using 1 MeV Si<sup>+</sup> ions [3]. In this work electron beam-induced crystallization of a sputter deposited, amorphous Al<sub>2</sub>O<sub>3</sub> film is reported. The results indicate that the process can be used to spatially manipulate the crystallinity, and thus the properties, of Al<sub>2</sub>O<sub>3</sub> thin films over a selected area.

#### 2.2. EXPERIMENTAL

Thin film capacitors with a Pt-Al<sub>2</sub>O<sub>3</sub>-Al layout were sputter deposited onto 11x11 cm fired low temperature co-fired ceramic (LTCC) substrates. The LTCC substrates were cleaned by immersion and agitation in acetone, methanol, and deionized (DI) water for 3 minutes each, with drying between each immersion step. Sputter deposition was carried out through 1.5 mm thick Mo shadow masks. Capacitor structures were constructed by depositing a Pt bottom electrode, followed by an Al<sub>2</sub>O<sub>3</sub> dielectric layer, then a top Al electrode. Figure 2.1 shows a cross-section schematic of a metal-insulator-metal capacitor consisting of 0.1 µm Pt bottom electrode, 1 µm thick Al<sub>2</sub>O<sub>3</sub> dielectric, and 0.2 µm Al top electrode.

Deposition was carried out using a Denton Discovery 18 magnetron sputter system. Metal (Al and Pt) electrode layers were deposited from 99.99% pure metal targets using a DC power supply at 300 W. The  $Al_2O_3$  dielectric layer was deposited from a 99.9% pure ceramic target using a RF power supply at 200 W. No substrate heating was used during deposition and all films were deposited using 99.999% pure Ar as the sputtering gas, at a working pressure of 1.07 Pa. Base pressure before deposition was  $\leq 10^{-6}$  Pa.

Figure 2.1. Schematic of the thin film capacitor layout used in this study, with approximate layer thicknesses.

TEM samples were prepared by focused ion beam (FIB) lift-out using a Helios Nano Lab 600 FIB. A cross section of a Pt-Al<sub>2</sub>O<sub>3</sub>-Al capacitor structure was milled using the FIB and lifted out using an omniprobe. TEM images and SAD patterns were collected using a Technai F20 TEM set at an accelerating voltage of 200 keV. SAD patterns were collected at beam currents of 18 nA and 135 nA, which correspond to current densities of 1.7 A/cm<sup>2</sup> and 13.0 A/cm<sup>2</sup>. After the diffraction patterns were collected bright field TEM images were captured. Centered dark field images were also captured using a portion of the ring structure visible in the SAD patterns for the diffracted beam.

# 2.3. RESULTS AND DISCUSSION

Figure 2.2 shows selected area diffraction (SAD) patterns collected from the amorphous alumina region of the sample in the TEM at a current density of 1.7 A/cm<sup>2</sup>. The first pattern was captured immediately after focusing and the second pattern was captured after 10 minutes of exposure to the electron beam. Both patterns are consistent with an amorphous material; no evidence of crystallization occurred for a current density of 1.7 A/cm<sup>2</sup> over the beam exposure times currently investigated.

Figure 2.2. SAD patterns from Al<sub>2</sub>O<sub>3</sub> thin film using a beam current of 1.7 A/cm<sup>2</sup>: a) initially and b) after 10 minutes.

A second region of the amorphous alumina layer was then examined with a beam current of  $13.0 \text{ A/cm}^2$ . Figure 2.3 (a) shows the initial SAD pattern of the  $\text{Al}_2\text{O}_3$  thin film, confirming the amorphous structure of the sputtered film. Crystallization began occurring after 2 minutes of electron beam irradiation (Figure 2.3 (b)). Increased beam time resulted in a sharpening of the polycrystalline rings in the subsequent patterns. Grain growth of the crystallized  $\text{Al}_2\text{O}_3$  is shown by the formation of diffraction spots in the SAD pattern after 16 minutes of beam exposure, as shown in Figure 2.3 (c).

Polymorphs of  $Al_2O_3$  are difficult to distinguish from each other using electron diffraction due to their similar d-spacings. The processing route from amorphous- $Al_2O_3$  to  $\alpha$ - $Al_2O_3$  is believed to occur via the following sequence [14]:

Amorphous

$$\rightarrow \gamma \rightarrow \delta \rightarrow \theta \rightarrow \alpha - Al_2O_3$$

(1)

Values for d-spacings for each of the outlined Al<sub>2</sub>O<sub>3</sub> polymorphs were located in JCPDS diffraction files [15] and the existence of any one polymorph over the others could not be definitively confirmed. The crystals formed in this study appear to be a mix of several Al<sub>2</sub>O<sub>3</sub> polymorphs, as calculated d-spacings matched at least one of the structures listed

above. This was in agreement with previous work that found that different  $Al_2O_3$  polymorphs can be present in samples simultaneously [14].

Figure 2.3. SAD patterns from  $Al_2O_3$  thin film: a) 13.0 A/cm<sup>2</sup> initially, b) after 2 minutes, and c) after 16 minutes.

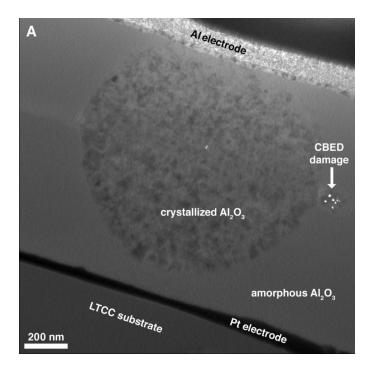

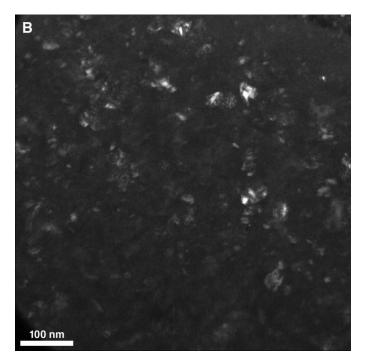

Figure 2.4 (a) shows the crystallized area in the amorphous  $Al_2O_3$  layer that was exposed to the electron beam for 16 minutes. The bright-field TEM micrograph also shows the entire height of the thin-film capacitor structure, with the LTCC substrate, Pt electrode,  $Al_2O_3$  dielectric and the Al electrode all visible. Holes in the sample are also visible to the right of the crystallized area from attempts at obtaining convergent beam electron diffraction (CBED) patterns. Collection of CBED patterns were unsuccessful; the patterns would change from amorphous to crystalline in a matter of seconds and then the beam would punch through the sample. A dark-field TEM micrograph of the crystallized alumina, after 16 minutes of electron beam exposure is shown in Figure 2.4 (b). The largest crystals oriented in the direction of the diffracted beam are  $\sim$  50 nm in diameter.

Note that in Figure 2.4 (a) that there is a decrease in crystallization toward the top of the Al<sub>2</sub>O<sub>3</sub> layer, near the Al top electrode. In contrast, the bottom of the area exposed to the electron beam is highly crystallized. The difference in crystallization between the two regions, both of which were exposed to the electron beam, is thought to occur because of the difference between the thermal conductivity, κ, of Al and Al<sub>2</sub>O<sub>3</sub>. In thin film form, the thermal conductivity of Al has been measured at 200 W m<sup>-1</sup> K<sup>-1</sup> [16]. In contrast, the thermal conductivity of thin film Al<sub>2</sub>O<sub>3</sub> deposited by anodic oxidation measured 0.5 W m<sup>-1</sup> K<sup>-1</sup> [17]. The large thermal conductivity disparity seems to indicate that the Al dissipates thermal energy away from the Al<sub>2</sub>O<sub>3</sub>, minimizing crystallization in the region near the Al. This, along with the detection of crystal growth in the diffraction patterns indicates that the crystallization process is thermal in nature, instead of an athermal, energy dissipation process described elsewhere [9].

#### 2.4. CONCLUSIONS

Sputter deposited thin film capacitor structures were fabricated and examined by transmission electron microscopy. Selected area diffraction patterns indicated that the amorphous alumina dielectric layer crystallized at current densities of 13.0 A/cm², but no crystallization occurred at 1.7 A/cm² beam current density. Crystallization began to occur after two minutes of beam exposure. Grain growth took place with longer beam exposure times and the largest crystals visible in TEM micrographs were ~ 50 nm in

Figure 2.4. TEM micrographs illustrating crystallized Al<sub>2</sub>O<sub>3</sub>: a) bright-field overview of crystallized area and b) dark-field detail of crystallized area after 16 minutes of electron beam exposure.

diameter after 16 minutes of electron beam exposure. 10 minutes of beam exposure at a current density of 1.7 A/cm<sup>2</sup> did not lead to crystallization. These results show that an electron beam can be used to selectively crystallize amorphous thin films in precise areas. As such, spatial variation of anisotropic properties can be achieved commensurate with the symmetry of the crystallized region.

# Acknowledgements