# Scholars' Mine

**Masters Theses**

Student Theses and Dissertations

Fall 2012

# Laminate dielectric and foil characterization for signal integrity on printed circuit board

Aleksandr Yakubovich Gafarov

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons Department:

#### **Recommended Citation**

Gafarov, Aleksandr Yakubovich, "Laminate dielectric and foil characterization for signal integrity on printed circuit board" (2012). *Masters Theses*. 5290. https://scholarsmine.mst.edu/masters\_theses/5290

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# LAMINATE DIELECTRIC AND FOIL CHARACTERIZATION FOR SIGNAL INTEGRITY ON PRINTED CIRCUIT BOARD

by

# ALEKSANDR YAKUBOVICH GAFAROV

### A THESIS

Presented to the Faculty of the Graduate School of the

### MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

# MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

2012

Approved by

Marina Y Koledintseva, Advisor James L. Drewniak Jun Fan

© 2012

Aleksandr Yakubovich Gafarov All Rights Reserved

#### ABSTRACT

Accurate characterization of laminate dielectrics as substrates of printed circuit boards (PCB) over a wide frequency range (from tens megahertz to tens gigahertz) is important from a signal integrity (SI) point of view. Accurate knowledge of dielectric constants (DK) and dissipation factors (DF), or loss tangents, of laminate dielectrics, as well as loss in conductors, as functions of frequency over a wide frequency range, are needed to the designers of high-speed digital electronics.

An "in situ" wideband traveling-wave technique based on measuring Sparameters of the PCB test vehicles with auxiliary 'through-reflect-line" (TRL) calibration patterns has been developed. This technique has been extensively applied to the material characterization of PCBs up to 20 GHz. However, extension of the frequency range of testing PCBs up to 50 GHz requires solving numerous problems, related to a new PCB test vehicle design and improvement of the material parameter extraction algorithms to take into account various subtle effects arising as frequencies increase to 50 GHz. Extending the frequency range in the new 50-GHz test vehicles leads to potentially increasing uncertainties compared to the 20-GHz test vehicles. Different sources of errors and uncertainties for extracting DK and DF values are analyzed for both the present 20-GHz and the new perspective 50-GHz test vehicles. The limitations for the design of test vehicles are also discussed.

An alternative technique for measuring dielectric parameters of PCB laminate dielectrics is using split-post dielectric resonator (SPDR). This narrowband technique is applied to measurements of thin dielectric plates at frequencies 10 GHz, 15 GHz, and 20 GHz.

#### ACKNOWLEDGMENTS

I express my sincere gratitude to my advisor, Dr. Marina Y. Koledintseva, for her constant support and inspiration for work. The level of her intelligence and knowledge has always been my motivation in the pursuit of my Master's degree. I thank Dr. James L. Drewniak for his mentoring and guidance in my career path, which began in the EMC Laboratory. I deeply appreciate the help from Scott Hinaga during my work on the CISCO project in the lab.

Also I want to show my deep gratitude to all professors of the EMC Laboratory for giving me priceless knowledge during course work, and showing faith in me as a future student, before I joined the lab. When I had any problems Dr. David Pommerenke, Dr. Jun Fan, and Dr. Tomas Van Doren would be always there to support me and show the right path. I am grateful for the financial support of the research assistantship from the EMC Laboratory.

I thank all my fellow laboratory students, who gave me advice and helped me work through any problems I encountered. With great help of Clarissa Wisner I was able to develop my new professional skills and to get very useful knowledge.

Finally, I would like to thank my beloved family (mom, dad, sister, brother-in-law and nephew), fiancé, and her family for their endless and unconditional love, support, and encouragement through all my education and life. Those delicious steaks and chicken which they were making always were giving me additional power to complete my thesis. This work I dedicate to all of them to show how much they mean to me.

# TABLE OF CONTENTS

| Page |

|------|

|------|

| ABSTRACT                                                                                                       | iii |

|----------------------------------------------------------------------------------------------------------------|-----|

| ACKNOWLEDGMENTS                                                                                                | iv  |

| LIST OF ILLUSTRATIONS                                                                                          | vii |

| LIST OF TABLES                                                                                                 | X   |

| SECTION                                                                                                        |     |

| 1. INTRODUCTION                                                                                                | 1   |

| 2. TRAVELING WAVE METHOD FOR PRINTED CIRCUIT BOARD<br>CHARACTERIZATION                                         | 3   |

| 2.1. REVISIT OF MATERIAL PARAMETER EXTRACTION<br>PROCEDURE USING A TRAVELING WAVE METHOD                       | 3   |

| 2.2. SOURCES OF TROUBLES AND ERROR ASSESMENT IN DK/DF<br>EXTRACTION                                            | 7   |

| 2.2.1. Non-Ideal Effects Due To Via-Connector-Trace Transitions                                                | 8   |

| 2.2.2. Non-Ideal Effects Due To TRL Calibration Pattern Design                                                 | 13  |

| 2.2.3. Effects Due To Conductor Surface Roughness                                                              | 15  |

| 2.2.4. Non-Ideal Effects Due To Test Fixture Artifacts                                                         | 22  |

| 2.3. OVERVIEW OF ERRORS AND UNCERTAINTIES ASSOCIATED<br>WITH TRAVELLING WAVE METHOD, AND POSSIBLE<br>SOLUTIONS | 25  |

| 3. DESIGN OF A TEST VEHICLE UP TO 50 GHZ                                                                       | 27  |

| 3.1. OVERVIEW OF THE GEOMETRY AND STACK-UP OF<br>CURRENT PRINTED CIRCUIT BOARD DESIGN                          | 27  |

| 3.2. MODIFICATION AND IMPROVEMENT OF TEST VEHICLE DESIGN                                                       | 37  |

| 3.2.1. Improvement In Via Design                                                                               | 38  |

| 3.2.2. Connector Replacement.                                                                                 | 56   |

|---------------------------------------------------------------------------------------------------------------|------|

| 3.2.3. Modification In TRL Calibration Patterns                                                               | 58   |

| 3.2.4. Correction In Via Wall Design.                                                                         | 66   |

| 3.3. SUMMARY OF MODIFICATIONS FOR 50-GHZ TEST VEHICLE                                                         | 69   |

| 4. DIELECTRIC MATERIAL CHARACTERIZATION USING SPLIT<br>POST DIELECTRIC RESONATOR (SPDR)                       | 72   |

| 4.1. THEORETICAL OVERVIEW OF THE 'SPLIT POST DIELECTRIC<br>RESONATOR' MEASUREMENT TECHNIQUE                   | 73   |

| 4.2. ANALYSIS OF THE MEASUREMENT PROCEDURE AND<br>RESULTS                                                     | 80   |

| 4.3. ON POSSIBILITY OF COMPARING SPDR AND TRAVELING<br>WAVE METHOD RESULTS                                    | 90   |

| 5. CONCLUSION AND FUTURE SCOPE                                                                                | 94   |

| APPENDICES                                                                                                    |      |

| A. DERIVATION OF THE FORMULAS TO CALCULATE ε' <sub>r</sub> AND ε" <sub>r</sub> IN<br>THE EXTRACTION PROCEDURE | 96   |

| B. FORMULAS TO EXTRACT DK AND DF BASED ON MEASURED S-<br>PARAMETERS                                           | 99   |

| C. CALCULATIONS OF SYSTEMATIC ERRORS IN DK AND DF                                                             | .102 |

| D. SAMPLE PREPARATION FOR THE SCANNING ELECTRON<br>MICROSCOPY                                                 | .107 |

| E. DATASHEET OF THE 'SV MICROWAVE' 2.4 MM SMA CONNECTOR<br>WHICH WILL BE USED IN NEW PCB DESIGN               | .126 |

| F. DETAILS OF THE NEW TEST VEHICLE DESIGN                                                                     | .128 |

| G.MEASURING PROCEDURE OF DIELECTRIC PARAMETERS USING<br>SPLIT POST DIELECTRIC RESONATOR TECHNIQUE             | .136 |

| BIBLIOGRAPHY                                                                                                  | 153  |

| VITA                                                                                                          | 156  |

# LIST OF ILLUSTRATIONS

|             | Page                                                                                                                                                                 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.1  | The picture of the test vehicle and stack-up4                                                                                                                        |

| Figure 2.2  | Sources of errors and uncertainties7                                                                                                                                 |

| Figure 2.3  | Acceptable connector mounting to PCB9                                                                                                                                |

| Figure 2.4  | Non-acceptable connector mounting to PCB10                                                                                                                           |

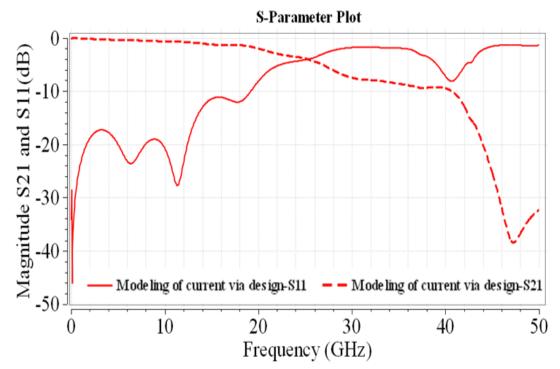

| Figure 2.5  | Modeling of the via with a stub and without any stub (MVTT tool)11                                                                                                   |

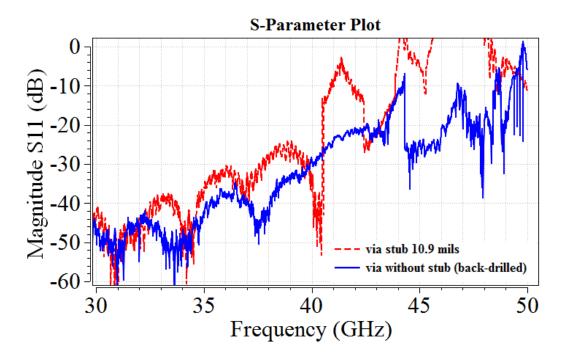

| Figure 2.6  | Comparison of the return loss for the PCB with 10.9mils via stub and PCB with back-drilled via (the same material and geometry of the test vehicles)                 |

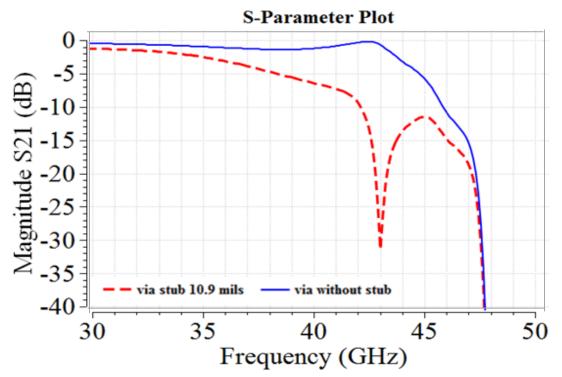

| Figure 2.7  | Comparison of the insertion loss for the PCB with 10.9mils via stub<br>and PCB with back-drilled via (the same material and geometry of the<br>test vehicles)        |

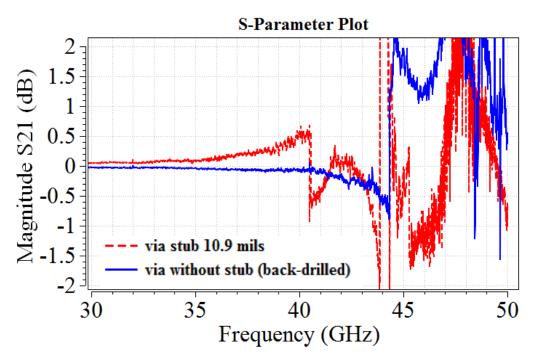

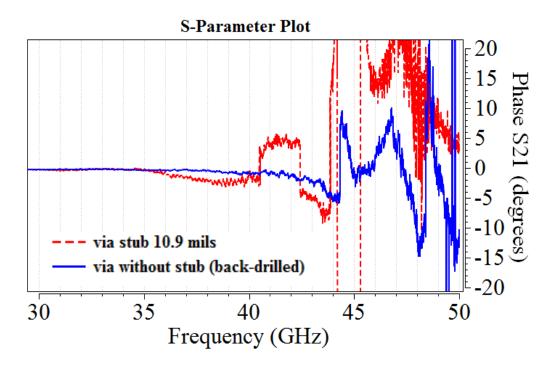

| Figure 2.8  | Comparison of the phase of the insertion loss for the PCB with 10.9mils via stub and PCB with back-drilled via (the same material and geometry of the test vehicles) |

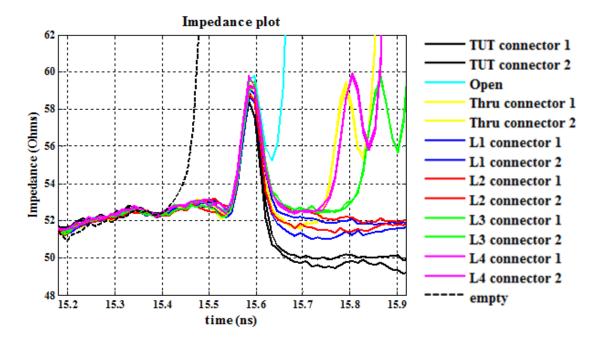

| Figure 2.9  | Impedance measurements using TDR15                                                                                                                                   |

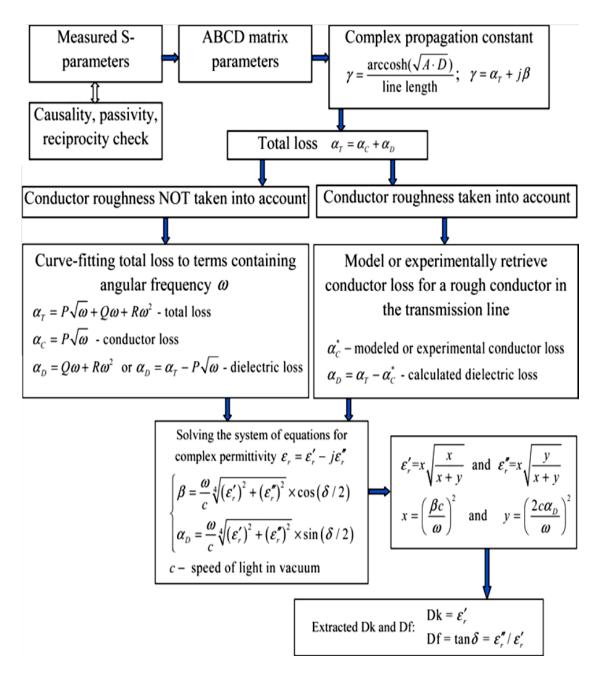

| Figure 2.10 | Flowchart of the procedure for extracting dielectric parameters from S-<br>parameters [3]                                                                            |

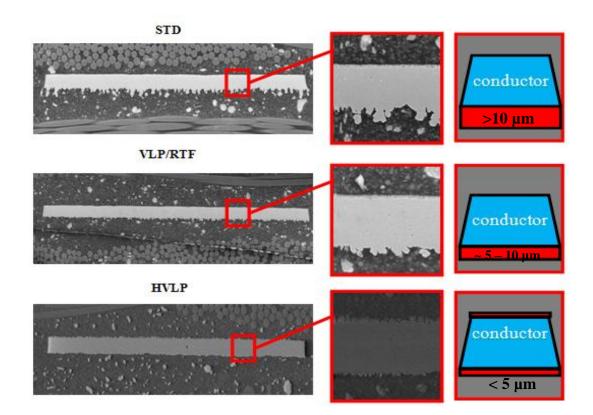

| Figure 2.11 | Cross-sectional SEM images of three types of foil used in current work20                                                                                             |

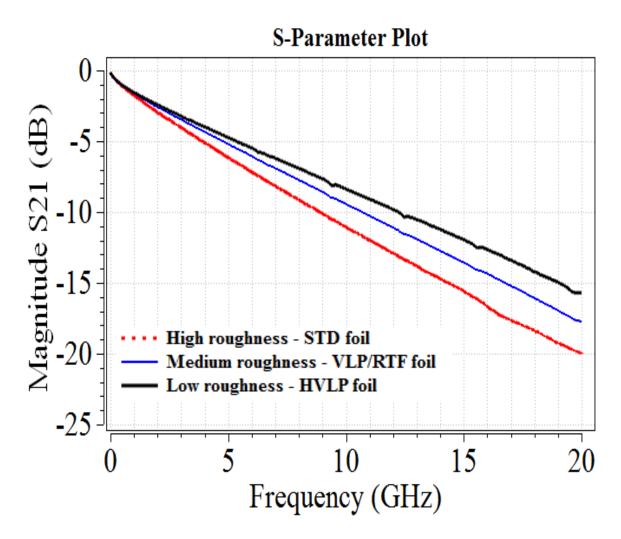

| Figure 2.12 | Insertion loss (S21) comparison between different types of foil21                                                                                                    |

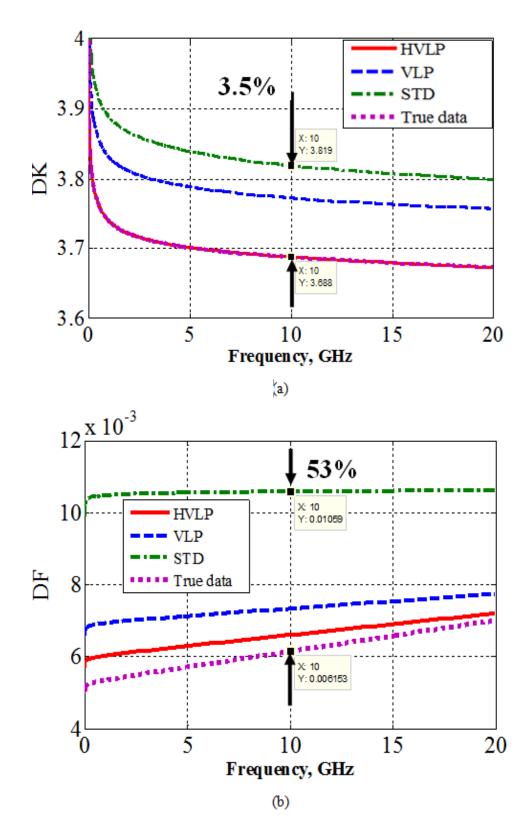

| Figure 2.13 | Dielectric parameters extracted using different methods to compare<br>rough foils with perfectly smooth conductor                                                    |

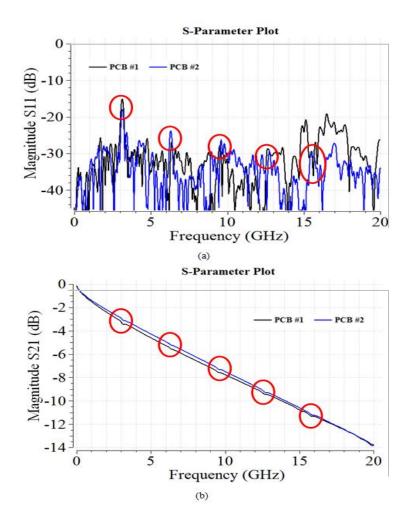

| Figure 2.14 | S-parameters measured over 16 inch transmission line. Artifacts are highlighted by red circles                                                                       |

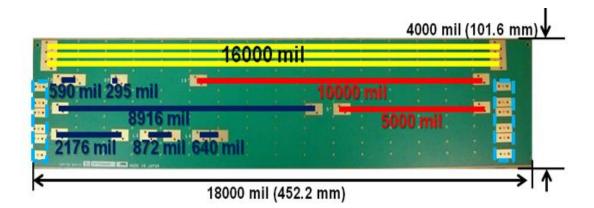

| Figure 3.1  | Dimensions and layout of the test vehicle                                                                                                                            |

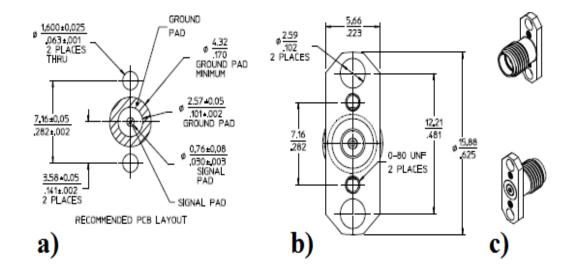

| Figure 3.2  | Geometry and overview of the SMA connectors.                                                                | .30 |

|-------------|-------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.3  | Stack-up details of 6-layer PCB                                                                             | .32 |

| Figure 3.4  | CST model of the via structure for 20-GHz test vehicle                                                      | .33 |

| Figure 3.5  | Return loss of the via modeled in full-wave CST                                                             | .34 |

| Figure 3.6  | Insertion loss of the via modeled in full-wave CST                                                          | .35 |

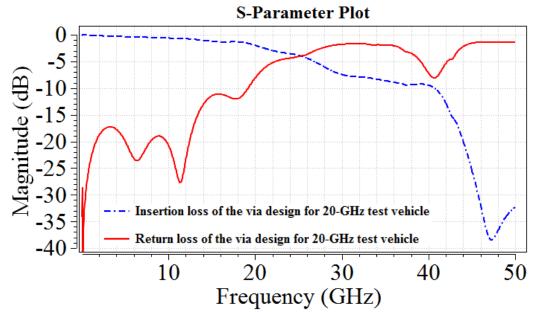

| Figure 3.7  | Insertion loss and return loss of the via modeled in full-wave CST on<br>the same comparison graph          | .35 |

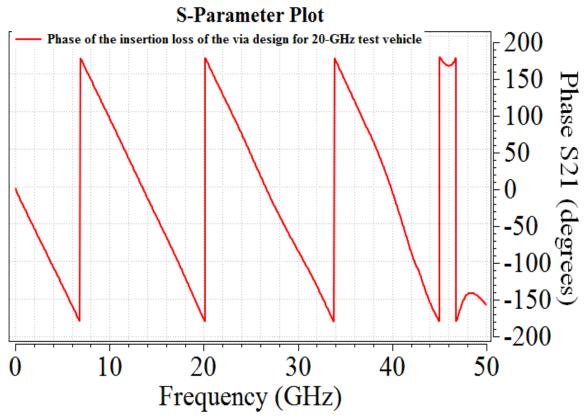

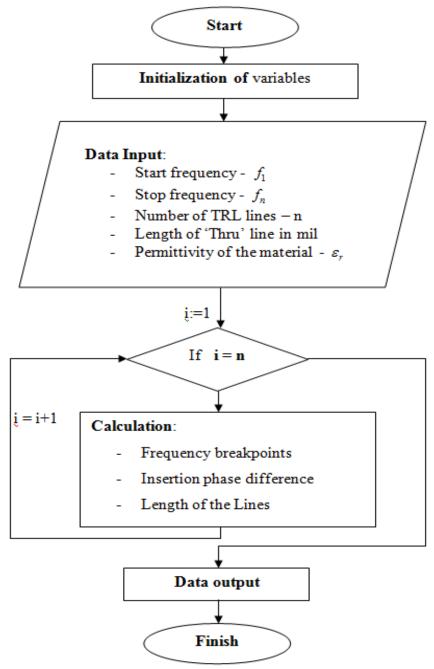

| Figure 3.8  | Phase of insertion loss of the via modeled in full-wave CST                                                 | .36 |

| Figure 3.9  | Summary of the issues for improving                                                                         | .38 |

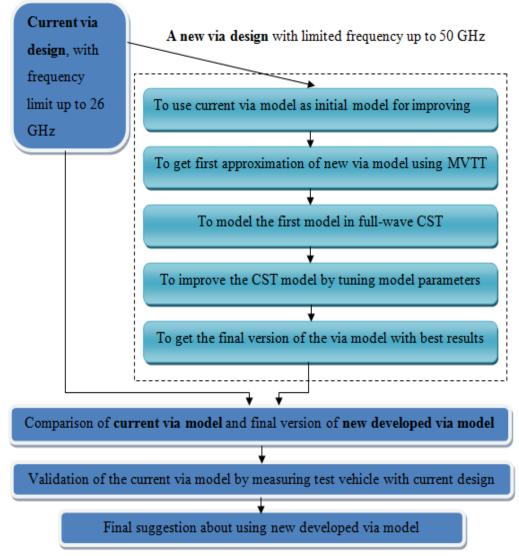

| Figure 3.10 | Algorithm of the new via design development                                                                 | .39 |

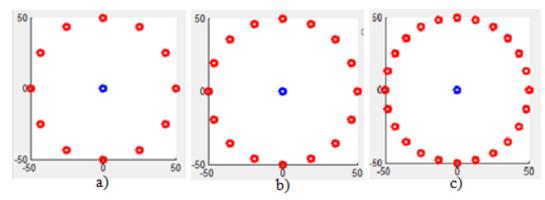

| Figure 3.11 | The top view of via models, analyzed using MVTT                                                             | .41 |

| Figure 3.12 | Calculated S-parameters using the MVTT (snapshot)                                                           | .42 |

| Figure 3.13 | Overview of the first via geometry CST model                                                                | .44 |

| Figure 3.14 | Results of modeling of improved via model in CST. Blue curve indicated  S21 , red curve corresponds to  S11 | .45 |

| Figure 3.15 | Overview of the second CST design via model                                                                 | .46 |

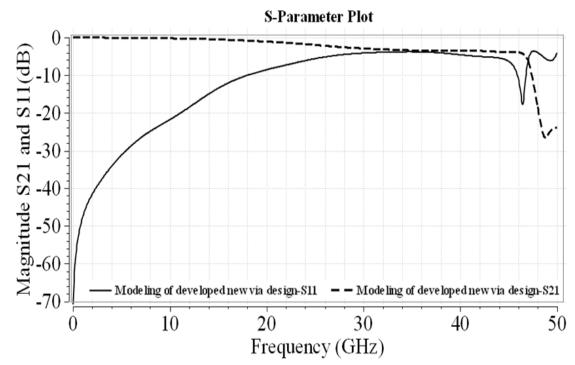

| Figure 3.16 | Results of modeling new 50-GHz via design in CST                                                            | .48 |

| Figure 3.17 | Simulated phase of S21. in the second CST 50-GHz via model                                                  | .49 |

| Figure 3.18 | Prospective views on the CST via models                                                                     | .49 |

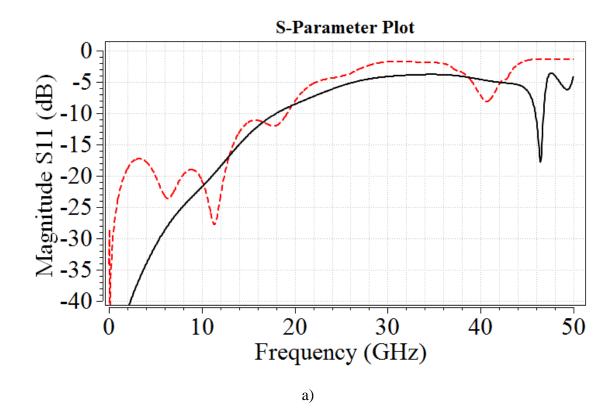

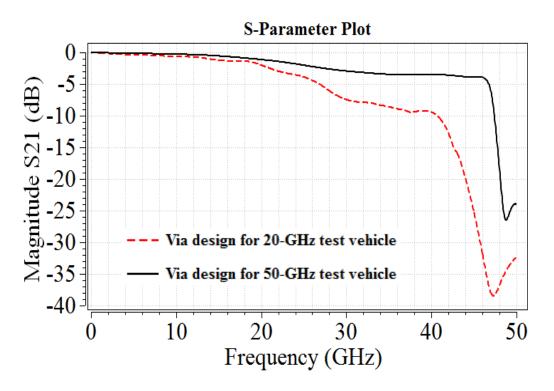

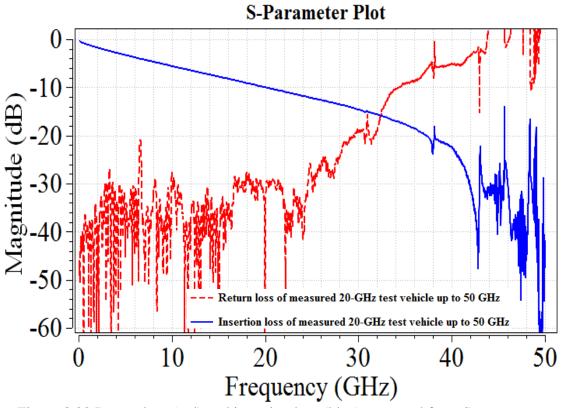

| Figure 3.19 | Return and insertion losses of the via structure developed for the 20-<br>GHz test vehicle                  | .50 |

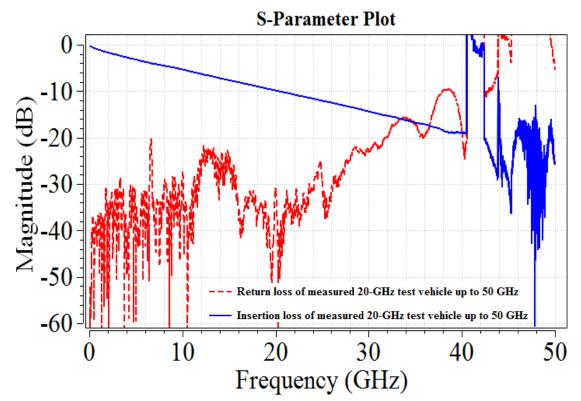

| Figure 3.20 | Return and insertion loss of the via structure, developed for the 50-GHz test vehicle                       | .51 |

| Figure 3.21 Comparison of the current via design and new via design, simulated ir CST                                                                     |                                                                                                                                                  |    |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| Figure 3.22 Return loss (red) and insertion loss (blue) extracted from S-parameters of a test vehicle with 16'' trace under test app 3.5mm SMA connectors |                                                                                                                                                  |    |  |

| Figure 3.23                                                                                                                                               | Results of measuring PCB with 2.4 mm SMA connectors applied                                                                                      | 57 |  |

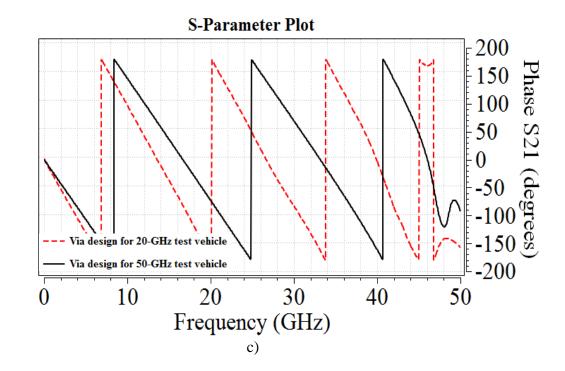

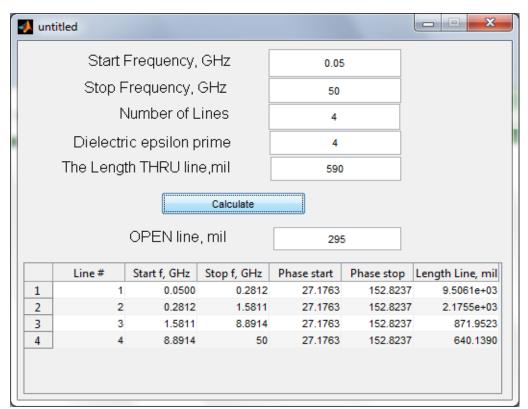

| Figure 3.24                                                                                                                                               | Algorithm of the Matlab GUI for calculating TRL calibration patterns                                                                             | 52 |  |

| Figure 3.25                                                                                                                                               | Results for calculating TRL calibration patterns for current PCB design using Matlab GUI                                                         | 53 |  |

| Figure 3.26                                                                                                                                               | Results of the TRL patterns calculation for current PCB design                                                                                   | 54 |  |

| Figure 3.27                                                                                                                                               | Results for calculating TRL calibration patterns for current PCB design using Matlab GUI                                                         | 55 |  |

| Figure 3.28                                                                                                                                               | Simulated results of the via wall artifact                                                                                                       | 58 |  |

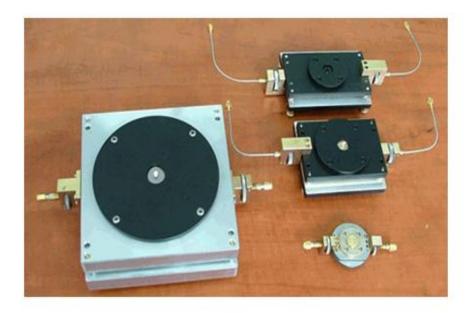

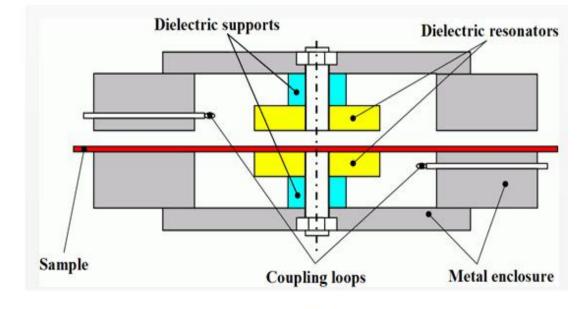

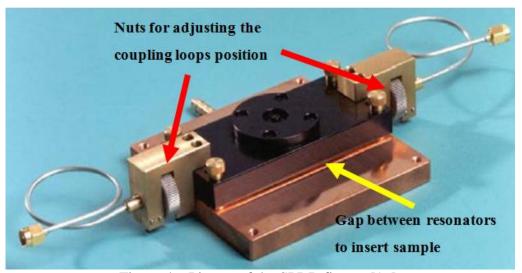

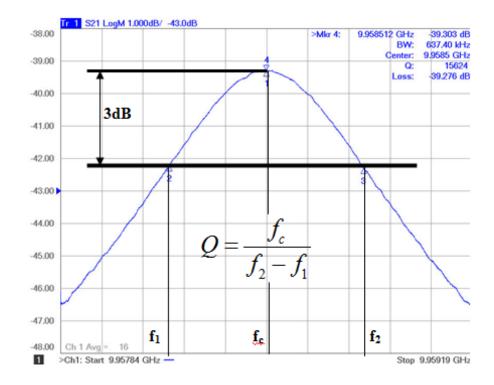

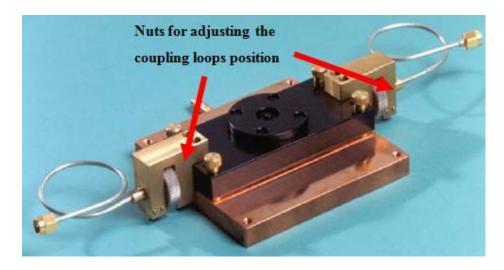

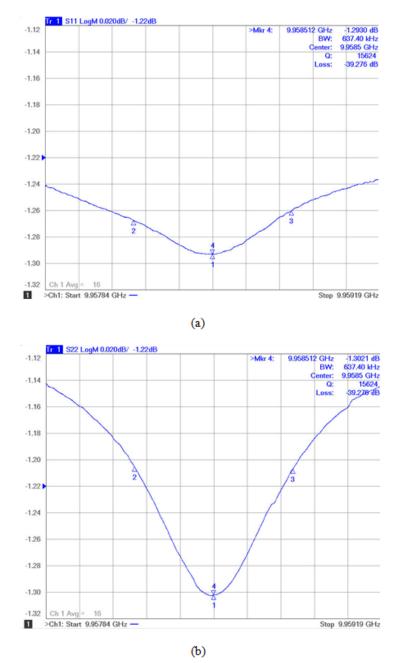

| Figure 4.1                                                                                                                                                | Split post dielectric resonator (SPDR).                                                                                                          | 74 |  |

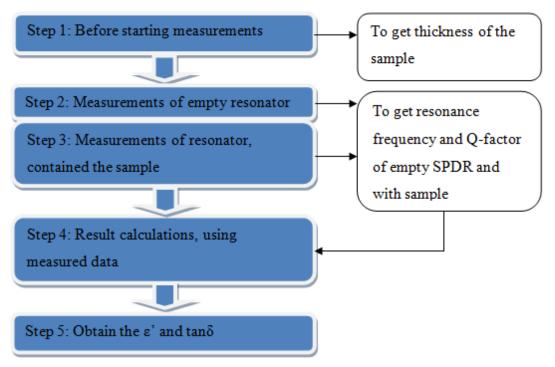

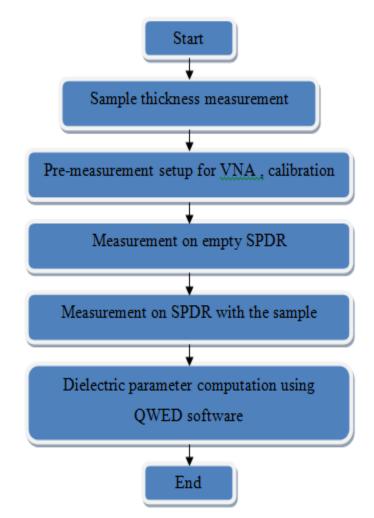

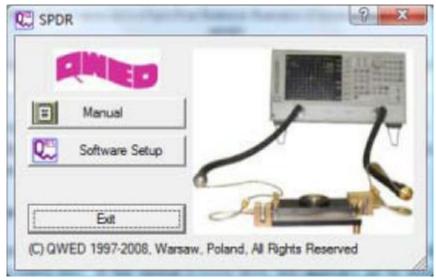

| Figure 4.2                                                                                                                                                | The procedure of measurements and computing data                                                                                                 | 76 |  |

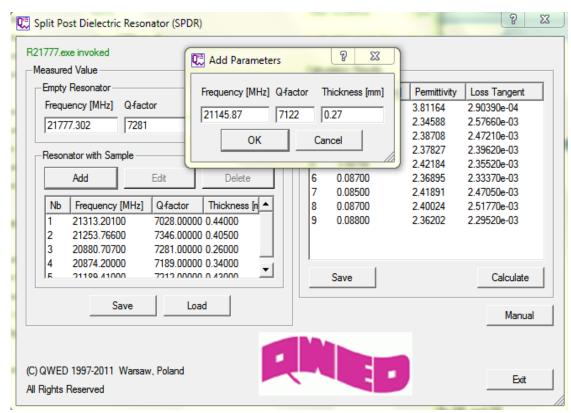

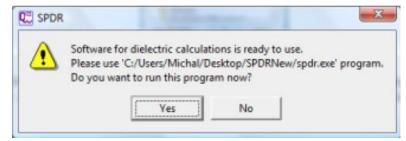

| Figure 4.3                                                                                                                                                | Example of computing dielectric parameters using QWED software.<br>Input data presented on the left side of the tool, results of the right side? | 79 |  |

| Figure 4.4                                                                                                                                                | Measurement step-by-step procedures                                                                                                              | 31 |  |

| Figure 4.5                                                                                                                                                | The measurement setup [16]                                                                                                                       | 32 |  |

| Figure 4.6                                                                                                                                                | Picture of the SPDR fixture [16]                                                                                                                 | 33 |  |

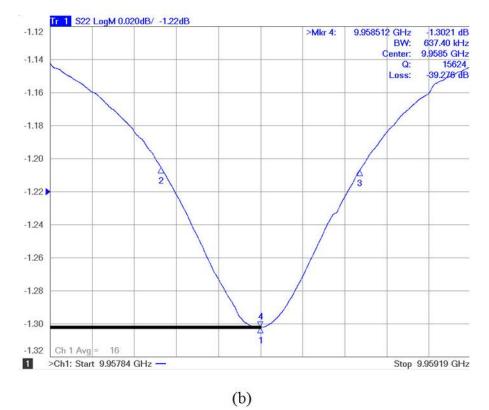

| Figure 4.7                                                                                                                                                | Example of the S-parameters after well adjusted coupling loops                                                                                   | 34 |  |

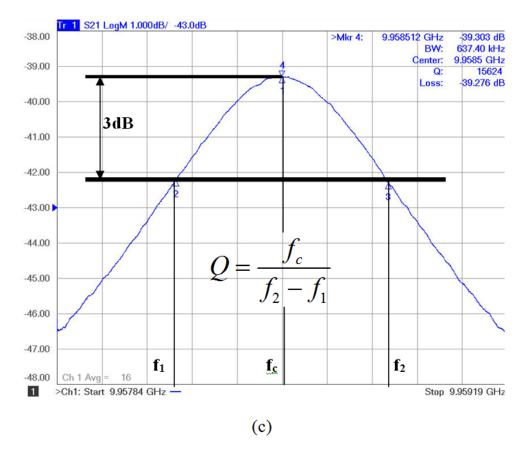

| Figure 4.8                                                                                                                                                | An effect of anisotropy [24]                                                                                                                     | €  |  |

# LIST OF TABLES

|           | Page                                                                                                                      | e |

|-----------|---------------------------------------------------------------------------------------------------------------------------|---|

| Table 2.1 | Line length calculations for different DK values14                                                                        | 4 |

| Table 2.2 | Challenges and possible solutions                                                                                         | б |

| Table 3.1 | Overview of the optimization for via geometry parameters for different DK, DF4                                            | 3 |

| Table 3.2 | Geometry and parameter comparison of the two via designs                                                                  | 2 |

| Table 3.3 | Summary of the TRL calibration pattern characteristics for the new developed test vehicle                                 | 5 |

| Table 3.4 | Comparison overview of current and new test vehicle designs                                                               | 0 |

| Table 4.1 | The minimum sizes of sample according to the operating frequency suggested by QWED [19]73                                 | 5 |

| Table 4.2 | Summary of measurement on Fused Silica                                                                                    | 8 |

| Table 4.3 | Comparison of results obtained from measurement in EMC Laboratory<br>and National Institute of Standards and Technology90 | 0 |

#### **1. INTRODUCTION**

An interest in the high-speed data rate transfer in printed circuit boards (PCBs) has raised the necessity to explore radio frequency and microwave parameters of the PCB materials – laminate dielectrics and conductors. The laminate dielectrics, used as substrates of striplines in multilayered PCBs, are characterized by the dielectric constant, DK, the real part of relative permittivity  $\varepsilon'_r = \operatorname{Re}(\varepsilon_r)$  and dissipation factor DF, or loss tangent  $\tan \delta = \varepsilon''_r / \varepsilon'_r = \operatorname{Im}(\varepsilon_r) / \operatorname{Re}(\varepsilon_r)$ .

The procedure to extract dielectric material parameters, as well as conductor loss in stripline structures inside PCBs, in this work is based on a traveling-wave method for TEM modes propagating along a stripline. This method includes measuring S-parameters of the specially designed test vehicles in the frequency domain using a vector network analyzer (VNA). These test vehicles have "through-reflect-line" (TRL) calibration patterns on them to eliminate port effects at the connectors of the lines. Currently, the test vehicles designed for operation over the frequency range from 50 MHz to 20 GHz have been used. However, data rates of high-speed digital designs using PCBs steadily increase with the progress in modern electronics, and hence there is a necessity for extending the frequency range of measuring material properties of PCBs. This requires not only improvement of the material parameter extraction algorithms, which would take into account various subtle effects arising as frequencies increase beyond twenty gigahertz, but also necessitates modifying a test vehicle design, or even developing substantially new designs of the test vehicles to satisfy requirements of operating at higher frequencies. The main goal of this work is to extend the frequency range of the PCB test vehicle operation up to 50 GHz.

Analysis of measurement errors and uncertainties both in the test vehicles design for measurements up to 20 GHz and in the new test vehicles operating up to 50 GHz is an important problem to be solved. Extending the frequency range to operate at frequencies up to 50 GHz, the new 50-GHz test vehicles should be designed. The extension of the frequency range may result in increased uncertainties compared to the 20-GHz test vehicles. To avoid problems, or at least minimize artifacts in the new design, the errors, uncertainties, and limitations are investigated and analyzed in Section I of this work. Section II is devoted to the new 50-GHz test vehicle design, including optimization of ground-via transitions at the connectors. There are several errors, described in Section I, which have been taken into account at the design of the new test vehicle.

PCB dielectric material parameters extracted using the traveling-wave method based on measuring S-parameters in the frequency domain on test vehicles with TRL calibration patterns sometimes need comparison with measurements done using other measurement techniques. In Section III, the method of dielectric characterization Split Post Dielectric Resonator (SPDR) is presented. The SPDR technique allows for only narrowband DK and DF measurements, and in this work SPDR results are obtained using a set of three different SPDRs - designed for 10GHz, 15 GHz, and 20 GHz. Measurements using travelling-wave technique on a stripline and SPDRs may results in different values of DK and DF for the same laminate dielectric. This is mostly related to anisotropy of PCB dielectric, since the electric field vectors in the SPDR and in the stripline have different orientations with respect to the glass fiber bundles in a resin matrix. Still, the comparison of the dielectric properties extracted using the SPDR approach and the traveling wave technique may be informative.

### 2. TRAVELING WAVE METHOD FOR PRINTED CIRCUIT BOARD CHARACTERIZATION

The systematic and random errors arising from the measurements using TRLcalibrated test vehicles over the frequency range below 20 GHz are comparatively low and almost do not affect the quality of designs using such PCBs. But as the upper frequency limit of measurements is increased from 20 GHz to 50 GHz, errors and uncertainties, associated with the measurement technique, may become significant. For obtaining adequate values of DK and DF (PCB) at higher frequencies (above 20 GHz), error assessment is needed.

The objective of this section is the analysis of errors, uncertainties, and limitations associated with this method.

## 2.1. REVISIT OF MATERIAL PARAMETER EXTRACTION PROCEDURE USING A TRAVELING WAVE METHOD

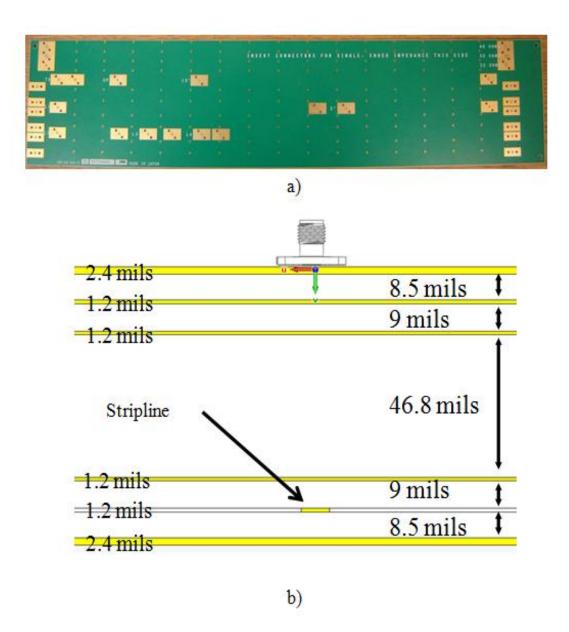

Dielectric material parameters (DK and DF) as functions of frequency over a wide frequency band are extracted herein using a technique based on a single-mode (TEM) propagation on low-loss transmission lines formed in PCBs. The scattering matrix parameters (S-parameters) of the specially designed test vehicles are measured in the frequency domain using a precision vector network analyzer (VNA). Currently, the frequency range of measurements is 50 MHz -20 GHz. Any test vehicle contains a comparatively long (16") single-ended stripline on a 6-layer PCB, and also a number of single-ended auxiliary lines of different lengths for the "through-reflect-line" calibration, which is called "a TRL calibration pattern" [4], [21]. The material parameter extraction procedure uses an algorithm, described in detail in [1]-[3].

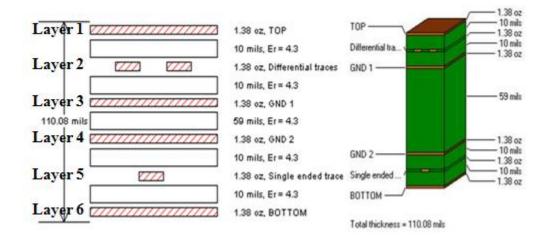

The picture of the test vehicle and the test board stack-up are presented in Figure 2.1.

Figure 2.1 The picture of the test vehicle and stack-up a) PCB outlook. b) PCB stack-up

The next steps after measuring S-parameters in the extraction procedure are converting them to ABCD transmission matrix parameters, and then calculating the complex propagation constant  $\gamma = \alpha + j\beta$ , where  $\beta$  is phase constant and  $\alpha$  is total attenuation constant.

For any transmission line, the total attenuation constant consists of the sum of the conductor loss and dielectric loss,  $\alpha = \alpha_T = \alpha_C + \alpha_D$ . The problem of separation of conductor loss and dielectric loss is considered in papers [1], [3] and will be also reviewed below in Section 2.2

As soon as the dielectric loss,  $\alpha_D$ , and the phase constant,  $\beta$ , are known, they can be used in DK and DF calculations.

The rigorous formulas for  $\beta$  and  $\alpha_D$  may be applied.

$$\beta = \frac{\omega}{c} \sqrt[4]{\varepsilon_r'^2 + \varepsilon_r''^2} \cdot \cos\left(\frac{\delta}{2}\right)$$

(2.1)

$$\alpha_D = \frac{\omega}{c} \sqrt[4]{\varepsilon_r'^2 + \varepsilon_r''^2} \cdot \sin\left(\frac{\delta}{2}\right)$$

(2.2)

By solving the system of these two equations for  $\varepsilon_r^{'}$  and  $\varepsilon_r^{''}$ , it is easy to obtain the dielectric constant  $DK = \varepsilon_r^{'}$  and dissipation factor  $DF = \tan \delta = \varepsilon_r^{''} / \varepsilon_r^{'}$  from

$$\varepsilon_r' = x \sqrt{\frac{x}{x+y}}$$

(2.3)

$$\varepsilon_r^{''} = x \sqrt{\frac{y}{x+y}}$$

(2.4)

where  $x = \frac{\beta^2 c^2}{\omega^2}$  and  $y = \frac{4c^2 \alpha_D^2}{\omega^2}$ .

Formulas (2.1) - (2.4) are derived in Appendix A. The formulas (2.3) and (2.4) correlate  $\varepsilon_r'$  and  $\varepsilon_r''$  with the phase constant  $\beta$  and dielectric loss on the line  $\alpha_D$ . However,  $\beta$  and  $\alpha_D$  are not measured directly. They are obtained by calculations using the measured S-parameters. The expressions for  $\varepsilon_r'$  and  $\varepsilon_r''$ , and  $\tan \delta$  in terms of the measured unwrapped phase and magnitude of the S<sub>21</sub> are

$$\varepsilon_r = \left(\frac{c}{2\pi}\right)^2 \left(\frac{\left[\varphi_{21}\right]_{unwrapped}}{l \cdot f}\right)^2$$

(2.5)

$$\varepsilon_r = \frac{c}{\pi \cdot 8.686} \frac{\sqrt{\varepsilon_r}}{l \cdot f} \left( -|S_{21}^{\ dB}|_D \right)$$

(2.6)

$$\tan \delta = \frac{\left(-|S_{21}^{\ dB}|_{D}\right)}{4.343 \cdot [\varphi_{21}]_{unwrapped}}$$

(2.7)

where  $[\varphi_{21}]_{unwrapped}$  is unwrapped phase of the measured  $S_{21}$  and  $(-|S_{21}^{dB}|_D)$  is the magnitude of measured  $S_{21}$ , which corresponds to a dielectric part of loss  $\alpha_D$ . Formulas (2.5) - (2.7) are derived in Appendix B

The advantage of the method specified in this work is that the calculations do not require solving complex electromagnetic problems with detailed analysis of scattering effects on conductor roughness. The extraction procedure is comparatively simple and could be applied for the experimental analysis of many different PCBs with fiberglass-filled epoxy-resin-based substrates.

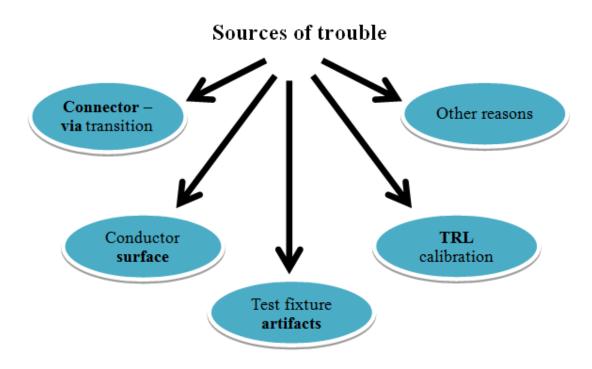

# 2.2. SOURCES OF TROUBLES AND ERROR ASSESMENT IN DK/DF EXTRACTION

The necessity of getting adequate  $\varepsilon_r$ ' (DK) and  $tan\delta$  (DF) on low-loss PCB over the frequency range up to 50 GHz is an important requirement for high-data-rate design. PCB material parameters in the current work have been extracted using the traveling wave technique, which was explained in Section 2.1. To estimate the systematic errors in measured DK and DF one can use the formulas presented in Appendix C. The derivation of these formulas is based on (2.5) - (2.7). TRL calibration is used to de-embed via and connector transitions. Most of the errors and uncertainties will be more significant after increasing the frequency range of measurements from 20 GHz to 50 GHz.

In Figure 2.2 sources of trouble are systematized.

Figure 2.2 Sources of errors and uncertainties

**2.2.1.** Non-Ideal Effects Due To Via-Connector-Trace Transitions. Before the signal propagates through the PCB trace, it passes through the via-connector-trace structure, which may affect the measured S-parameters on the line, and eventually contribute to the errors in the extracted DK and DF of a dielectric under test. Even if the TRL calibration is applied, an improper via transition design may affect signal loss and mismatch and cause errors and unwanted limitations. Thus, via transition structure may limit frequency range of measurements, and may even cause the TRL calibration failure.

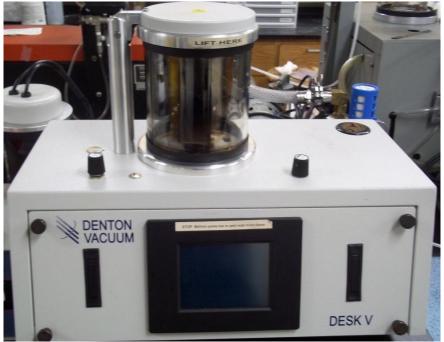

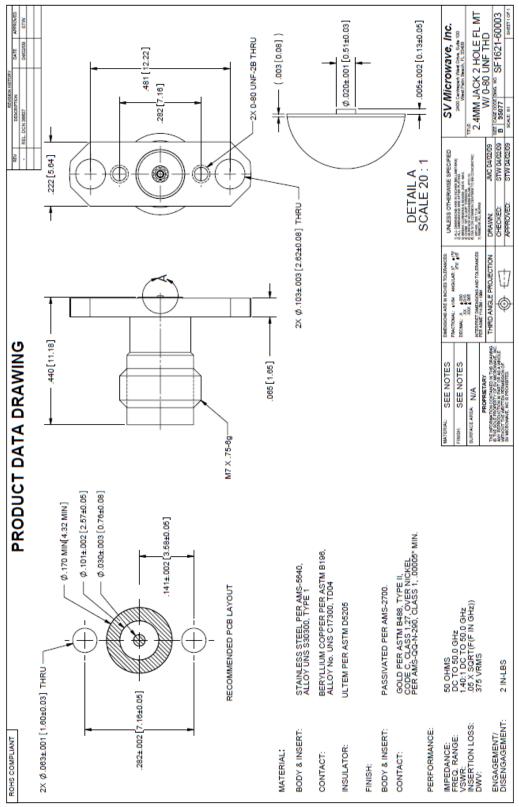

In the current measurement setup, 3.5-mm surface mounted SMA connectors have been used. The upper limit for the 3.5-mm SMA connector is 26.5 GHz. This is sufficient for the current measurement setup up to 20 GHz, but these connectors cannot be applied for the measurements up to 50 GHz. That means that the type and characteristics of a connector are the factors determining the frequency limitation. For a measurement setup with frequency range up to 50 GHz, 2.4-mm SMA connectors with frequency limit at 50 GHz should be chosen.

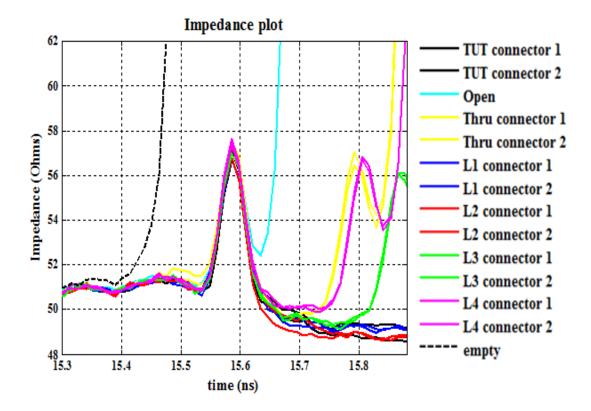

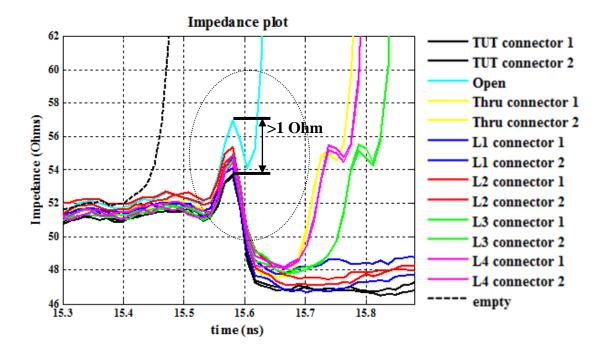

Even if the connectors applied to a PCB have proper characteristics over the entire frequency range, they still can be a source of uncertainty. An important assumption for the TRL calibration is that all the ports are of the identical geometry, which means the identity in the impedance of all the connectors. Non-uniformity of mounting connectors to a PCB and manufacturing tolerances can result in non-repeatability of time-domain response from the connectors. Figure 2.3 demonstrates an acceptable mounting of all the connectors, since impedance responses from all the connectors are quite similar. The deviation in impedance of these connectors is within 0.5 Ohm – 1 Ohm in the time span from 15.4 ns to 15.61 ns. In the case of unacceptable mounting, the impedance deviation

of all connectors will be higher than a few Ohms. Example of unacceptable mounting is plotted on Figure 2.4.

Non-uniformity of mounting can be caused by a mismatch between a via pad and the connector inner pin. For an ideal transition connector, a pin and a via pad should have the same sizes and need to be perfectly aligned. Unfortunately, in practice, it is difficult to satisfy those conditions for surface-mounted connectors. Misalignment and size mismatch reduce the area of contact. One of the other possible troubles is an air gap between a connector pin and a via pad. This could be a result of using a broken connector, which has its inner pin pushed inside, or this may be a via pad manufacturing error.

Figure 2.3 Acceptable connector mounting to PCB

Figure 2.4 Non-acceptable connector mounting to PCB

Even if the signal successfully passes the transition between the connector pin and the via pad, there is still a possibility of having an unwanted resonance in the insertion loss in the high-frequency part of the frequency range of operation. This resonance could be caused by a via stub.

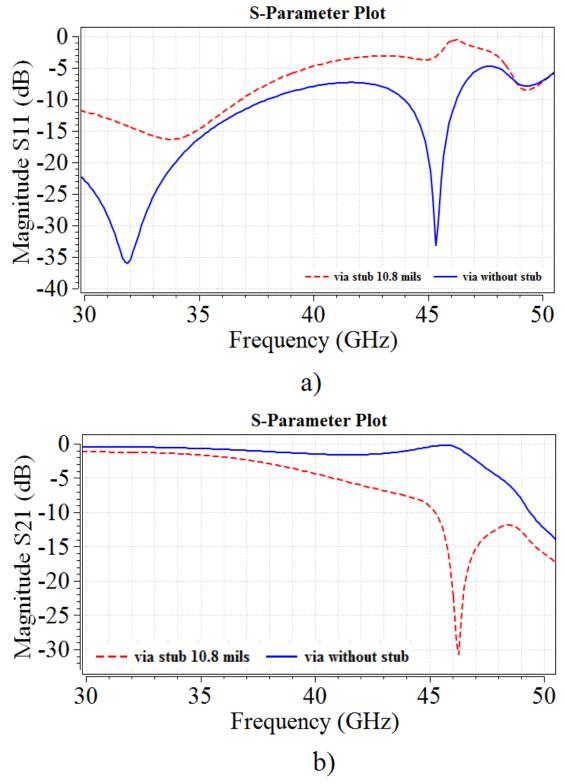

To demonstrate the resonant effect of the via stub, the simulated insertion loss curves for the 80.5 mil via with 10.9 mil stub and without any stub are presented in Figure 2.5. The difference between two curves around 45 GHz is significant.

It is a common practice to reduce the via stub length by back-drilling the stub as close as possible to the signal layer. In Figure 2.6-2.8, the comparison of the measured zero-length 'through' line for the same PCB, but in different scenarios, is presented (with a via stub vs. without via stub).

Figure 2.5 Modeling of the via with a stub and without any stub (MVTT tool)

Figure 2.6 Comparison of the return loss for the PCB with 10.9mils via stub and PCB with back-drilled via (the same material and geometry of the test vehicles)

Figure 2.7 Comparison of the insertion loss for the PCB with 10.9mils via stub and PCB with back-drilled via (the same material and geometry of the test vehicles)

Figure 2.8 Comparison of the phase of the insertion loss for the PCB with 10.9mils via stub and PCB with back-drilled via (the same material and geometry of the test vehicles)

After applying the back-drilling technique, the return loss has improved at frequency above 40 GHz. Insertion loss and phase of insertion loss has been stabilized up to 40 GHz, and slightly improved above 40 GHz. Measurements have been made with the same setup settings. That allows to see improvement in results, after reducing the length of the via stub, what has been proven by above shown plots.

**2.2.2.** Non-Ideal Effects Due To TRL Calibration Pattern Design. Some of the uncertainties and effects related to imperfect via transitions mentioned above can be avoided applying 'through-reflect-line' (TRL) calibration, unless the via transition defects lead to the failure of the TRL calibration. The TRL calibration is the most effective method to remove the port effects from the measurements. However, the TRL calibration patterns have to be design properly according to certain rules.

All the test vehicles in this study have the same TRL calibration pattern, comprised of a number of auxiliary single-ended lines of different lengths on the same PCB under test. For the current test vehicle design, the TRL pattern contains a "through line" (TL), an "open line" (OL), and four lines with different lengths specified for different frequency ranges. The existing TRL patterns have been initially designed for the operation up to 50 GHz, but assuming that the laminate PCB dielectric has the DK value equal to 4.0, and this DK value is constant over the entire frequency range. However, it is well known from the experience, that the DK value of the laminate dielectrics is a frequency-dependent parameter, and the DK typically decreases as frequency increases. For different values of DK, the calculated lengths of the TRL calibration lines will be different. Table 2.1 represents the results of the TRL patterns calculations for different DK values (3.5, 4.0, and 4.5).

|                  | Frequency<br>range, GHz | $\varepsilon' = 3.5$       | ε' = 4.0                | ε' = 4.5                   |        |

|------------------|-------------------------|----------------------------|-------------------------|----------------------------|--------|

| TRL Line         |                         | Length of the<br>line, mil | Length of the line, mil | Length of the<br>line, mil |        |

| Line 1           | 0.0500                  | 10122                      | 10122                   | 9506.1                     | 8996.2 |

|                  | 0.2812                  | 10122                      | 9500.1                  | 6990.2                     |        |

| Line 2           | 0.2812                  | 2285                       | 35 2175.5               | 2084.9                     |        |

| Line 2           | 1.5811                  |                            | 2203                    | 2175.5                     | 2004.9 |

| Line 3           | 1.5811                  | 891.42                     | 801 / 2                 | 871.95                     | 855.82 |

| Line 5           | 8.8914                  | 071.42                     | 071.95                  | 055.02                     |        |

| <b>T</b> · · · · | 8.8914                  | (12.60                     | C40 14                  | (27.07                     |        |

| Line 4           | 50                      | 643.60                     | 640.14                  | 637.27                     |        |

Table 2.1 Line length calculations for different DK values

The other assumption for the TRL calibration pattern design is that the impedance for all lines is the same. However, the manufacturing process does not always guarantee the same impedance over all the traces or even the translational invariance of impedance along any trace. This means the impedance difference on different lines may result in some uncertainty of measurements. The impedance of the traces as a function of time is tested using the Time Domain Reflectometer (TDR) equipment. These tests allow an operator for understanding whether there is an impedance-difference, and the impact it has on the measurements. According to the measured data, represented in Figure 2.9, the trace impedances vary within several Ohms for the lines of the TRL calibration patterns.

The identical signal propagation through connectors and traces is the most significant criterion for designing the appropriate TRL calibration patterns. The violation of this criterion would decrease the quality of the TRL calibration and lead to errors and uncertainties. Further experimental investigation is needed to estimate numerically the degradation of the calibration.

Figure 2.9 Impedance measurements using TDR

**2.2.3. Effects Due to Conductor Surface Roughness.** Errors and uncertainties could occur due to not taking into account surface roughness of the conductor in the extraction algorithm. The conductor surface roughness starts to significantly affect the extracted DF values (and less for the DK values) at frequencies above approximately 5 GHz.

However, to correctly separate conductor loss  $\alpha_c$  and the pure dielectric loss  $\alpha_D$  from the total measured loss  $\alpha_T$  has always been a challenge. Currently, in the material parameter extraction method adopted in this work, there are two ways of separation of the conductor and dielectric loss.

The first is the so-called "**root-omega**" approach [2]. In this case, conductor surface roughness is not taken into account. The total loss is curve-fitted by the three terms proportional to the powers of the angular frequency,  $\sqrt{\omega}$ ,  $\omega$ , and  $\omega^2$ , as  $a\sqrt{\omega}$  +

$b\omega + c\omega^2$ . The conductor loss is assumed to be proportional to the  $\sqrt{\omega}$  term, as in the absolutely smooth conductor, and the dielectric loss behaves as the sum of the rest  $\omega$ , and  $\omega^2$  components. Though this approach has shown that it is not very accurate for significantly rough conductors, especially at frequencies above ~5 GHz, it can be applied in the case, when the conductor surface roughness is unknown and cannot be easily determined, and if the transmission line geometry is not known. This algorithm has been employed in the Matlab code to extract DK and DF parameters of the test vehicles, when the cross-sectional geometry of the test lines is not available, and the destructive cross-sectional analysis of the test boards is not possible.

If the test line cross-sectional parameters, such as the signal trace average width and thickness, the distances between the trace and the ground planes, the average peakto-valley roughness amplitude, and the spatial quasi-period of the surface roughness function, are known, then a small perturbation model based on Sanderson's theory of roughness as a periodic or random function can be applied [22]. In the current version of the Matlab code, which is developed for the DK and DF extraction, the Sanderson's small perturbation technique has been realized for the one-dimensional sawtooth roughness functions [1].

An overview of both methods in the procedure for extracting dielectric parameters from measured S-parameters using VNA is presented in the flowchart published in [3], and this flow-chart is also presented in Figure 2.10.

However, any analytical or numerical model of surface roughness is an approximation to some extent, because it is extremely difficult, if not impossible, to characterize surface roughness, which has the statistical nature, by any deterministic parameters, which could be included in a model. For this reason, experiment-based techniques to separate conductor and dielectric loss may be reasonable alternatives to analytical and numerical techniques [3].

Figure 2.10 Flowchart of the procedure for extracting dielectric parameters from Sparameters [3]

As is mentioned above, in the "root-omega" procedure, the conductor loss is associated with  $\sqrt{\omega}$  behavior, while dielectric loss is retrieved from the  $\omega$  and  $\omega^2$  terms in the total curve-fitted loss. But in reality, conductor loss always deviates to some extent from the pure  $\sqrt{\omega}$  behavior, since conductor roughness lumps into  $\omega$  and  $\omega^2$ , as is shown in [3]. If the conductor roughness profile is known, e.g., retrieved from mechanical or laser profilometry, optical microscopy, scanning electron microscopy, or even more advanced atomic-force microscopy, then the conductor loss could be modeled using an adequate numerical or analytical method. Alternatively, a new experimental technique "DERM", proposed by Dr. M. Koledintseva and published in [3], can be applied, if at least three test vehicles with identical geometries and identical dielectric, but different conductor roughness profiles are available. It is also possible to separate conductor loss and dielectric loss, if at least three test vehicles with the same conductor roughness and the same dielectric, but different trace widths, are available ("DERM-W" technique) [23]. Then the dielectric loss would be simply calculated by subtraction of the conductor loss from the total loss [2].

Currently there are three main groups of foils used in industry. The difference between those groups is in the level of the foil roughness. The convenient parameter to characterize surface roughness is average peak-to-valley  $R_z$ . It is defined as

$$R_{z} = \frac{\sum_{i=1}^{5} |Y_{i}^{peak}| + \sum_{i=1}^{5} |Y_{i}^{valley}|}{5}$$

(2.8)

where  $Y_i^{peak}$  are the amplitudes of the five highest peaks, and  $Y_i^{valley}$  are the amplitudes of the five deepest valleys of the roughness profile [3], [9].

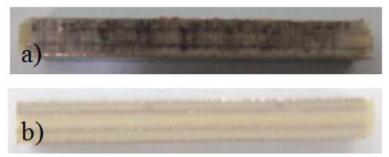

The first group is the standard (STD) foil, which has the highest roughness. The typical level of its  $R_z$  is on the order of ~10 µm and may be even exceeding10 µm. The second group has medium roughness with  $R_z \sim 5 - 10$  µm and includes foils with very low profile (VLP) and reverse treated foil (RTF). The third group includes the smoothest hyper very low profile (HVLP) foils with  $R_z$  up to 5µm.

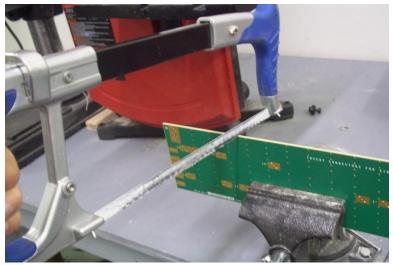

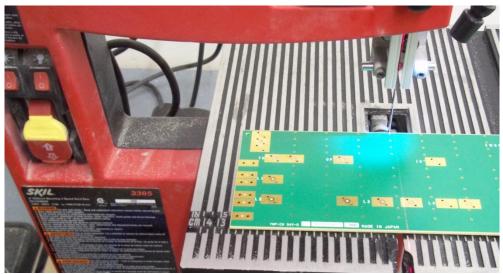

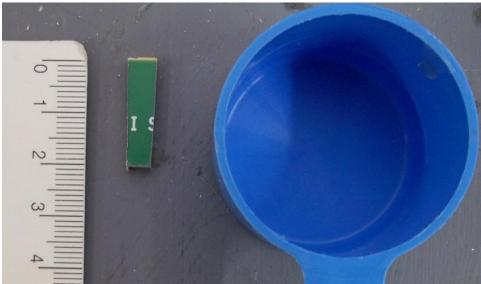

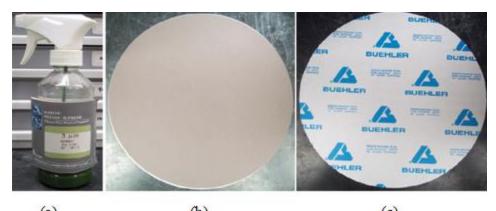

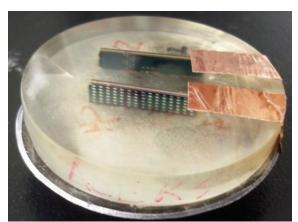

There are several different methods to retrieve the information about conductor surface roughness. In current work, surface roughness data has been extracted from the scanning electron microscopy (SEM) images of trace cross section. The algorithm of preparing samples for SEM cross-sectional analysis is described in Appendix D. Figure 2.11 presents the cross-sectional images of three foil classes obtained using the Hitachi 4700 SEM machine, available at the Missouri S&T Materials Research Center.

The algorithm which has been used to extract surface roughness data from SEM images in the current work is implemented in a semi-automatic tool. Stripline geometry and surface roughness information could be retrieved from an SEM image using this tool. Detailed description of the tool is published in [9].

To understand the importance of including surface roughness loss in calculating total loss, a set of test vehicles with identical dielectric of the same resin content and fiber-glass structure, and the same single-ended stripline geometry were measured. The conductors on all PCB were made of electrodeposited copper. These test vehicles differ only by the type of copper foil roughness: STD, VLP, and HVLP. Difference in measured data would be only due to the difference in roughness.

The difference in the insertion loss  $(S_{21})$  leads to the difference in the corresponding extracted dielectric constant (DK) and dissipation factor (DF) values, if

applying the "root-omega" extraction procedure, which does not take into account surface roughness. This is described in [10] and can be seen in Figure 2.12. The difference in the slopes of the insertion loss curves in Figure 2.12 is solely due to the surface roughness, since these three test vehicles have the same geometry and the same dielectric.

Figure 2.11 Cross-sectional SEM images of three types of foil used in current work

If surface roughness is not taken into account and the "root-omega" algorithm is applied, the DK and DF values for exactly the same dielectric turn out to be different, as is seen from Figure 2.13. This ambiguity is the consequence of the fact that the surface roughness is not "extracted out" of the DK and DF values properly. The "root-omega" procedure does not separate dielectric loss from conductor surface roughness loss. The latter is lumped in the DK and DF values.

Figure 2.12 Insertion loss (S21) comparison between different types of foil

When the differential extrapolation method "DERM" [3] was applied to separate dielectric and rough conductor losses in printed circuit boards, this method allowed for extracting the pure dielectric losses, the same for all the test vehicles, independently of

the conductor roughness. The resultant value with "zero roughness" could be used as a reference in comparison with rough STD, VLP, and HVLP foils. The extracted DK and DF of the pure, "free from the roughness", PCB laminate dielectric (in this case it was Megtron 6) are presented in Figure 2.13 as a purple dashed line. The DK value matches the one for the test vehicle with the HVLP foil, which has the lowest surface roughness, and thus was taken as the true dielectric constant value for the further DF extraction. The true dielectric data extracted using the DERM technique is lower than the DK and DF values extracted using the "root-omega" procedure, because in the DERM technique the surface roughness is removed.

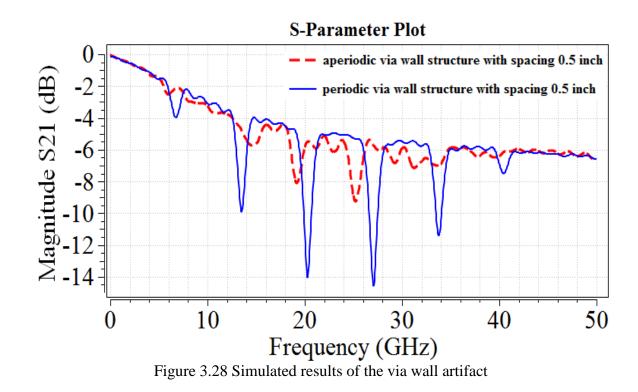

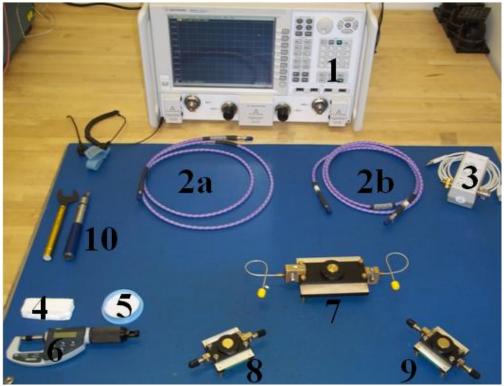

**2.2.4.** Non-Ideal Effects Due To Test Fixture Artifacts. A transmission line with losses has a transmission coefficient, the magnitude of which decreases monotonically with frequency, or the magnitude of the insertion loss (in dB below zero) should be a monotonous function of frequency. However, the insertion loss (|S21|, dB) curves, measured on the majority of the PCB test vehicles designed for this project, are not monotonous: some periodic resonances can be seen. The same periodic "peaks" can be seen on the return loss (|S11|, dB) curves. These artifacts are shown in Figure 2.14. The measurements are done using Agilent E8364B 50-GHz Precision Network Analyzer (PNA).

It has been noticed that these artifacts have the resonance shape, and they repeat approximately every 3.1 GHz. Any discontinuities close to the transmission line could cause reflection of the wave traveling along the line. In fact, in the current PCB design there are equidistant ground vias located along the transmission line with one-inch spacing. Pairs of ground vias form <sup>1</sup>/<sub>2</sub> wavelength resonator for the TEM mode.

Figure 2.13 Dielectric parameters extracted using different methods to compare rough foils with perfectly smooth conductor a) DK. b) DF

The fundamental mode frequency of such resonator, assuming that the dielectric constant of the test board dielectric is around 4.0, can be estimated as

$$f_0 = \frac{c}{2L\sqrt{\varepsilon_r}} = \frac{3 \cdot 10^8 \frac{m}{s}}{2 \cdot 0.0254m \cdot \sqrt{4}} \approx 3.1 \ GHz \tag{2.9}$$

where L is the length of the spacing between ground vias, and c is a speed of light in the free space.

Figure 2.14 S-parameters measured over 16 inch transmission line. Artifacts are highlighted by red circles. a)Return loss. b) Insertion loss

The resonance frequency, calculated in equation (2.7), is very close to a frequency of artifacts in the measurements. An interesting observation is that the magnitude of these resonances increases as surface roughness increases, thus, for the test vehicles with STD foil these artifacts are more pronounced than for the test vehicles with VLP and HVLP foils. This effect suggests that the surface roughness "helps" to dissipate (absorb) energy stored in these "resonators" formed by the stripline and corresponding periodic via wall.

## 2.3. OVERVIEW OF ERRORS AND UNCERTIANTIES ASSOCIATED WITH TRAVELING WAVE METHOD, AND POSSIBLE SOLUTIONS

Analysis of errors, limitations, and uncertainties is important for making accurate measurements, as well as for improving a test vehicle design. Sources of troubles, which have an effect on current measurements up to 20 GHz, definitely will have an impact on the results of measurements as frequencies increase, and will be even more important when designing a new test vehicle for measurements up to 50 GHz. The main goal of the current work is to design such a test vehicle to be able to conduct measurements up to 50 GHz using a VNA. To achieve this goal, the factors, described above, need to be taken into account in a new design.

Table 2.2 summarizes the most significant problems and possible solutions, applicable both to the 20-GHz and 50-GHz test vehicles. Most of the solutions have been taken into account in the new PCB test vehicle design, and they will be detailed in Section III.

| Challenge                                  | Possible solution(s)                         |  |

|--------------------------------------------|----------------------------------------------|--|

| Unwanted resonances in S-parameters due    | Eliminate stubs in a new test vehicle design |  |

| to via stub                                |                                              |  |

| Surface roughness artifacts in Df          | Use smooth foils and/or separate conductor   |  |

|                                            | roughness loss from dielectric loss          |  |

| Unwanted periodic resonance in S-          | Eliminate via wall in a new test vehicle     |  |

| parameters due to via wall                 |                                              |  |

| Sensitivity of TRL calibration patterns to | Study of errors by numerical/analytical      |  |

| small errors in mounting and               | simulations                                  |  |

| manufacturing                              |                                              |  |

| Phase offset at very low frequencies and   | Determine errors                             |  |

| phase instability                          |                                              |  |

| Mismatch effect                            | Determine maximum acceptable RL and          |  |

|                                            | associated errors                            |  |

| Insufficient line length                   | Determine minimum line length and errors     |  |

|                                            | associated IL and phase of $S_{21}$          |  |

Table 2.2 Challenges and possible solutions

## **3. DESIGN OF A TEST VEHICLE UP TO 50 GHZ**

An increase of the bandwidth of the PCB test fixtures to get more wideband PCB laminate dielectric characterization is one of the biggest practical challenges. In the past few years, the data rate of high-speed electronics using PCBs has reached 25 Gb/s and that number is steadily increasing. This increase necessitates the study of PCB dielectric parameters at frequencies no less than 50 GHz.

The present-day PCB test vehicle design, with a frequency range limited to 20 GHz, needs to be improved. And the frequency range should be extended to 50 GHz. Those features of the design which should be improved will be described in this section.

## 3.1. OVERVIEW OF BOTH THE GEOMETRY AND STACK-UP OF CURRENT PRINTED CIRCUIT BOARD DESIGN

The single-ended stripline test vehicle was developed to investigate the behavior of dielectric parameters, such as both DK and DF, up to 20 GHz. Printed circuit boards had the same stack-up and layout, which are fully explained in [1] and [11]. The crosssectional geometries, conductor roughness (due to different foils), and a laminate dielectric are individual on each printed circuit board. Dielectric material of the same type and from the same manufacturer, taken from different batches, may contain differences in their dielectric characteristics.

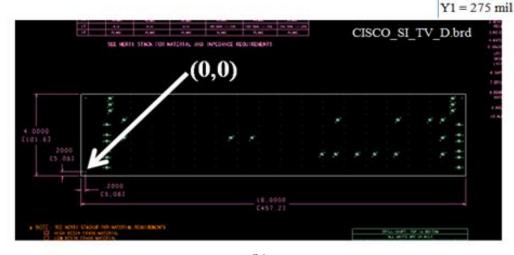

Both the dimensions and layout of the 6-layer PCB test vehicle currently used for PCB material characterization are presented in Figure 3.1. The length of the trace under test was approximately sixteen inches (15,410 mils). Both launching and receiving ports

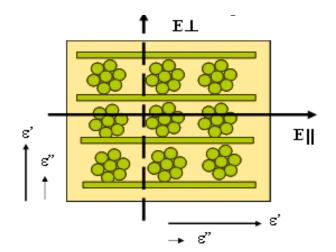

with surface mount connectors were placed on both sides of the trace. Layer 2 in the stack-up contains three single-ended striplines, each with a different trace width to reach the target impedance of 48, 50, and 52 ohms. The difference in trace impedances allowed for choosing the trace with the impedance closest to 50 ohms, even if the manufacturing process would have an error. Likewise, differential pairs with 96, 100 and 104 ohms impedances are presented on Layer 5.

Besides the single-ended and differential traces under test on the PCB, there are the TRL calibration patterns, as well as additional five-inch and ten-inch single-ended striplines

Figure 3.1 Dimensions and layout of the test vehicle. Traces under test are highlighted with yellow color, TRL calibration patterns are dark blue, launch for differential pairs are blue, and additional traces are red.

Knowing the TRL calibration patterns allows for the de-embedding of systematic errors associated with both the inductance and capacitance of the launch vias and connectors. In principle, measurements can be taken using any type of calibration. The position of the reference planes for E-calibration (or the coaxial SOLT calibration) is

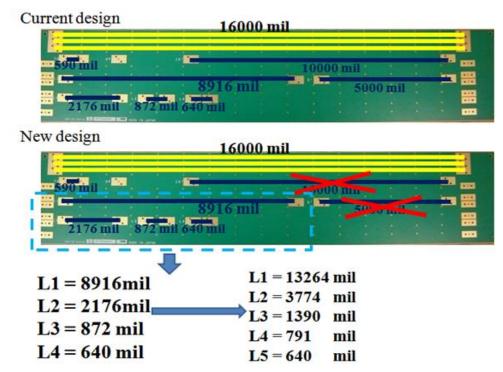

typically at the end of the precision cables, connected to the 50-GHz VNA. This calibration includes uncertainties of connectors and via-to-trace transition. TRL calibration allows for shifting the reference plane from the cable connectors further into the trace. That takes port effects away from the measurements. Patterns were designed so that the frequency range from 50 MHz to 50 GHz is divided into four segments. The length of each TRL calibration line was calculated according to the relative frequency breakpoints. Figure 3.1 illustrates that there were four TRL lines. Hence, there were five frequency breakpoints. 'Line 1' was 8416 mil (213.7 mm) long. The frequency range was between 50 MHz and 281.17 MHz. 'Line 2' was 2176 mil (55.3 mm). This frequency range was between 281.17 MHz and 1.581 GHz. The frequency range from 1.581 GHz up to 8.891 GHz is covered by the 872-mil (22.1-mm) long 'Line 3'. 'Line 4' is 640 mil (16.3 mm). The frequency ranges was between 8.891 GHz and the stop frequency of 50 GHz. There were'Through' and 'Open' standards with frequency ranges between 50 MHz and 50 GHz. The lengths of those standards were 590 mil (15 mm) and 295 mil (7.5 mm), respectively.

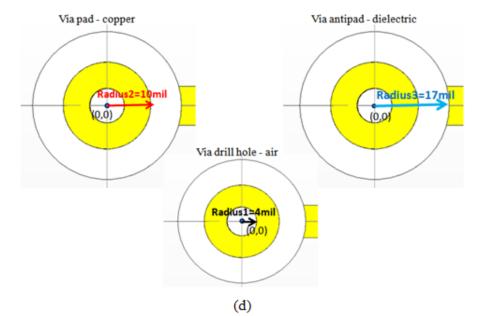

During both the calibration and measurements, the precision cables were attached to the SMA connectors using a torque wrench, minimizing variation in the contact resistance. The launching structure presented as a pad surface was designed to accept a flange-mount, compression-fit SMA connector. In the outer-layers, the pad size of Layer 1 and Layer 6 was 30 mil (0.765 mm). For any other inner layers, the diameter of the signal via was 9.8 mil (0.25 mm). An antipad had 100-mil (2.54-mm) diameter. This was intended to isolate the signal via from any ground and reference layers. If measurements are up to 20 GHz, it is sufficient to use the SMA connector MOLEX SN 73251-1850.

The maximum frequency for operating this connector is 26.5 GHz, according to a manufacturer's official rating. The dimensions and the overview of the connector are shown in Figure 3.2. The metal body of the connector provided the return path. Two plated-through holes for screws were drilled through all six layers. Each connector was mounted using two screws of certain dimensions. The quality of the signal transition between the connector and PCB via pad primarily on the quality of screws and connectors. Before making calibration and measurements, it is very important to make sure that the connectors and screws are not broken or damaged, otherwise, the calibration procedure have falied and measurements would have been incorrect.

Figure 3.2 Geometry and overview of the SMA connectors. (a) Recommended PCB layout. (b) Schematic of geometry of the connector (c) Outlook of the connectors.

The PCBs under study had the six-layer structure. According to the test vehicle stack-up, the connectors were to mounted on Layer 6, when single-ended traces are under

test and on Layer 1, or when the differential pairs are to be tested. Choosing the proper side for mounting connectors would minimized the length of the via stub.

The design of the stack-up, illustrated in Figure 3.3, contained the balancedstripline signal traces on Layer 5 (impedance-tuned for 48, 50 and 52 ohm). On Layer 2, the single-ended traces were replaced with an analogous structure of the differential pairs (impedance-tuned for 96, 100, 104 ohm). Layers 1, 3, 4, and 6 have the identical ground planes. Between Layers 1 and 2, as well as between Layer 5 and 6, there are prepregs with approximately 50% finished resin content. Copper-clad cores comprised both Layers 2 and 3 and Layers 4 and 5. They were chosen as close as possible to the 50% resin content. The dielectric between Layers 3 and 4 provides the mechanical rigidity to a finished board, and has no influence on measurements. This is the reason of not using expensive dielectrics to fill the spacing between Layers 3 and 4. Only prepregs and cores were located between Layers 1 and 2 and Layers 2 and 3, have an impact on measurements of the single-end stripline, described in this work.

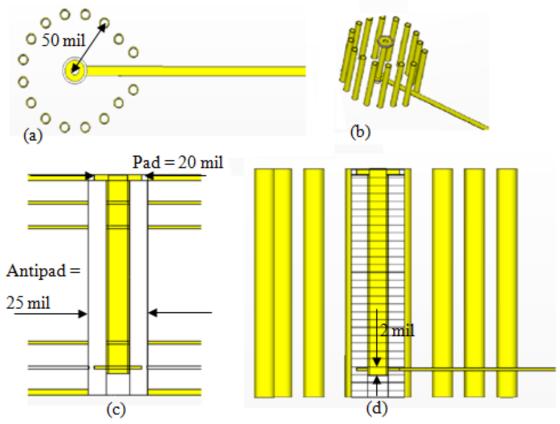

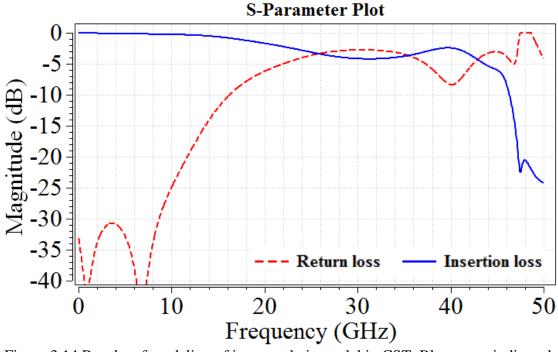

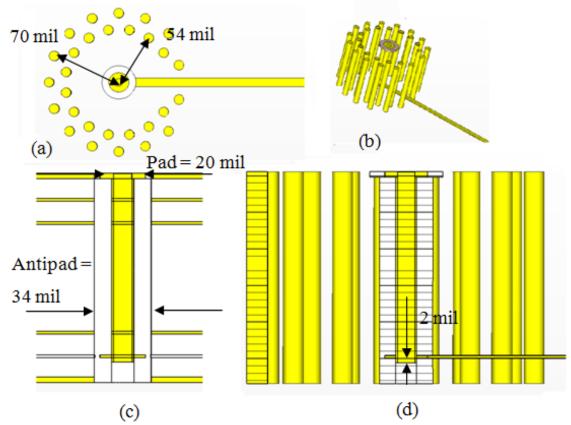

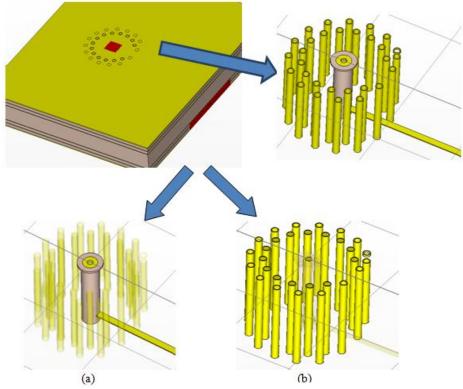

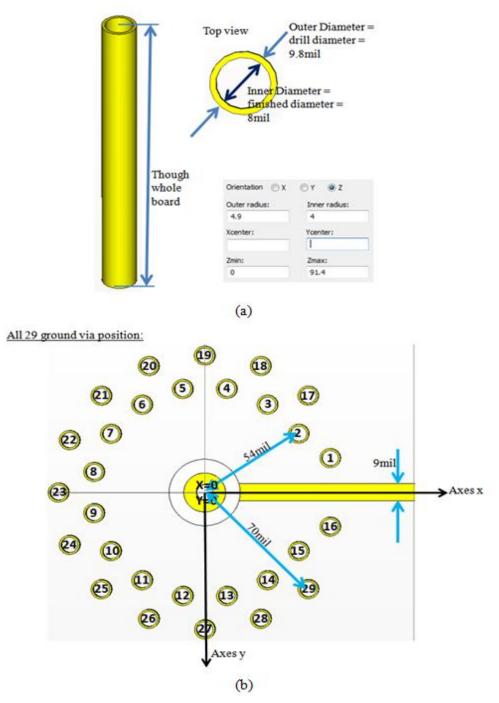

Besides the connector frequency limitation, the maximum frequency range for measurements was also determined by the signal via design. Herein, the via design was optimized to work up to 35 GHz, which is sufficient for measurements up to 20 GHz. The via structure needed to be significantly modified to provide measurements up to 50 GHz. Both the design and dimensions of the signal via are presented in Figure 3.4

A circle of eight ground stitching vias, passing though all six layers of the PCB, was located outside of the anti-pad. Both provided shielding of the signal via and raised the current return path. Eight ground stitching vias were equally distributed in a circle. All sizes were calculated and optimized using a Multilayer Via Transition Tool (MVTT). This tool is described in [12] and will be discussed further in Section 3.2 of this work. As a reference for the dielectric constant, DK has been defined as 4. The signal via went through six layers. But the single-ended trace is located on Layer 5. The via part from Layer 5 to Layer 6 was the via stub. The size of via stub is 10.8 mil. The resonance frequency associated with via stub, in this case, is above 35 GHz.

Figure 3.3 Stack-up details of 6-layer PCB

Via have been designed to work up to approximately 30 GHz. In practice, however, the measurements become incorrect around 33 GHz. Today's industry needs to know dielectric parameters up to 10 GHz for designing more accurate models. The frequency range of the current measurements is from 10 MHz till 20 GHz, both covers the point of interest for the industry and stays below the maximum frequency point. Even if the TRL calibration de-embeds the port effects, including via transitions, the characteristics of the via transition must still be known. If the return loss at a certain frequency is- significantly high (approximately more than -7 dB), and the insertion loss is

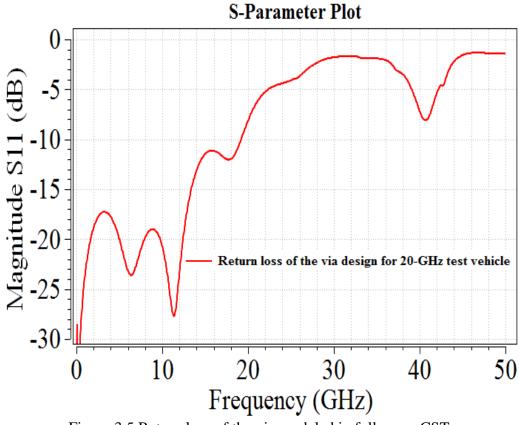

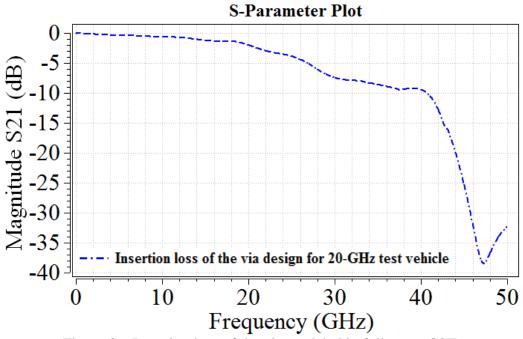

low (approximately -10 dB), sufficient amount of signal could not pass the via, this and calibration would fail. To understand the behavior of the via transition up to 50 GHz, the model has been designed using the full-wave numerical electromagnetic software CST Microwave Studio. Via has been modeled with the same geometry as in the MVTT optimization tool with the 300-mil stripline. From the plots presented in Figure 3.5 and Figure 3.6, the via transition could be analyzed with a certain percentage of accuracy.

Figure 3.4 CST model of the via structure for 20-GHz test vehicle a) Prospective view. b) Top view. c) Side view

Up to 20 GHz the return loss is below -10 dB, allows for getting the TRL calibration and extracting the relatively correct data from measurements. The TRL calibration fails at about 28 GHz, because the level of the return loss is significantly high.

Figure 3.5 Return loss of the via modeled in full-wave CST

Looking at the insertion loss in Figure 3.6, it is easy to notice that after 28 GHz there is much loss. Having the insertion loss around -10 dB would not provide a sufficient signal for either calibration or measurements. The return loss characterizes the magnitude of the signal reflected from the via structure, and the insertion loss shows how much signal would go through the transmission line. In practice, it is very useful to have the higher return loss (magnitude of  $S_{11}$  is approximately below -8 dB) and the insertion loss as low as possible (less than 6 dB). If the magnitude of the return loss exdceeds the magnitude of the insertion loss, that more energy is reflected from via structure than it is going through the via. The effect of the increased mismatched loss on the systematic

Figure 3.6 Insertion loss of the via modeled in full-wave CST

Figure 3.7 Insertion loss and return loss of the via modeled in full-wave CST on the same comparison graph

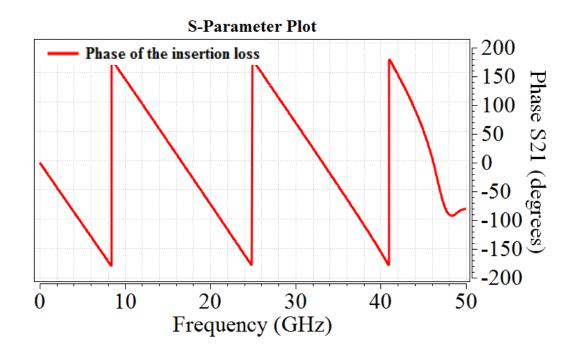

Another important indicator of the via transition quality is the phase of insertion loss. This loss needs to be both stable and linear over the entire frequency range. Figure 3.8 illustrates a phase of insertion loss for the modeled via. Linearity of the phase fails around 26-27 GHz.

Simulation of the via transition in the full-wave simulation tool in CST Microwave Studio was made. Modeling shows the approximate frequency limit of the via structure and characterizes the optimized via geometry. The frequency range of the current measurements was below 26 GHz. This may provide a good quality of measurements.

Figure 3.8 Phase of insertion loss of the via modeled in full-wave CST

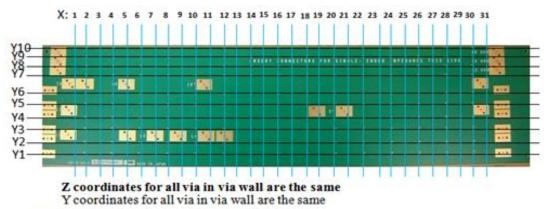

In addition to stitching ground vias around the signal via, there are other ground vias on the board which provide the current return path. All vias are equidistant with one inch spacing between vias. Such geometry of the via wall creates a resonance effect, detailed in Section 2.2.

As previously mentioned, the primary goal of this work was to design a new PCB test vehicle with a frequency limit up to 50 GHz. For accomplishing this goal, the current design of the test vehicle, described in Section 3.1, will be used as a reference. Analysis of errors and uncertainties, explained in Section 2.2, will be taken into account to avoid additional problems with the test vehicle design.

## **3.2. MODIFICATION AND IMPROVEMENT OF TEST VEHICLE DESIGN**

Test vehicles with the current design up to 20GHz were used to obtain dielectric properties with measurements up to 20 GHz. The frequency limit of the existing PCB test vehicles with current design up to 20 GHz is approximately 26-30 GHz. This frequency is dependent on the dielectric constant of the PCB laminate dielectric material.

The decision to improve the design was made after analyzing limitations and possible uncertainties in measurements due to the current 20-GHz test vehicle design. Both signal via and via stub had significant influence on the cut-off frequency of the measurements. The design of the signal via needed to be modified to allow for measurements up to 50 GHz. However, even if the via design is improved, calibration and measurements still may fail unless new, proper connectors are used. The cut-off frequency of the SMA connectors used in the current test vehicle design was

approximately 35 GHz. 2.4-mm connectors with a 50-GHz cut-off frequency were used for the new PCB test vehicle design. A new TRL pattern was designed for calibration over a frequency range between 50 MHz and 50 GHz. According to the error analysis presented in Section 2.2, via wall in the test vehicles also needed to be modified. Periodic one-inch spacing between stitching ground vias creates unwanted resonances every 3.1 GHz.

Summary of future improvements presented in Figure 3.9.

Figure 3.9 Summary of the issues for improving

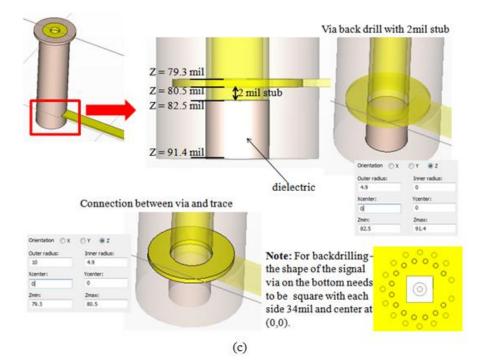

**3.2.1. Improvement In Via Design.** Design and optimization of a connector launch structure up to 40-50 GHz is challenging. Distance from the center of the signal via to center of each stitching ground via (which forms a coaxial structure around the signal via) needs to be calculated and optimized. As well as size of pad and dimensions of anti-pad. The algorithm to develop a new via structure is given in Figure 3.10.

The genetic algorithm (GA) employed in the MVTT (Multi-via transition tool) software has been used for the first-stage optimization. The full description and manual

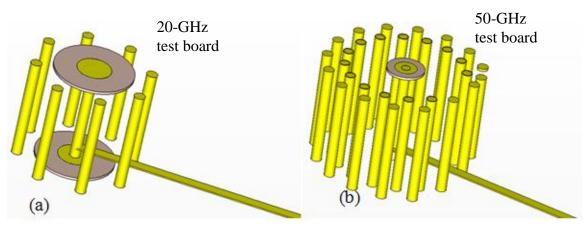

for the MVTT have been published in [12]. After using the MVTT as the first stage of the optimization, the full-wave electromagnetic simulations using the CST Microwave Studio, both in frequency domain and in time domain, were then run to verify results of the MVTT optimization. At the final stage, the CST model was tuned to achieve the best possible results. The final version of the via design was compared to the via model used in the 20-GHz test vehicles.

Figure 3.10 Algorithm of the new via design development

The advantage of the MVTT tool is a wide variety of input parameters. Structure's model, however, should remain comparatively simple. A 70 Ghz stop frequency was for the new design. In the previous via design for 20-GHz test vehicle this frequency was set as 40 GHz. The dielectric parameters of the laminate dielectric on the test vehicle were set at DK=3.5 and DF=0.005. In the previous design these values were DK=4.25 and DF=0.095. Stack-up information for the 50-GHz test vehicle remained the same as that for the 20-GHz test vehicle.

Figure 3.11 illustrates three ground via configurations analyzed using the MVTT. A 50 mil distance between the signal via and the stitching ground via was chosen as the initial parameter. During optimization, this parameter changed. The current design (20-GHz) has 8 stitching ground vias placed in a circle around the signal via. This design has been analyzed in earlier works: [8] and [11]. The ground via ring was intended to suppress the cavity mode created due to the coaxial structure around the signal via. In the case of 8 ground vias located 50 mil away from the signal via, the resonance will be at approximately 40 GHz. To increase the shielding effect of ground vias around the signal via, the number of ground vias will be increased as well. However the distance between the ground vias in the model with 24 ground via (as in Figure 3.11 c), is too small. That spacing does not meet manufacturing requirements regarding the minimum distance in the layout. The optimal model presented in Figure 3.11 (b) is the ring of 16 stitching ground vias.

Optimization of only the geometry of a single ring ground via and varying a number of vias does not result in the optimal via design. Such optimization only gives expectations for a future design of 50-GHz test vehicle. Figure 3.12 is a snapshot of both

the numerically calculated return loss and the insertion loss using the MVTT for the model of 16 ground stitching vias. According to these calculations, the resonance frequency of the natural cavity mode is near 50 GHz, however, (see Figure 3.12 b) the unwanted resonance occurs at 46 GHz. This resonance is due to the 10.8 mil via stub. Having either no via stub or a very small via stub would eliminate this unwanted 46-GHz resonance

Figure 3.11 The top view of via models, analyzed using MVTT a) Single ring 12 ground vias. b) Single ring 16 ground vias. c) Single ring 24 ground vias

There are three output parameters optimized in the MVTT using the genetic algorithm: (1) the radius of the pad, (2) the radius of the antipad, and (3) the distance between the ground via and a signal via. The MVTT generates these three parameters, taking into account both initial parameters and ranges established by a user. Tuning the impedance of the via to 50 Ohm at the optimization stage. The optimization results also depend significantly on the initial dielectric parameters. The results for the optimized parameters are giving in Table 3.1. They are depend on the chosen DK and DF values of the PCB test board dielectric.

Figure 3.12 Calculated S-parameters using the MVTT (snapshot) The model with a 10.8 mil via stub is shown in red. Via without the stub is in shown in blue a) Magnitude  $S_{11}$ . b) Magnitude  $S_{21}$

| 1        |    |     | / 1 |     |

|----------|----|-----|-----|-----|

| Df       | 0. | 0.0 | 0.0 | 0.0 |

| Dk       | 3. | 3.4 | 3.2 | 3   |

| Via pad, | 18 | 18. | 20  | 19. |

| Via      | 27 | 26. | 25  | 25  |

| Distance | 58 | 56  | 54  | 40  |

Table 3.1 Overview of the optimization for via geometry parameters for different DK, DF

The optimized dimensions of both the via pad and anti-pad, were obtained for the DK=3.2. The size of the via must match the size of the SMA connector pin for getting an acceptable signal transition between the connector and the via. Both types of SMA connectors (the 3.5mm and 2.4mm) have a connector pin diameter of 20 mil.

During the second stage of the via transition design, the via structure (which has been optimized using the MVTT software) was modeled using the full-wave CST Microwave Studio tools (further referred as CST). According to the results of the MVTT via geometry optimization, 16 stitching ground via, each located at 54 mil away from the center of the signal via, were needed. The two closest to the trace ground stitching vias were too close to the single-ended stripline. They need to be moved away from the trace. The via pad was 20 mil in diameter, while the via anti-pad diameter was 25 mil. The via stub should be either shorter, or even completely eliminated from the via structure. The DK was set at 3.2, and the loss tangent was DF=0.01. Both the CST model overview and the corresponding via geometry are presented in Figure 3.13.

The model in the CST was designed according both the calculations and optimization obtained using the MVTT. The simulated data given in Figure 3.14, however, is unacceptable.

The modeled insertion loss was comparatively high (>-20 dB) at frequencies above approximately 15 GHz. The return loss was greater than the insertion loss over the frequency range approximately from 26 to 32 GHz. These factors may cause the TRL calibration to fail. That affects measurement accuracy.

Figure 3.13 Overview of the first via geometry CST model a) Top view. b) Prospective view. c) Front view. d) Side view

During the third stage of the via design, the optimized and modeled via dimensions must be tuned to decrease the return loss and possibly remove the natural resonance of the cavity mode or move it closer to the target 50 GHz

Figure 3.14 Results of modeling of improved via model in CST. Blue curve indicated |S21|, red curve corresponds to |S11|

Several special techniques are available to improve the via design. Several of these techniques have been implemented at the initial stage of modeling in CST. Reducing the via stub from 10.8 mil to 2 mil allowed for avoiding an unwanted resonance close to 50 GHz. A tear-drop structure could be applied to eliminate sharp angles/edges at the via-trace transition. However, after modeling the tear-drop geometry in the CST, little improvement was observed. An unwanted cavity coupling to the other structures, such as via, traces, via wall on the PCB could be suppressed by adding an additional, second, stitching ground via ring. The dual ring ground via structure provides the better isolation for coupling. The closest outer ring of the ground vias may be located at 70 mil away from the center of the signal via. On the one hand, having the second ring closer than 70 mil to the center of signal via, cannot satisfy manufacturing requirements.

As compared to the initial CST model, illustrated in Figure 3.13, only two changes in the next CST model were made. These changes included both adding a second ring of ground vias 70 mil away from the center of the signal via and using a wider antipad. The clearance between the signal pad and the first ring of ground vias was increased to prevent having short between inner pin of the 2.4 mm SMA connectors and the ground plane of the PCB, while running calibration and measurements. In the latest new CST model, the diameter of the antipad is 34 mil. Figure 3.15 shows the via design and gives information about its dimensions.

Figure 3.15 Overview of the second CST design via model a) Top view. b) Prospective view. c) Front view. d) Side view

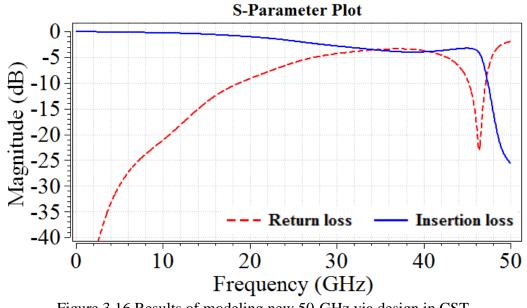

Even with small changes in the via model design, the simulated CST results (illustrated in Figure 3.16) were better than the results from the previous design. The magnitude of return loss of the second via model did not exceed the magnitude of the insertion loss over the entire frequency range until above 46 GHz, where the natural resonance of the cavity mode occurs. The chance of TRL calibration failure during measurements with this latter via-trace transition design was reduced when compared to the initial design. The phase of the insertion loss (shown in Figure 3.17) remained both linear and stable up to 46 GHz, also indicating a better quality of the second model.

After analyzing the simulation results, shown in Figures 3.16 and 3.17, the decision to use the latest version of the via model as a via design for new test vehicle has been made. The CST model shows that there is an unwanted resonance at frequency of about 48 GHz. This resonance is clearly seen in Figure (3.16) on the insertion loss curve. It can limit the frequency range of the new via design.

The possible explanation of the resonance observed in Figure (3.16) is the higherorder mode (TE<sub>11</sub>) in the coaxial structure. The internal radius of the structure corresponds to the radius of the via radius of the via itself (a = 10 mils). The outer radius corresponds to the radius of the inner ground via ring (b = 27 mils). According to [4, pp 144-145], the cut-off frequency is calculated as

$$f_c = \frac{c \cdot k_c}{2\pi \sqrt{\varepsilon_r}} \tag{3.1}$$

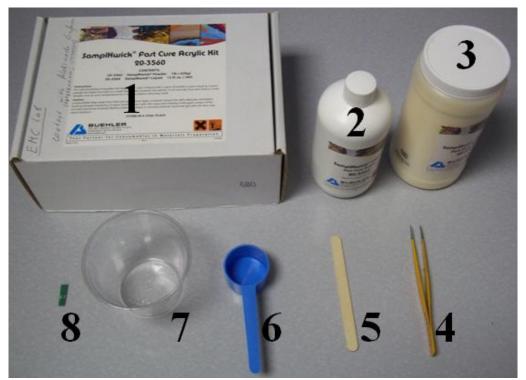

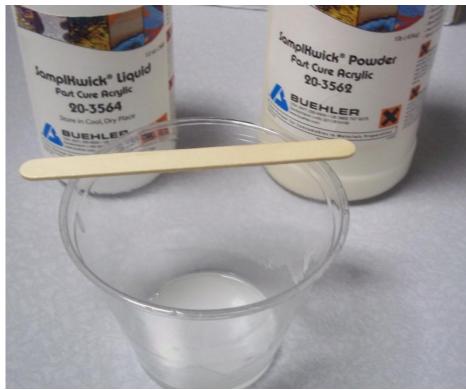

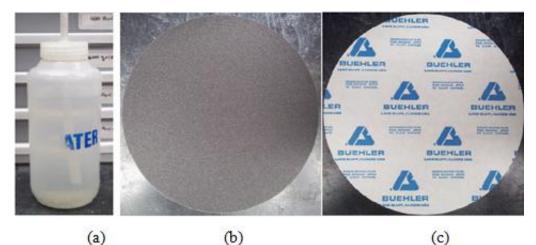

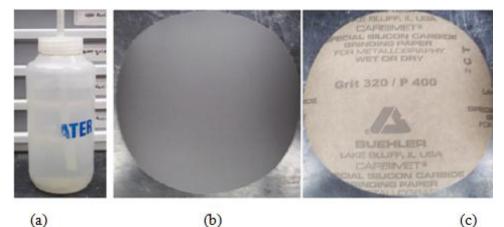

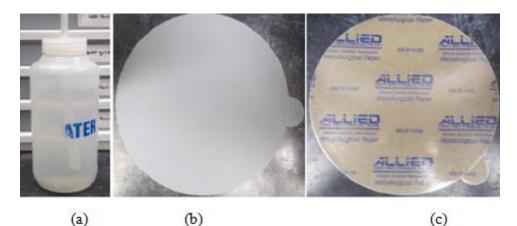

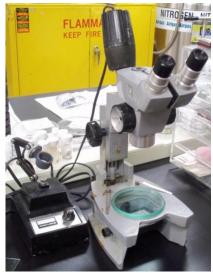

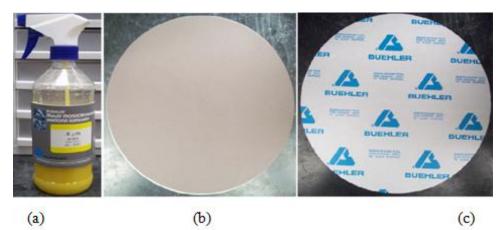

where  $k_c$  is the cut-off wave number, which is approximately found according