# Scholars' Mine

**Doctoral Dissertations**

Student Theses and Dissertations

Fall 2019

# Characterization and modeling of ESD events and near-field scanning calibration structures

Shubhankar Kashinath Marathe

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Electromagnetics and Photonics Commons Department: Electrical and Computer Engineering

# **Recommended Citation**

Marathe, Shubhankar Kashinath, "Characterization and modeling of ESD events and near-field scanning calibration structures" (2019). *Doctoral Dissertations*. 2840. https://scholarsmine.mst.edu/doctoral\_dissertations/2840

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# CHARACTERIZATION AND MODELING OF ESD EVENTS AND NEAR-FIELD

# SCANNING CALIBRATION STRUCTURES

by

# SHUBHANKAR KASHINATH MARATHE

# A DISSERTATION

Presented to the Faculty of the Graduate School of the

# MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

# DOCTOR OF PHILOSOPHY

in

# ELECTRICAL ENGINEERING

2019

Approved by:

Dr. Daryl Beetner, Advisor Dr. Jun Fan Dr. Chulsoon Hwang Dr. Victor Khilkevich Dr. Daniel Stutts

© 2019

# SHUBHANKAR KASHINATH MARATHE

All Rights Reserved

# PUBLICATION DISSERTATION OPTION

This dissertation consists of the following three articles, formatted in the style used by the Missouri University of Science and Technology:

Paper I: Pages 3-29; Software-Assisted Detection Methods for Secondary ESD Discharge During IEC 61000-4-2 Testing, has been accepted in IEEE Transactions on Electromagnetic Compatibility.

Paper II: Pages 30-57; Measurement-based Characterization and Full-wave Modeling of ESD to Display Touchscreen Sensors, will be submitted to IEEE Transactions on Electromagnetic Compatibility.

Paper III: Pages 58-81; Effect of Inhomogeneous Medium on Fields Above GCPW PCB for Near-Field Scanning Application, has been accepted in IEEE Transactions on Electromagnetic Compatibility.

#### ABSTRACT

This research is divided into three papers that cover, two major topics. The first topic, system-level electrostatic discharge (ESD), is discussed over the course of two papers. The second topic, a calibration structure for near-field scanning probe calibration application, is discussed in the last paper. In the first paper, software-assisted detection methods are proposed for secondary ESD discharges. The measured waveforms are analyzed with respect to waveform parameters, such as the vertical threshold of the rising edge, the derivative of the current waveform, and total charge delivered. These parameters enable automatic detection of secondary ESD while monitoring the discharge waveform at the ESD generator tip. In the second paper, the worst-case risk caused due to sparkless discharges to electronic touchscreens is investigated. The statistical behavior of the induced currents is determined for different parameters such as a change in glass thickness, indium tin oxide layer equivalent resistance, sensor spacing to the ground plane, ESD generator air discharge polarity and test voltage. In addition, a full-wave simulation model is developed to reproduce the displacement current flowing through the glass into the display's inner electronic structures. In the third paper, a method is proposed to calibrate a probe by placing it into a known field and referencing its output voltage to the known field. The near-field is measured by using E- and H-field electromagnetic interference probes. A calibration structure is built from a grounded coplanar waveguide to determine the probe factor for near-field scanning applications. The effect of non-TEM modes is easily underestimated such that non-TEM fields prevent the user from determining the unwanted field suppression of probes at higher frequencies.

## ACKNOWLEDGMENTS

I would like to express my sincere gratitude to my M.S. degree advisor, Dr. David Pommerenke, for guiding me throughout the course of both my M.S. and Ph.D. degree program. I would like to thank my Ph.D. degree advisor, Dr. Daryl Beetner, for his continuous guidance in my research work and enhancing my learning experience through numerous discussions. They guided me in developing both technical and non-technical skill sets, which helped me grow as an individual.

I would like to thank Dr. Jun Fan, Dr. Chulsoon Hwang, Dr. Victor Khilkevich, and Dr. Daniel Stutts for helping me with many useful discussions related to my research work. I would also like to thank all the former and current members of the EMC laboratory for their teamwork and help in my research and coursework. I am proud that I was a member of such an exceptional lab in the EMC area.

Lastly, I am deeply grateful to my parents and my sister for their constant support and encouragement towards achieving this goal.

# **TABLE OF CONTENTS**

| P                                                                                                  | age   |

|----------------------------------------------------------------------------------------------------|-------|

| PUBLICATION DISSERTATION OPTION                                                                    | . iii |

| ABSTRACT                                                                                           | . iv  |

| ACKNOWLEDGMENTS                                                                                    | V     |

| LIST OF ILLUSTRATIONS                                                                              | . ix  |

| LIST OF TABLES                                                                                     | xiii  |

| SECTION                                                                                            |       |

| 1. INTRODUCTION                                                                                    | 1     |

| 1.1. SYSTEM-LEVEL ESD                                                                              | 1     |

| 1.2. CALIBRATION STRUCTURE FOR NEAR-FIELD SCANNING                                                 | 2     |

| PAPER                                                                                              |       |

| I. SOFTWARE-ASSISTED DETECTION METHODS FOR SECONDARY ESD<br>DISCHARGE DURING IEC 61000-4-2 TESTING | 3     |

| ABSTRACT                                                                                           | 3     |

| 1. INTRODUCTION                                                                                    | 4     |

| 1.1. CONTROLLED SETUP                                                                              | 6     |

| 1.2. SETUP FOR SECONDARY DISCHARGE INSIDE OF A TWO-WIRE<br>POWER SUPPLY                            | 7     |

| 2. SECONDARY DISCHARGE WAVEFORMS AND EVENT DETECTION                                               | 9     |

| 2.1. MEASUREMENT RESULTS FOR THE CONTROLLED SETUP                                                  | . 12  |

| 2.2. MEASUREMENT RESULTS FOR SECONDARY DISCHARGE<br>INSIDE OF A TWO-WIRE POWER SUPPLY              | . 13  |

| 3. SOFTWARE-ASSISTED DETECTION                                                                     | . 15  |

| 3.1. CHARGE-BASED DETECTION                                                                            | 16 |

|--------------------------------------------------------------------------------------------------------|----|

| 3.1.1. Total Charge in the Secondary and Primary ESD Event                                             | 20 |

| 3.1.2. Events due to Residual Charge in the ESD Gun                                                    | 22 |

| 3.2. DISCHARGE CURRENT WAVEFORM-BASED DETECTION                                                        | 23 |

| 4. DISCUSSION                                                                                          | 25 |

| 5. CONCLUSION                                                                                          | 27 |

| REFERENCES                                                                                             | 28 |

| II. MEASUREMENT-BASED CHARACTERIZATION AND FULL-WAVE<br>MODELING OF ESD TO DISPLAY TOUCHSCREEN SENSORS | 30 |

| ABSTRACT                                                                                               | 30 |

| 1. INTRODUCTION                                                                                        | 31 |

| 2. MEASUREMENT SETUP                                                                                   | 33 |

| 2.1. EVALUATION PRINTED CIRCUIT BOARD (PCB) GEOMETRY                                                   | 33 |

| 2.2. AUTOMATED HMM DISCHARGE SETUP                                                                     | 34 |

| 2.2.1. ESD Generator Approach Speed Control                                                            | 34 |

| 2.2.2. ESD Generator Voltage and Polarity                                                              | 35 |

| 2.2.3. Shielded Enclosure                                                                              | 35 |

| 2.2.4. Vacuum Pump                                                                                     | 35 |

| 2.2.5. Ionizer                                                                                         | 35 |

| 2.3. ULTRA-SEGMENTATION MODE OSCILLOSCOPE ACQUISITION                                                  | 36 |

| 3. MEASUREMENT RESULTS                                                                                 | 38 |

| 4. FULL-WAVE SIMULATION MODELING                                                                       | 45 |

| 5. DISCUSSION                                                                                          | 52 |

| 6. CONCLUSION                                                                                          | 54 |

| REFERENCES                                                                                                               | 55 |

|--------------------------------------------------------------------------------------------------------------------------|----|

| III. EFFECT OF INHOMOGENEOUS MEDIUM ON FIELDS ABOVE GCPW<br>PCB FOR NEAR-FIELD SCANNING PROBE CALIBRATION<br>APPLICATION | 50 |

| APPLICATION                                                                                                              | 38 |

| ABSTRACT                                                                                                                 | 58 |

| 1. INTRODUCTION                                                                                                          | 59 |

| 2. GCPW SIMULATION MODEL                                                                                                 | 63 |

| 3. SIMULATION RESULTS                                                                                                    | 66 |

| 4. TESTING THE REJECTION RATIO OF A NEAR-FIELD PROBE                                                                     | 72 |

| 4.1. COMPARISON BETWEEN THE TWO GCPW GENERATED<br>FIELDS AT A FIXED HEIGHT AND FREQUENCY                                 | 74 |

| 4.2. COMPARISON BETWEEN THE TWO GCPW GENERATED<br>FIELDS AT A FIXED FREQUENCY AND DIFFERENT HEIGHTS                      | 76 |

| 5. DISCUSSION AND CONCLUSION                                                                                             | 78 |

| REFERENCES                                                                                                               | 80 |

| SECTION                                                                                                                  |    |

| 2. SUMMARY AND CONCLUSIONS                                                                                               | 82 |

| BIBLIOGRAPHY                                                                                                             | 84 |

| VITA                                                                                                                     | 89 |

# LIST OF ILLUSTRATIONS

| Pag | ge |

|-----|----|

| PAPER I   |                                                                                                                                                                                                                                                                                                                                                               |     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 1. | Block diagram of secondary ESD discharge measurement setup.                                                                                                                                                                                                                                                                                                   | 7   |

| -         | (a) Non grounded 10 cm $\times$ 10 cm plane. (b) 1.9 $\Omega$ current target mounted on the shielded enclosure, located underneath the plate.                                                                                                                                                                                                                 | . 8 |

| •         | Measurement setup for secondary ESD discharge inside of a two-wire power supply                                                                                                                                                                                                                                                                               | . 9 |

|           | Graphical illustration of a typical ESD event followed by a secondary discharge event                                                                                                                                                                                                                                                                         | 10  |

| Figure 5. | Waveforms acquired using F-65 current clamp                                                                                                                                                                                                                                                                                                                   | 12  |

| Figure 6. | Measured waveforms on the controlled setup.                                                                                                                                                                                                                                                                                                                   | 13  |

|           | Measured waveforms on the two-wire power supply setup using the F-65 current clamp placed at the tip of the ESD gun measuring the discharge current, the wire loop probe positioned near the two-wire power supply to monitor any disturbances inside of the two-wire power supply and the high impedance voltage probe to monitor the floating metal voltage | 14  |

|           | Flowchart of the suggested algorithm for secondary ESD detection based<br>on the secondary ESD waveforms acquired using a current clamp                                                                                                                                                                                                                       | 16  |

| Figure 9. | Measured F-65 current clamp waveforms                                                                                                                                                                                                                                                                                                                         | 19  |

| Figure 10 | $Q_{\text{primary}} = Q_{\text{secondary}} = \text{approximately 130 nC}.$                                                                                                                                                                                                                                                                                    | 21  |

| Figure 11 | . (a) First triggered event on the oscilloscope. (b) Reignition discharge event is 5.8 ms after the first triggered event with an ESD gun voltage setting of 10 kV                                                                                                                                                                                            | 23  |

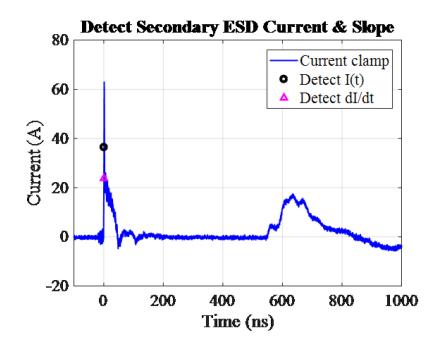

| Figure 12 | . Secondary ESD detection using the rising edge and slope detection algorithm.                                                                                                                                                                                                                                                                                | 24  |

| Figure 13 | . Detection based on the rising edge and the slope of the measured current<br>for the two-wire power supply setup                                                                                                                                                                                                                                             | 26  |

# PAPER II

| Figure 1. Typical touchscreen sensor geometry.                                                                                                                                                                               | . 32 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

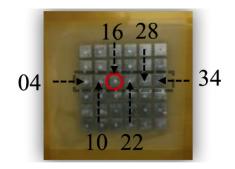

| Figure 2. Designed evaluation PCB touchscreen sensor patch display geometry                                                                                                                                                  | . 34 |

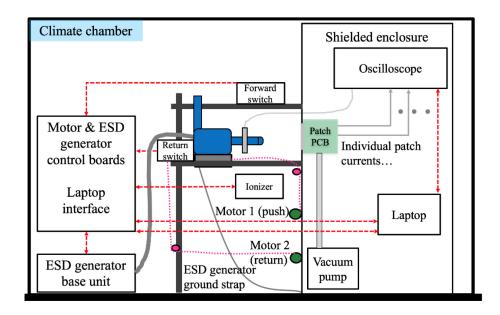

| Figure 3. Automated measurement setup positioned in a climate chamber                                                                                                                                                        | . 36 |

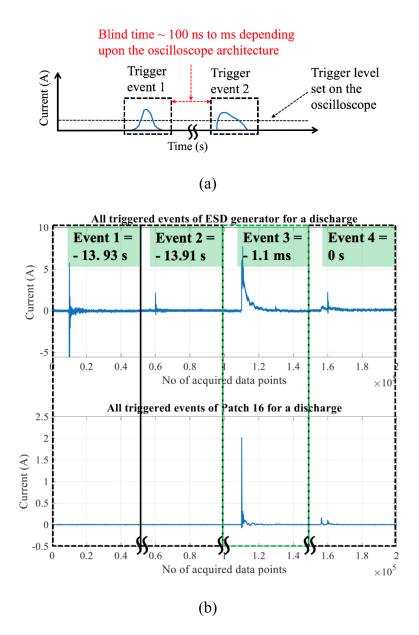

| Figure 4. Ultra-segmentation or fast-retrigger mode on the oscilloscope                                                                                                                                                      | . 37 |

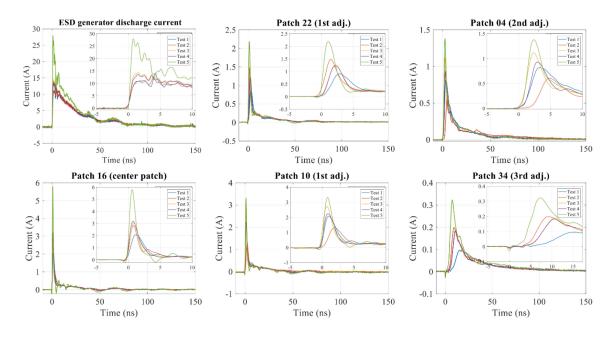

| Figure 5. Measured data for 0.6 mm (thin glass, $C2a = 650$ fF), 3rd layer PCB ground ( $C2b = 2.9$ pF), 100 $\Omega$ ITO series resistance (Rtrace), 0.3 m/s approach speed at +15 kV ESD generator air discharge setting   | . 40 |

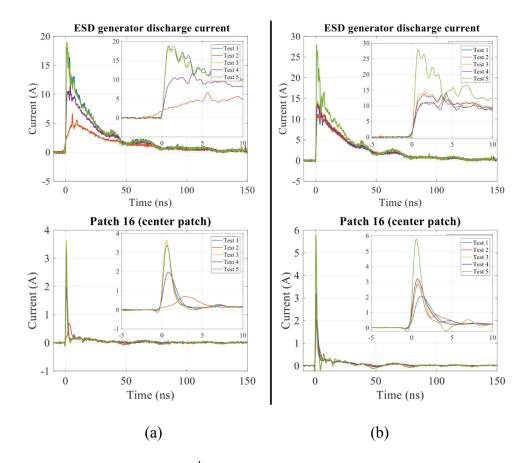

| Figure 6. DUT geometry with 3 <sup>rd</sup> layer PCB ground ( $C_{2b} = 2.9 \text{ pF}$ ), 100 $\Omega$ ITO series resistance ( $R_{\text{trace}}$ ), 0.3 m/s approach speed at +15 kV ESD generator air discharge setting. | . 42 |

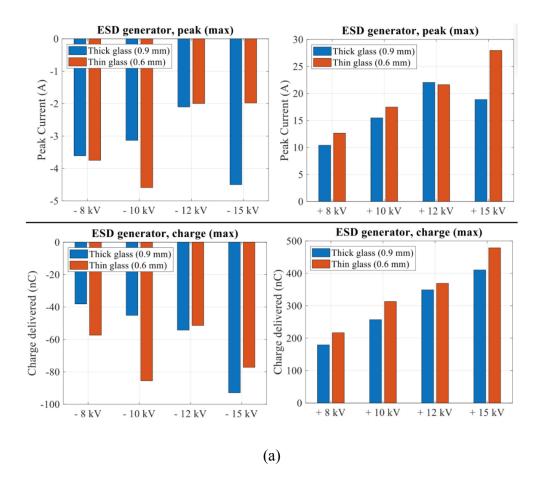

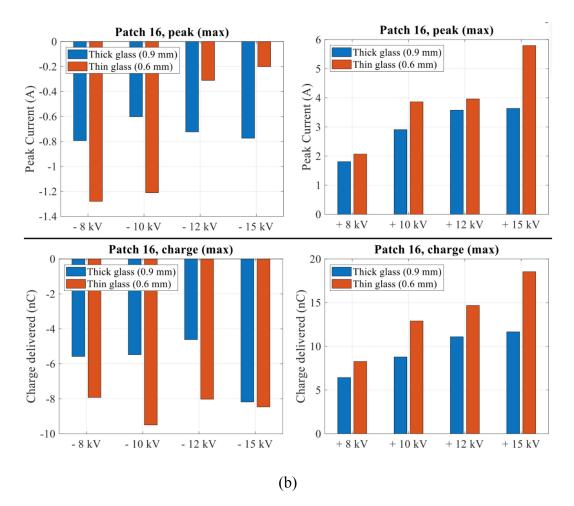

| Figure 7. Measured data for 0.6 mm (thin glass) & 0.9 mm (thick glass), 3rd layer<br>PCB ground, 100 Ω ITO series resistance, 0.3 m/s approach speed at<br>+15 kV ESD generator air discharge setting.                       | . 44 |

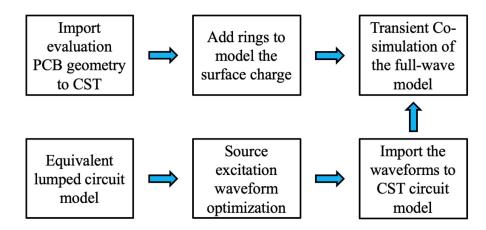

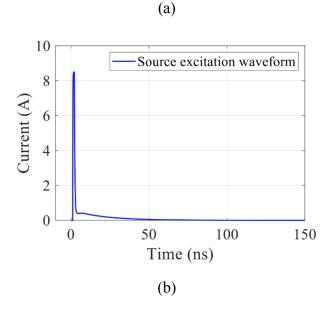

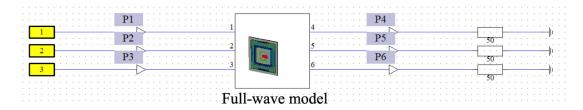

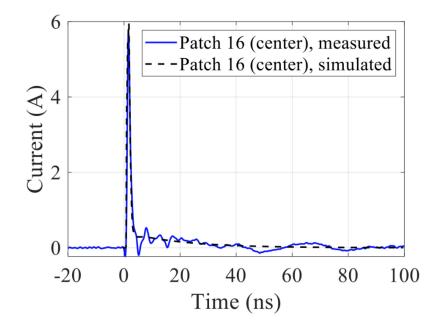

| Figure 8. Simulation workflow.                                                                                                                                                                                               | . 47 |

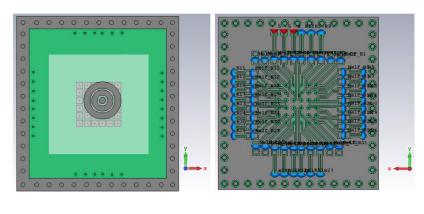

| Figure 9. Simulation model illustrating the concentric ring structures                                                                                                                                                       | . 49 |

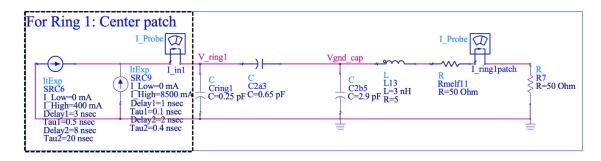

| Figure 10. DUT equivalent circuit geometry simulated using the advanced designed system (ADS) software.                                                                                                                      | . 50 |

| Figure 11. Transient co-simulation block diagram.                                                                                                                                                                            | . 51 |

| Figure 12. Comparison of the measured and simulated worst-case ESD induced waveform.                                                                                                                                         | . 51 |

| PAPER III                                                                                                                                                                                                                    |      |

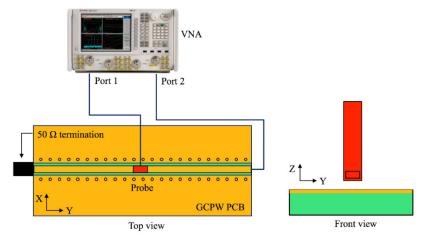

| Figure 1. Measurement set-up for probe factor calculations using a GCPW PCB                                                                                                                                                  | . 61 |

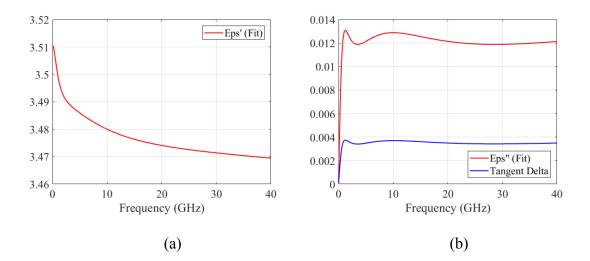

| Figure 2. Frequency dependence of the RO4350 dielectric material properties used in the simulation model.                                                                                                                    | . 64 |

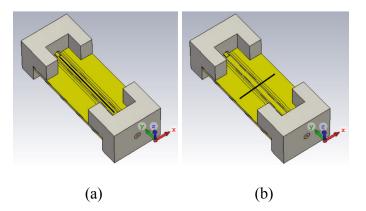

| Figure 3. Simulation model of the RO4350 dielectric-based GPCW PCB with a connector model.                                                                                                                                   | . 66 |

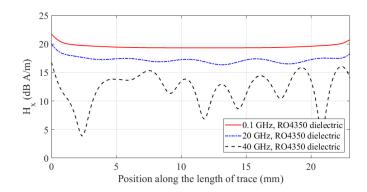

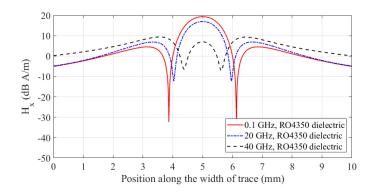

| Figure 4. Desired $H_x$ component over the RO4350 GCPW trace along the length (y-<br>direction, parallel to the trace) of the PCB at 0.1, 20, and 40 GHz.                                                                    | . 68 |

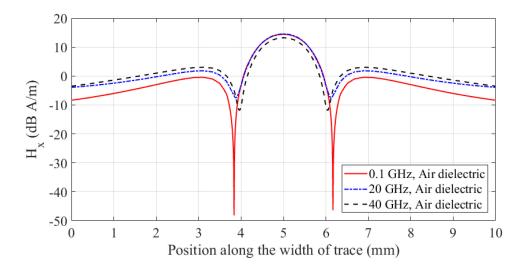

| •  | esired $H_x$ component over the RO4350 GCPW trace along the width (x-<br>irection) of the PCB at 0.1, 20, and 40 GHz.                                                                                              | 68 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

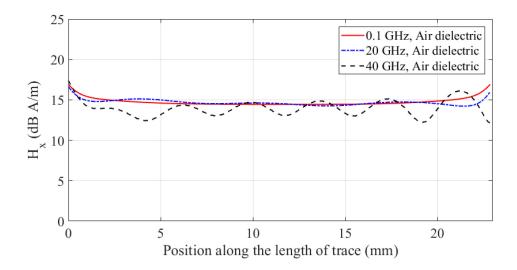

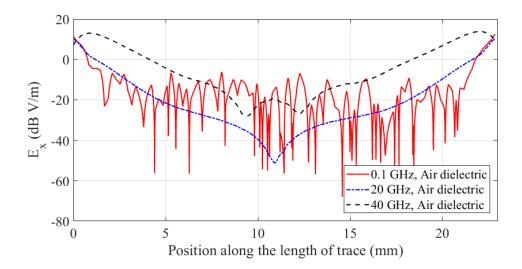

|    | esired $H_x$ component over the air GCPW trace along the length (y-<br>irection) of the PCB at 0.1, 20, and 40 GHz                                                                                                 | 69 |

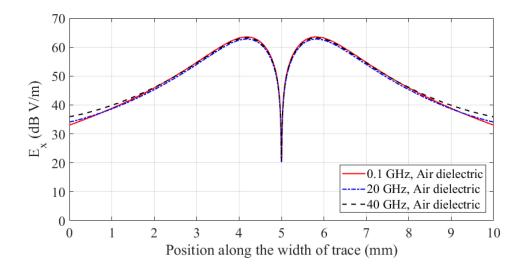

| •  | esired $H_x$ component over the air GCPW trace along the width (x-<br>irection) of the PCB at 0.1, 20, and 40 GHz.                                                                                                 | 69 |

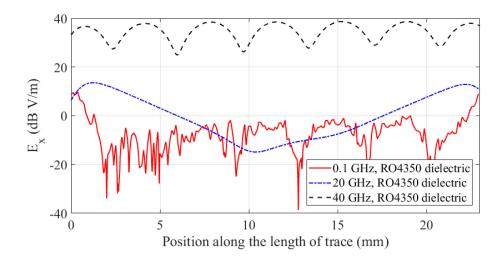

| di | esired $E_x$ component over the GCPW trace along the length (y-<br>irection) of the PCB at 0.1, 20, and 40 GHz but exactly in the middle<br>where the component has a null.                                        | 70 |

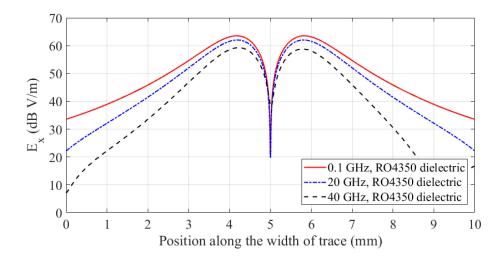

| -  | esired $E_x$ component over the GCPW trace along the width (x-direction) f the PCB at 0.1, 20, and 40 GHz                                                                                                          | 70 |

|    | $E_x$ component over the GCPW trace along the length (y-direction) of the PCB at 0.1, 20, and 40 GHz.                                                                                                              | 71 |

| •  | $E_x$ component over the GCPW trace along the width (x-direction) of the PCB at 0.1, 20, and 40 GHz.                                                                                                               | 71 |

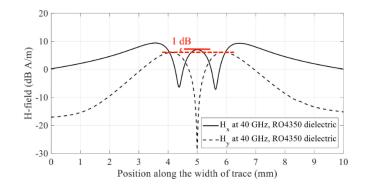

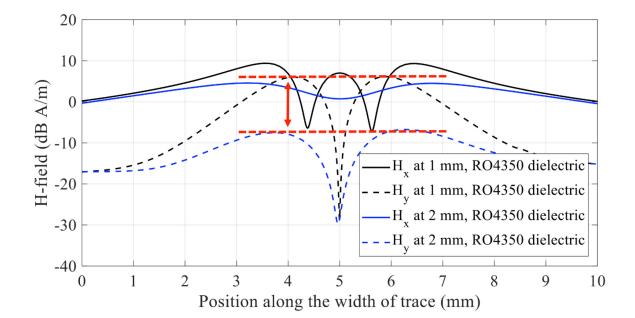

| 1  | Side scan comparison of the desired $H_x$ component (solid line) and the non-TEM $H_y$ component (dashed line) over the RO4350 GCPW trace along the width (x-direction) of the PCB at $z = 1 \text{ mm}$ at 40 GHz | 73 |

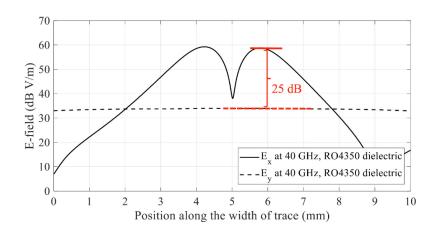

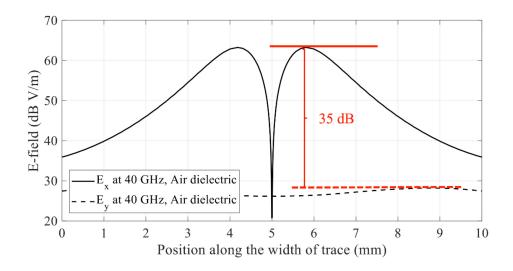

| (  | Side scan comparison of desired $E_x$ component (solid line) and the $E_y$ component (dashed line) over the RO4350 GCPW trace along the width (x-direction) of the PCB at $z = 1 \text{ mm}$ at 40 GHz.            | 74 |

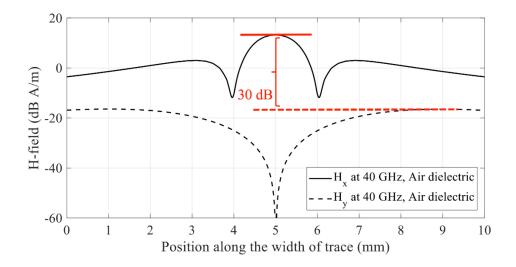

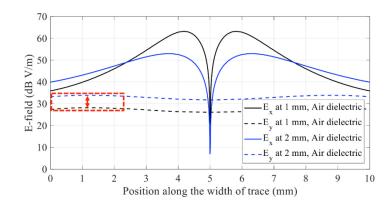

| 1  | Side scan comparison of the desired $H_x$ component (solid line) and the non-TEM $H_y$ component (dashed line) over the air GCPW trace along the width (x-direction) of the PCB at $z = 1 \text{ mm}$ at 40 GHz    | 75 |

| (  | Side scan comparison of desired $E_x$ component (solid line) and the $E_y$ component (dashed line) over the air GCPW trace along the width (x-direction) of the PCB at $z = 1 \text{ mm}$ at 40 GHz                | 75 |

|    | Side scan comparison of the desired $H_x$ component (solid line) and the $H_y$ component (dashed line) over the RO4350 GCPW trace along the width (x-direction) of the PCB at $z = 1$ and 2 mm at 40 GHz           | 76 |

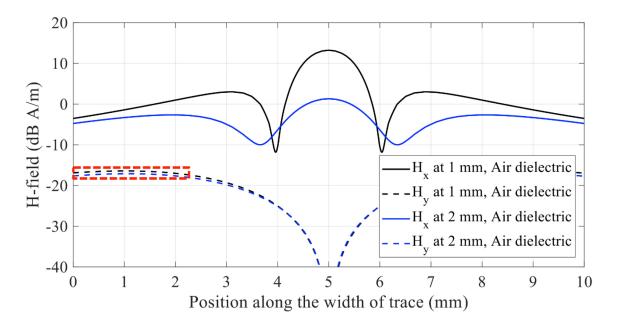

| -  | Side scan comparison of desired $H_x$ component (solid line) and the $H_y$ component (dashed line) over the air GCPW trace along the width (x-direction) of the PCB at $z = 1$ and 2 mm at 40 GHz                  | 77 |

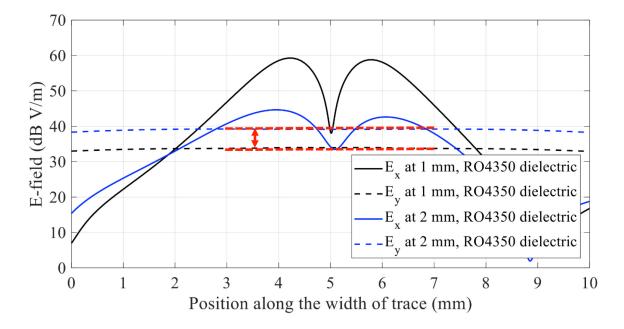

| Figure 18. Side scan comparison of desired $E_x$ component (solid line) and the |    |

|---------------------------------------------------------------------------------|----|

| undesired $E_y$ component (dashed line) over the RO4350 GCPW trace              |    |

| along the width (x-direction) of the PCB at $z = 1$ and 2 mm at 40 GHz          | 77 |

| Figure 19. Side scan comparison of desired $E_x$ component (solid line) and the |    |

|---------------------------------------------------------------------------------|----|

| undesired $E_y$ component (dashed line) over the air GCPW trace along           |    |

| the width (x-direction) of the PCB at $z = 1$ and 2 mm at 40 GHz                | 78 |

# LIST OF TABLES

|                                                                                                                         | Page |

|-------------------------------------------------------------------------------------------------------------------------|------|

| PAPER I                                                                                                                 |      |

| Table 1. Learning sequence and charge based analysis.                                                                   | 18   |

| PAPER II                                                                                                                |      |

| Table 1. Design parameters of the display geometry                                                                      | 39   |

| Table 2. Waveform parameters for the worst-case touchscreen sensor patch at   +15 kV.                                   | 51   |

| PAPER III                                                                                                               |      |

| Table 1. Design parameters of the two GCPW models investigated using CST MWS simulation.                                | 65   |

| Table 2. Field rejection ratio for various frequencies for RO4350 and air-dielectric      GCPW at 1 mm above the trace. | 79   |

# **1. INTRODUCTION**

#### **1.1. SYSTEM-LEVEL ESD**

In Paper I, software-assisted detection methods are proposed for secondary ESD discharges. When an ESD event reaches a nongrounded metallic part within a product, the voltage of this metallic part with respect to ground will increase. If the isolation to the ground is insufficient, a secondary ESD event can occur. Secondary ESD events are especially harmful to electronic products for multiple reasons. First, the peak discharge current within the secondary spark gap can be more than five times larger than the current of the primary ESD event from the ESD generator. Second, the rise time of the secondary ESD can be much shorter than the primary discharge—a consequence of discharging a highly overvoltaged gap. Third, the secondary ESD occurs within the product and can couple more strongly into the sensitive electronics. This can lead to soft and hard failures. As secondary ESD often leads to system upset or damage and to poorly reproducible results, it is important to detect the occurrence of secondary ESD. Secondary ESD can be detected in IEC 61000-4-2 setups by monitoring the currents, charge transfer, and sudden current increases due to the secondary ESD. An algorithm has been developed that automatically detects secondary ESD events.

Paper II investigates ESD sparkless surface discharges to displays. An evaluation PCB is designed to analyze the influence of touch screen sensor-geometry parameters such as display glass thickness, sensor-to-system-ground capacitance, and the ITO layer equivalent resistance. The setup measures the air discharge-induced displacement current into the touch sensors. As the ESD generator approaches the glass surface, a sparkless surface corona discharge occurs, which rapidly changes the surface potential. The change in potential causes the displacement current to flow through the glass into the touch sensors. Statistical data is needed to understand the variation in peak level and the total charge delivered by the induced currents. Furthermore, a full-wave simulation model is developed to predict the worst-case induced currents flowing into the touch screen sensors.

# **1.2. CALIBRATION STRUCTURE FOR NEAR-FIELD SCANNING**

Near-field scanning is used to visualize the near-field sources present inside an electronic device. The near-fields are measured using near-field E and H probes. The near-field data obtained using the probes are valuable; for example, identifying radio frequency interference in mobile devices. One of the applications of the near-field scanning technique is to generate models of ICs or emission sources on PCBs by obtaining the near-field data over the DUT. The emission frequency spectrum may range from a few KHz up to 40 GHz and higher. The goal of this work is to identify a single-probe calibration method that can work for large frequency bandwidth. From the available choices, the GCPW transmission line is selected as it supports wide frequency bandwidth and because of its convenience of measuring the field strength over small heights over the trace structure. At first glance, one may believe that the field structure over a GCPW or microstrip is not a function of frequency, as the structure supports a quasi-TEM wave. This paper discusses the effect of the inhomogeneous medium in GCPW PCB.

# PAPER

# I. SOFTWARE-ASSISTED DETECTION METHODS FOR SECONDARY ESD DISCHARGE DURING IEC 61000-4-2 TESTING

S. Marathe

Department of Electrical Engineering Missouri University of Science and Technology Rolla, Missouri 65409–0050 Tel: 573–202–1260

Email: skmcr4@mst.edu

# ABSTRACT

When an electrostatic discharge (ESD) event reaches a nongrounded metallic part within a product, the voltage of this metal with respect to ground will increase. If the isolation to the ground is insufficient, a secondary ESD event can occur. As secondary ESD often leads to system upset or damage, and to poorly reproducible results, it is important to detect the occurrence of secondary ESD. If the discharge current is monitored using an oscilloscope, the test equipment may miss the secondary discharge waveform. This is because the time delay between the primary and secondary discharge events can vary between nanoseconds to milliseconds. Present oscilloscopes do not offer functionality to autodetect a secondary discharge event. The goal of this study is to analyze different types of secondary discharge events acquired with various measurement setups and identify waveform parameters for software-assisted detection methods. A learning sequence is proposed for identifying secondary ESD events starting from low ESD gun test voltages. The data are analyzed with respect to the waveform parameters such as the vertical threshold of the rising edge, the dI/dt of the current waveform, and total charge delivered, which enable automatic detection of secondary ESD while monitoring the discharge waveform at the ESD gun tip.

**Keywords:** Current clamp, detection algorithm, electrostatic discharge (ESD), oscilloscope, secondary discharge, sequence mode acquisition.

## **1. INTRODUCTION**

Secondary electrostatic discharge (ESD) events are especially harmful to electronic products for multiple reasons. First, the peak discharge current within the secondary spark gap can be more than five times larger than the current of the primary ESD event from the ESD gun [1]–[4]. Second, the rise time of the secondary ESD can be much shorter than the primary discharge—a consequence of discharging a highly overvoltaged gap. Third, the secondary ESD occurs within the product and can couple more strongly into the sensitive electronics. This can lead to soft and hard failures. From a testing point of view, another difficulty arises from the repeatability of secondary ESD. The secondary discharge varies much more than the primary event due to the variability of the statistical time lag [1]. Typically, during system-level ESD testing of compact electronics, the root cause of the observed failures may not be clear. For instance, cell phones are known to have ESD-induced risks to various system components and peripherals exposed to the end user [5]–

[8]. In the case of compact electronics, secondary ESD events are likely to cause failures as the spark gap distances inside the electronic products are small—ranging from micrometers to millimeters. Knowing if secondary ESD has occurred helps to understand test results and their repeatability, and assists root-cause analysis of observed failures. Detecting secondary ESD can be achieved by measuring the discharge currents and voltages or transient fields, then processing them with software algorithms to determine whether secondary ESD has occurred.

Investigations have been performed to develop a methodology to model the secondary discharge inside of a portable electronic product [3], [4], [19]. ESD guns are known to generate electromagnetic noise pulses during ESD testing. The switching of relays inside of the ESD gun before and following the discharge test leads to the prepulse and postpulse events [10], [11]. Additional pulses can be created during the ESD test due to reignition of the gap between the air discharge tip and the device under test (DUT). Here, the arc of the discharge may quench before most of the charge is depleted. As the ESD gun approaches toward the DUT test point, the gap is reduced and this may reignite the ESD gun. For contact mode discharges, a similar effect may be observed in which the spark in the relay may quench and reignite, or the relay may bounce. It is important to note that these occurrences should not be conflated with secondary ESD events, since these secondary sparks are instead generated by the ESD gun.

The various DUT configurations are placed on a horizontal coupling plane (HCP) during ESD testing and can include a grounded device, a device connected by a two-wire power supply, a battery-powered device, or a complex system with multiple cable connections. The cases where the DUT is not grounded, for example, a battery-powered device, which has floating metal and a DUT connected to a two-wire power supply, are investigated. Measured current waveforms during secondary discharge events for the floating metal and the two-wire power supply setups [12] are used for identifying waveform parameters for software-assisted detection. First, the waveforms are measured for a controlled setup, which reproduces a DUT having a nongrounded decorative metal part. The second case consists of a DUT, which is connected to a two-wire power supply, in which the secondary ESD occurs inside of the two-wire power supply. The waveforms are acquired using an oscilloscope, a high-impedance voltage probe, and an F-65 current clamp.

A software-assisted methodology is proposed for secondary ESD event detection during IEC 61000-4-2 testing [13], which enables the distinction between the primary and secondary ESD events. The software tool implementation is based on a learning sequence during an ESD test session and requires an ESD gun voltage selection, DUT configuration input from the operator. The time domain data are acquired and postprocessing is performed to determine whether secondary ESD has occurred. The method is applied to various test setups, and results are discussed in Section III. This proposed detection methodology can be further implemented within the oscilloscope firmware as an additional tool set to assist ESD test engineers during system-level testing.

# **1.1. CONTROLLED SETUP**

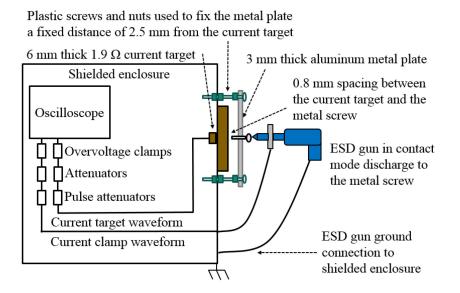

Figure 1 illustrates a measurement setup designed to understand one class of secondary discharge ESD waveforms as a controlled experiment. The setup emulates decorative metal present on electronic products which are not grounded. The controlled

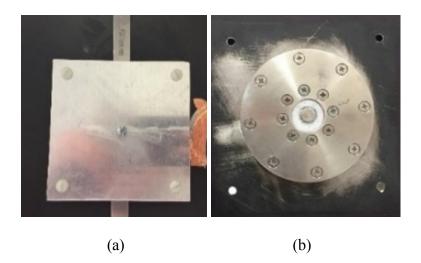

setup generates repeatable occurrences of a secondary discharge event when subjected to a primary charging ESD event. The DUT is an aluminum plate with dimensions of 10 cm height  $\times$  10 cm width  $\times$  3 mm thickness mounted above a ground plane. A screw is inserted into the plate to form a spark gap with adjustable distance. Figure 2 depicts the nongrounded floating metal and the current target.

An F-65 current clamp is used to measure the primary discharge current from the ESD gun. To protect the oscilloscope, pulse attenuators [14] and overvoltage protectors are used.

Figure 1. Block diagram of secondary ESD discharge measurement setup.

# **1.2. SETUP FOR SECONDARY DISCHARGE INSIDE OF A TWO-WIRE POWER** SUPPLY

Next, a different setup configuration is investigated in which the secondary discharge occurs inside of a two-wire power supply. This presents a challenge for discharge

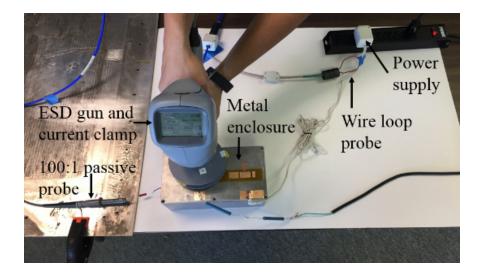

current measurement, since the event of interest occurs at a location inside of the DUT which cannot be directly probed. As a result, ESD-induced currents measured at the gun tip have degraded rise times and amplitudes, caused by the capacitive and inductive filtering between the injection point and the origin of the spark inside the system. To create a primary charging event, the ESD gun is discharged to the metal enclosure in contact mode. The metal enclosure is affixed to the low-voltage connector of the two-wire power supply. The two-wire power supply is connected directly to the power strip, while the metal enclosure is connected via a 1 G $\Omega$  high-voltage resistor to the same power strip. The F-65 current clamp is positioned at the tip of the ESD gun to monitor the discharge current during ESD testing as depicted in Figure 3.

Figure 2. (a) Non grounded 10 cm  $\times$  10 cm plane. (b) 1.9  $\Omega$  current target mounted on the shielded enclosure, located underneath the plate.

A 100:1 passive probe is used to monitor voltage on the floating metal enclosure, while a wire loop probe is positioned near the two-wire power supply to detect the occurrence of ESD events.

Figure 3. Measurement setup for secondary ESD discharge inside of a two-wire power supply.

# 2. SECONDARY DISCHARGE WAVEFORMS AND EVENT DETECTION

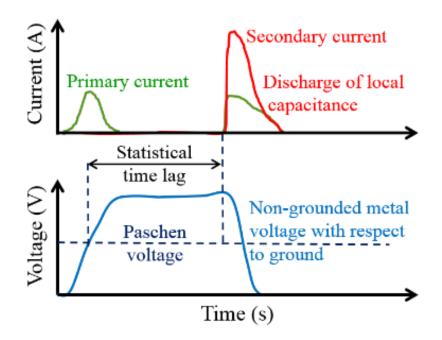

The secondary ESD event may follow a primary charging event by a variable time delay, ranging from nanoseconds to milliseconds. This variable time delay is known as the statistical time lag. Most modern oscilloscopes offer the capability to detect separate events as a sequence of individual captures. In sequential capture mode, the complete waveform consists of a number of fixed-sized segments. An oscilloscope utilizes sequenced acquisitions by selecting the desired number of segments, maximum segment length, and total available memory, which determines the actual number of events acquired. A sequential acquisition is useful for capturing many rapidly occurring ESD events, or for capturing intermittent ESD events separated by long time gaps.

To capture these waveforms in the time domain, the user sets the trigger level and enables a segmented acquisition mode in the oscilloscope [15]. However, a digital oscilloscope is temporarily blind even with the segmented acquisition mode enabled [16]. The blind time refers to the duration in between two segmented events, which cannot be acquired by the oscilloscope. The blind time or the intersegment time may range from a few hundred nanoseconds to milliseconds depending upon the type of acquisition architecture used internally within the oscilloscope. In our measurement setup, the oscilloscope intersegment time was approximately 1  $\mu$ s. One way to avoid losing signals due to the oscilloscope blind time is to select a sufficiently long time record in the range of few hundred milliseconds to several seconds for the oscilloscope time base. Increasing the time capture window size of the oscilloscope allows for the capture of secondary ESD events, but also results in reduced sampling rate of the acquired waveform. The concept of capturing both the primary and secondary discharge events is illustrated in Figure 4.

Figure 4. Graphical illustration of a typical ESD event followed by a secondary discharge event. The decrease in the metal plate voltage is the indication of the occurrence of a secondary discharge event.

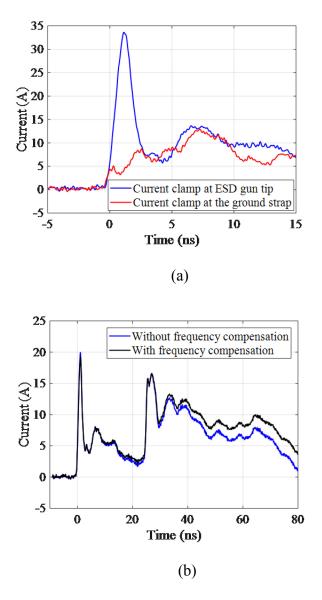

Locations for monitoring discharge using an F-65 current clamp can include the tip of the ESD gun, the ground cable of the ESD gun, or the power cable connecting the DUT to the two-wire power supply. The advantage of positioning the F-65 current clamp at the tip of the ESD gun allows for highfrequency components of the discharge current to be detected. However, probe loading changes the waveform shape of the acquired discharge current in this configuration. A disadvantage of this configuration is that positioning the current clamp at the tip of the ESD gun adds another measurement cable into the setup. By contrast, positioning the F-65 current clamp at the ESD gun ground strap offers the advantages of being geometrically convenient and minimizing probe loading, however the relatively longer distance between the probe location and the ESD gun tip creates the disadvantage of not detecting the initial peak current due to high-frequency attenuation through the cables, impacting the measured waveform as shown in Figure 5(a).

In addition, the measurement waveforms acquired using the F-65 current clamp require frequency response compensation for the time-domain acquired waveform [17]. For example, the transfer impedance of a typical current clamp is not constant across its operational frequency range, but instead provides a flat response at high frequencies, and increased losses at low frequencies. Thus, the low-frequency slope of the current clamp transfer impedance can result in distortion of the acquired waveform. The high-frequency components associated with the rise time of an ESD pulse are sufficiently captured by the current clamp. However, compensation is needed for the low-frequency response corresponding to the low-frequency trailing end of the pulse. A method for compensating the low-frequency slope of a current clamp using deconvolution is presented in [17], and the resultant waveform is shown in Figure 5(b).

Figure 5. Waveforms acquired using F-65 current clamp. (a) Comparison of the F-65 current clamp monitor location at the ESD gun tip and the ESD gun ground strap. (b) Comparison of the uncompensated frequency response measured using the F-65 current clamp with the compensated F-65 current clamp measurement.

## 2.1. MEASUREMENT RESULTS FOR THE CONTROLLED SETUP

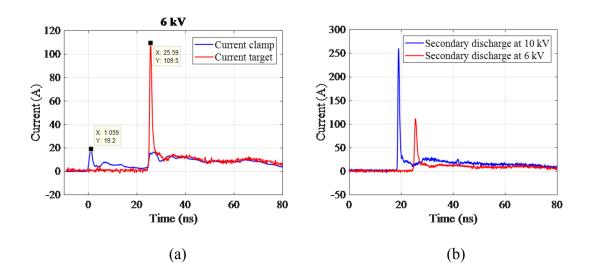

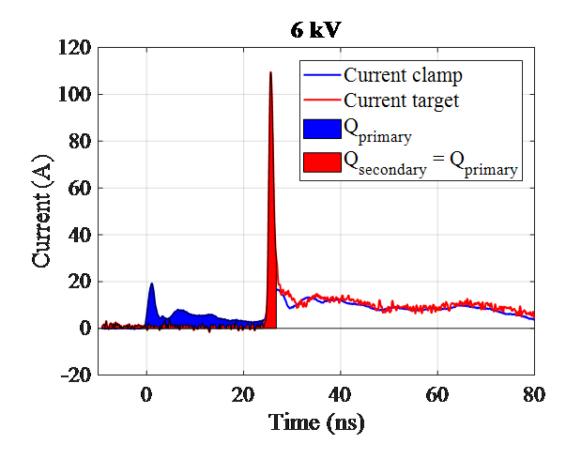

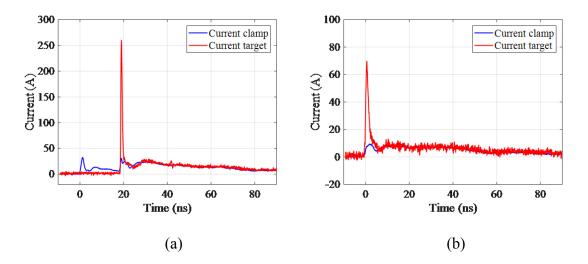

The measurement results for the controlled setup of 6 kV and 10 kV ESD gun voltage settings in contact mode discharge are shown in Figure 6. A spark gap of 0.8 mm

requires approximately 3.91 kV as the minimum breakdown voltage to result in secondary discharge. The breakdown voltage (also called "Paschen value") for a specific spark gap distance is calculated using the formula given in [9]. The time lag between primary and secondary events depends on the discharge voltage setting, gap length, surface materials, and humidity [1]. The higher the discharge voltage, the lower the time lag for the secondary discharge event. An example waveform for the occurrence of the secondary discharge at 10 and 6 kV as well as the influence on time lag is shown in Figure 6(b).

Figure 6. Measured waveforms on the controlled setup. (a) Primary charging waveform measured using an F-65 current clamp, and secondary discharge waveform measured using a current target. (b) Secondary discharge due to 10 kV occurs approximately 6 ns before the secondary discharge due to 6 kV. The primary ESD event occurring at 0 ns is not included in this figure.

# 2.2. MEASUREMENT RESULTS FOR SECONDARY DISCHARGE INSIDE OF A TWO-WIRE POWER SUPPLY

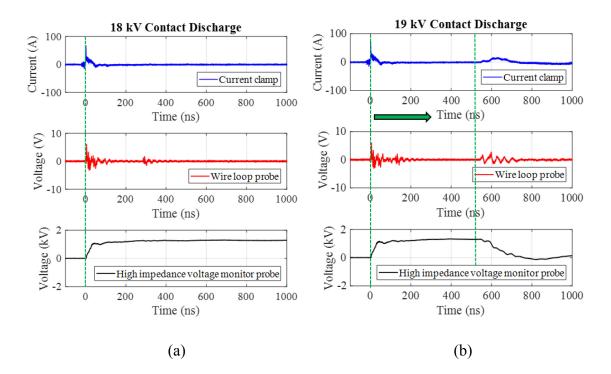

The ESD gun was discharged in contact mode into the metal enclosure as shown in

Figure 3. The waveforms were measured from 6 to 18 kV in steps of 2 kV, and the results

for the 18 kV ESD gun discharge are shown in Figure 7(a). The first vertical dashed line is a visual representation of the time at which the ESD gun was discharged into the DUT. There is no secondary discharge at 18 kV setting as shown in Figure 7(a). At a 19 kV setting, all three measurement monitors identify the occurrence of a secondary discharge event at approximately 545 ns as shown in Figure 7(b). The second vertical dashed line in Figure 7(b) represents the occurrence of the secondary discharge event. The stable voltage amplitude of the high impedance voltage monitor probe shown in Figure 7(a), and its collapsing amplitude approaching zero after approximately 545 ns in Figure 7(b), provide clear evidence of nonexistence and occurrence of a secondary discharge, respectively.

Figure 7. Measured waveforms on the two-wire power supply setup using the F-65 current clamp placed at the tip of the ESD gun measuring the discharge current, the wire loop probe positioned near the two-wire power supply to monitor any disturbances inside of the two-wire power supply and the high impedance voltage probe to monitor the floating metal voltage. (a) 18 kV discharge. (b) 19 kV discharge with secondary ESD event occurring at 545 ns.

#### **3. SOFTWARE-ASSISTED DETECTION**

During ESD compliance testing, multiple test points are chosen for ESD injection. Often, an automated robotic system is tasked with executing a suite of tests, which determine the failure voltage or current levels [18]. While such a system can produce a pass/fail report, it does not help to determine the root cause of the failure due to ESD discharge or secondary discharge events. A software-assisted secondary ESD detection algorithm is proposed to identify the secondary ESD events during testing. To detect an event, the discharge current at the ESD gun tip using an F-65 current clamp and the charge delivered obtained from the current clamp waveform are analyzed.

For an algorithm to differentiate secondary events from primary events, pre- and post-pulses, and reignition events, the characteristics of the primary events must first be introduced to the algorithm during the learning sequence. Operator input to the software is also required to select the appropriate ESD gun voltage setting and the DUT configuration. The proposed testing sequence is illustrated in Figure 8. First, the operator needs to discharge the ESD gun onto a large ground plane and measure the discharge current using a current clamp. The tests should begin with a low voltage setting on the ESD gun, for example, 1 kV, where it is expected that there will be no secondary ESD events occurring inside of the DUT. The current clamp waveform is analyzed for the charge delivered into the DUT, the next rising edge after the primary event and the next fast changing dI/dt (slope) after the primary event. If the charge ratio criteria or the next rising and the next fast changing dI/dt criteria are met, then the algorithm concludes that the secondary ESD

has occurred. Otherwise, the algorithm suggests increasing the ESD gun discharge voltage to the next voltage increment and repeat the test procedure.

Figure 8. Flowchart of the suggested algorithm for secondary ESD detection based on the secondary ESD waveforms acquired using a current clamp.

## **3.1. CHARGE-BASED DETECTION**

One method to detect the occurrence of a secondary ESD event would be to analyze the amount of charge delivered to the DUT. During an ESD test session, the test sequence begins with measuring the charge delivered to a large ground plane. For a low voltage setting of 1 kV, a secondary ESD event is not expected. Once the ground discharge  $Q_{GND}$ result is available to the operator, then the ESD gun is discharged with the same voltage setting to the DUT. The charge delivered to HCP can also be used as a discharge reference value. However, the quantity of charge delivered to the HCP is less than the ground plane discharge. The HCP has a capacitance to the comparatively larger ground plane and it is also connected to the ground plane by two 470 k $\Omega$  resistors in series, thus the ESD gun delivers less quantity of charge to the ground plane.

$$Q(t) = \int I(t) \cdot dt \tag{1}$$

$$Q = C \cdot V \tag{2}$$

In (1), charge Q is the integration of measured current I with respect to time t. In (2), Q is equal to the product of capacitance C and voltage V. In our case, the large ground plane-based discharge is used as reference during the learning sequence while testing. First, the charge  $Q_{\text{DUT }1kV}$  delivered using (1) is determined. The detection algorithm compares the  $Q_{\text{DUT 1kV}}$  with  $Q_{\text{GND 1kV}}$ , and the resulting ratio is  $Q_{\text{Ratio}} = Q_{\text{DUT 1kV}}/Q_{\text{GND 1kV}}$ . It is important to note that this detection method requires a time capture window which includes both events. In addition, the time corresponding to the charge calculation for the ground and the DUT discharge must be equal. If the  $Q_{\text{Ratio}}$  is less than 0.5, then this suggests that the test point is nongrounded (a capacitive load) with a possibility of spark gap structures existing within the DUT geometry causing secondary ESD occurrences at higher test voltages. For example, as shown in Table 1, the charge delivered into the DUT at 1 kV is 14 nC. Using the relation given in (2), where V is equal to the ESD gun voltage of 1 kV. The effective capacitance obtained is approximately 14 pF. If the discharge was injected into a grounded device, most of the ESD gun charge would be delivered into the DUT and  $Q_{\text{Ratio}} = Q_{\text{DUT }1kV}/Q_{\text{GND }1kV}$  would be approaching unity. Since the  $Q_{\text{DUT}}$  is approximately 14 nC and the  $Q_{\text{Ratio}}$  is less than 0.5, with a capacitance of 14 pF, it strongly suggests that

the DUT is a nongrounded device. This provides an indicator that a secondary ESD event may be possible if one of the spark-gap structures breaks down at a higher ESD voltage setting.

Since at 1 kV the charge ratio is not greater than 0.5, the operator is guided to increase the ESD gun voltage to 2 kV and the process is then repeated. If the  $Q_{\text{Ratio}}$  criteria for  $Q_{\text{DUT}_{2kV}}$  with  $Q_{\text{GND}_{2kV}}$  is similar to the previous discharge voltage, then the ESD testing is continued with higher ESD gun test voltages in +1 kV increments. It is important to note that  $Q_{\text{Ratio}}$  will remain the same at higher voltages, because contact mode ESD gun discharges are linearly proportional to the voltage setting. However, this holds true only when no secondary ESD occurs.

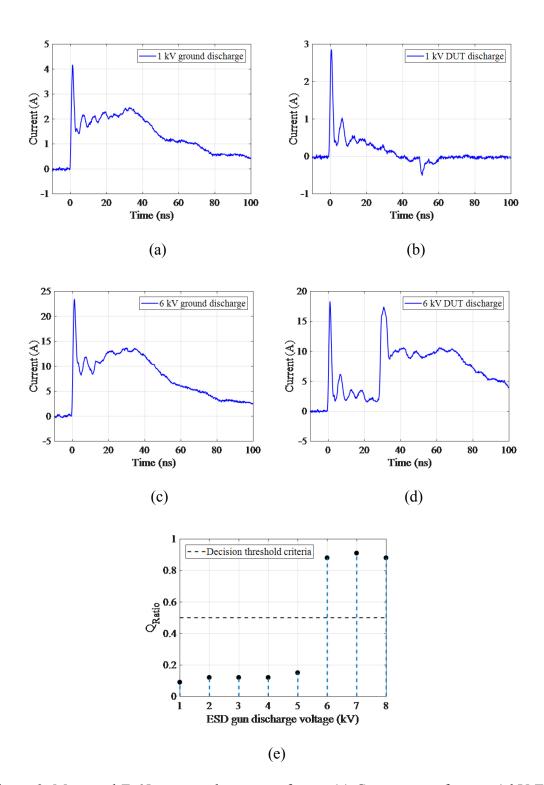

Table 1 provides the  $Q_{\text{Ratio}}$  values obtained during a learning sequence from 1 to 8 kV applied to the controlled setup. Figure 9 illustrates the current waveforms for the low voltage 1 kV in which no secondary ESD event occurred. In addition, it depicts the waveforms at 6 kV, when the secondary ESD occurred. A  $Q_{\text{Ratio}}$  plot is illustrated in Figure 9(e), which depicts the increase in the charge delivered into a DUT when a secondary ESD event occurs.

| ESD gun Voltage | Charge delivered to ground $Q_{\text{GND}}$ | Charge delivered to DUT $Q_{\text{DUT}}$ | $Q_{\text{Ratio}} = Q_{\text{DUT}}/Q_{\text{GND}}$ |

|-----------------|---------------------------------------------|------------------------------------------|----------------------------------------------------|

| 1 kV            | 140 nC                                      | 14 nC                                    | 0.10                                               |

| 2 kV            | 250 nC                                      | 29 nC                                    | 0.12                                               |

| 3 kV            | 393 nC                                      | 48.4 nC                                  | 0.12                                               |

| 4 kV            | 475 nC                                      | 57.06 nC                                 | 0.12                                               |

| 5 kV            | 659.3 nC                                    | 98.62 nC                                 | 0.15                                               |

| 6 kV            | 825 nC                                      | 727.5 nC                                 | 0.88                                               |

| 7 kV            | 941 nC                                      | 856.9 nC                                 | 0.91                                               |

| 8 kV            | 1132 nC                                     | 991.6 nC                                 | 0.88                                               |

Table 1. Learning sequence and charge based analysis.

Figure 9. Measured F-65 current clamp waveforms. (a) Current waveform at 1 kV ESD gun discharge to ground plane. (b) Current delivered at 1 kV ESD gun discharge to DUT. (c) Current waveform at 6 kV ESD gun discharge to ground plane. (d) Current delivered at 6 kV ESD gun discharge to DUT, with a secondary ESD event. (e)  $Q_{\text{Ratio}}$  parameter for a test sequence from 1 to 8 kV based on the Table 1 data.

During the testing sequence with incrementally higher ESD gun voltage discharges, when  $Q_{\text{Ratio}}$  is higher than 0.5, the software identifies it as a secondary ESD event occurrence. For example, in the controlled setup geometry depicted in Figure 1, for a 6 kV ESD gun discharge setting,  $Q_{\text{Ratio}} = Q_{\text{DUT}_{6kV}}/Q_{\text{GND}_{6kV}}$  is greater than 0.5. Thus, the quantity of charge delivered to the nongrounded metal produces sufficient overvoltage to break down the spark gap distance within the DUT geometry. The relationship between charge and voltage is given in (2), where *C* is the capacitance of the nongrounded metal to the grounded reference which is a constant based on DUT geometry. Therefore, as the ESD gun voltage level is increased, a higher amount of charge is delivered with each subsequent ESD discharge into the DUT. Since the nongrounded metal has a fixed capacitance, the amount of voltage generated across the spark gap in the nongrounded metal increases with each higher ESD gun voltage setting.

This detection methodology is based on a learning sequence which initiates with low test voltages and does not require the operator to have knowledge of the internal DUT geometry details, such as the nongrounded metal's capacitance, or the spark gap distances. As an example, if the maximum reliability level for testing is 8 kV, and a secondary ESD event has not yet occurred, then the DUT is considered immune to secondary ESD events for voltages up to 8 kV.

**3.1.1. Total Charge in the Secondary and Primary ESD Event.** Analyzing events using the concept of total charge delivered into the controlled setup is shown in Figure 6(a). It is observed that the charge associated with the secondary ESD event is more than the primary event. The F-65 current clamp measures the ESD gun discharge and the current target measures the secondary ESD. To understand the QDUT delivered, the

measured waveform is further analyzed in terms of Qprimary and Qsecondary ESD events. Here, the primary ESD event was defined from 0 ns to approximately 25 ns. The total charge delivered during this time window is approximately 130 nC.

The secondary ESD event begins at approximately 25 ns. The total charge contained in Qprimary from 0 to 25 ns is equal to total charge contained in Qsecondary from time 25 to 27 ns, due to the law of charge conservation. After 27 ns, the extra current measured by the current target is due to the residual charge delivered by the ESD gun. The charge delivered during the primary and secondary events is indicated by the shaded areas of Figure 10.

Figure 10.  $Q_{\text{primary}} = Q_{\text{secondary}} = \text{approximately 130 nC}$ . Charge delivered after 27 ns is due to residual current from the ESD gun.

The ESD gun in contact mode delivers charge to the nongrounded floating metal, but does not deliver complete charge into the floating structure until after the spark gap distance breaks down. At 25 ns, the spark gap distance of approximately 0.8 mm breaks down due to the overvoltage potential, causing the secondary ESD event. The spark resulting from the spark gap breakdown becomes a nonlinear resistive conductive path connecting the nongrounded metal with the ground reference. At this time, the ESD gun, still connected to the nongrounded plate in contact mode, has a residual charge current path to ground formed by the secondary ESD spark conductive channel which can be given by  $Q_{DUT} = Q_{primary} + Q_{secondary} + Q_{residual_ESD_gun}$ .

**3.1.2. Events due to Residual Charge in the ESD Gun.** After the primary and secondary discharge events occur, multiple secondary discharges, referred to as ESD gun reignition discharges, are possible due to residual charge buildup on the ESD gun tip. The software-based detection method can only identify multiple secondary events which occur within the same time capture window as the primary event. However, since these ESD gun reignition discharges have lower peak current than the secondary ESD event, they can be considered less important than the secondary ESD events for detection purposes.

In such situations,  $Q_{\text{primary}}$  will be discharged during the secondary ESD event. The spark initiated by the secondary ESD allows residual charge to be delivered from the ESD gun tip after the occurrence of secondary ESD. The charge on the primary nongrounded metal must have sufficient overvoltage for the spark gap to break down for reignition events to occur. An example of reignition of the ESD gun after 5.8 ms after the first triggered event is shown in Figure 11.

Figure 11. (a) First triggered event on the oscilloscope. (b) Reignition discharge event is 5.8 ms after the first triggered event with an ESD gun voltage setting of 10 kV.

## **3.2. DISCHARGE CURRENT WAVEFORM-BASED DETECTION**

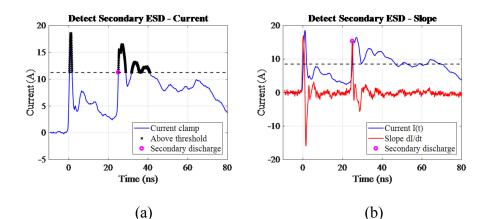

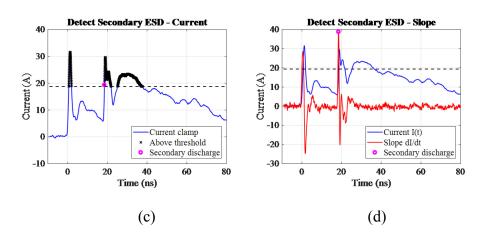

A detection method based on the rising edge and dI/dt is applied to the waveforms generated using the configuration shown in Figure 1. The detection results are determined for the two discharge cases of 6 and 10 kV, shown in Figure 12.

Waveform-based detection using the rising edges of the current waveform is depicted in Figure 12(a) and (c). The peak discharge amplitude is determined for the contact mode discharges using the transfer function 3.75 A/kV. As an example, an ESD gun voltage setting of 6 kV would be converted to 22.5 A. Using a 50% threshold of the peak amplitude, the primary event positive-polarity trigger threshold level is determined. The waveform sample points located above these threshold criteria are highlighted in Figure 12(a) and (c). A time gap separates the primary and secondary ESD events. In Figure 12(a), a time of 25 ns is detected by the suggested algorithm to be the start of the secondary ESD event.

The slope-based detection method calculates dI/dt. By applying a threshold crossing to the derivative function, the start time for primary or secondary discharge can be determined, as shown in Figure 12(b) and (d).

The secondary ESD event current can reach five times the amplitude of the primary current [1]–[4] and have faster rise times. If the secondary ESD event is not probed in close proximity to the source, a degradation in measured rise time and current amplitude will occur. This degradation of the acquired waveform can lead to missed detection using the rising edge and dI/dt (slope) based detection methods.

Figure 12. Secondary ESD detection using the rising edge and slope detection algorithm. (a) 6 kV rising edge-based detection. (b) 6 kV slope-based detection. (c) 10 kV rising edge-based detection. (d) 10 kV slope-based detection.

#### 4. DISCUSSION

The suggested software-assisted detection of a secondary ESD event is based on measurable quantities such as current and charge. For system-level testing, it may be challenging to physically access all of the measurement test points. The use of a current clamp allows for current measurements to be performed from outside of the DUT. The acquired current waveform dataare used for secondary ESD detection based on the rising edge and slope-based algorithms.

However, these methods have two limitations based on the bandwidth of the measured data. First, since the F-65 current clamp is required to capture the current waveform, but also results in measurement system bandwidth reduction, highfrequency content such as fast transition times are reduced, which limits the software algorithm abilities to detect all occurrences of secondary discharge. Second, if the placement of the F-65 current clamp is relatively far from the occurrence of secondary discharge, then high-frequency content will be filtered by the transmission path, resulting in further system bandwidth reduction at the observation point. The charge-based method described in Section III resolves the bandwidth limitation problems, which impacted the accuracy of the rising edge and slope-based algorithms. An example in which the chargedbased method succeeds where the rising edge and slope based algorithms fail, is in a two-wire power supply setup, in which the F-65 current clamp did not capture the secondary ESD event rise time with high resolution. This leads to a missed detection using the rising edge and the slope method as shown in Figure 13.

In Figure 13, the charge-based method does detect the extra charge delivered during the secondary ESD event that ranges from approximately 550 to 800 ns. In order for the detection algorithm to work, the algorithm must be provided  $Q_{\text{Ratio}}$  values starting with a low-voltage case and then incrementing subsequently higher ESD gun voltages.

Figure 13. Detection based on the rising edge and the slope of the measured current for the two-wire power supply setup.

In order to determine if a device is floating, it should first be checked with lowvoltage inputs. Once a low  $Q_{\text{Ratio}}$  value is computed for low-voltage inputs, this confirms a floating device which may be subject to spark gap breakdown at higher input voltages. The detection logic during the learning process is based on the sudden change in the  $Q_{\text{Ratio}}$  value during a secondary ESD event which did not previously occur for low-voltage inputs when the  $Q_{\text{Ratio}}$  value was low. To facilitate more rapid testing for secondary ESD, a smaller set of input voltages could be used. For example, the operator could first inject with a low voltage of 1 kV to verify a floating device, then input a second high voltage at the maximum desired ESD reliability test level, for example, 8 kV. If the  $Q_{\text{Ratio}}$  at 8 kV and the  $Q_{\text{Ratio}}$  at 1 kV are both below 0.5, then a secondary ESD event did not occur. However, if the  $Q_{\text{Ratio}}$  at 8 kV is > 0.5 and the  $Q_{\text{Ratio}}$  at 1 kV < 0.5, then this indicates the presence of a secondary ESD event.

An additional advantage of the charge-based method is immunity to an overlapping primary and secondary discharge. In the case where overvoltage across the spark gap results in a secondary ESD event that overlaps with the primary event, the overlapping events may result in non-detection by the rising edge and slope-based methods, whereas this situation can be clearly detected using the charge-based method.

## **5. CONCLUSION**

The purpose of this study was to analyze secondary discharge events acquired with various measurement setups, in order to identify waveform parameters for software-assisted algorithms, and to verify the occurrence and detection of secondary ESD events using current clamp-acquired waveforms. Multiple measurement setups and configurations were used, and several software algorithms were applied for detection. The use of software-assisted algorithms based on the acquired current waveforms can be flexible across multiple measurement setup scenarios, allowing secondary discharge events to be identified. The proposed detection methods were shown to work well across a range of configurations. As shown in Figure 8, multiple methods can also be combined to increase detection robustness.

#### REFERENCES

- F. Wan, V. Pilla, J. Li, D. Pommerenke, H. Shumiya, K. Araki, "Time Lag of Secondary ESD in Millimeter-Size Spark Gaps," IEEE Trans. Electromagn. Compat., vol. 56, no. 1, pp. 28–34, Feb. 2014.

- [2] H. Wolf, H. Gieser, "Secondary discharge A potential risk during system level ESD testing," in Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), 2015 37th, vol., no., pp.1-7, 27 Sept.-2 Oct. 2015.

- [3] J. Xiao, D. Pommerenke, J. L. Drewniak, H. Shumiya, T. Yamada, and K. Araki, "bmodel of secondary ESD for a portable product," Electromagnetic Compatibility (EMC), 2011 IEEE International Symposium on, 14-19 Aug. 2011, pp. 56-61.

- [4] J. Xiao, D. Pommerenke, J. L. Drewniak, H. Shumiya, J. Maeshima, T. Yamada, and K. Araki, "Model of secondary ESD for a portable electronic product," IEEE Trans. Electromagn. Compat., vol. 54, no. 3, pp. 546–555, Jun. 2012.

- [5] S. Marathe, P. Wei, S. Ze, L. Guan, and D. Pommerenke, "Scenarios of ESD Discharges to USB Connectors," 2017 39th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Tuscon, AZ, 2017, pp. 1-6.

- [6] Y. Gan, A. Talebzadeh, X. Xu, S. Shinde, Y. Zeng, K. Kim, and D. Pommerenke, "Experimental Characterization and Modelling of Surface Discharging for an Electrostatic Discharge (ESD) to an LCD," IEEE Trans. Electromagn. Compat., vol. 60, no. 1, pp. 96–106, Feb. 2018.

- [7] P. Wei, S. Marathe, J. Zhou, and D. Pommerenke, "ESD Susceptibility Evaluation on Capacitive Fingerprint Module," 2017 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMCSI), pp. 175-180.

- [8] J. Park, J. Kim, J. Lee, C. Jo and B. Seol, "System-level ESD noise induced by secondary discharges at voltage suppressor devices in a mobile product," 2017 Asia-Pacific International Symposium on Electromagnetic Compatibility (APEMC), Seoul, South Korea, 2017, pp. 70-72.

- [9] D. Pommerenke, "ESD: Transient fields, arc simulation and rise time limit," J. Electrostat., vol. 36, pp. 31–54, 1995.

- [10] T. Ishida, Y. Tozawa, M. Takahashi, O. Fujiwara, and S. Nitta, "A Measurement on Electromagnetic Noises from ESD Generator just Before and After ESD Testing," Proceedings of 2014 International Symposium on Electromagnetic Compatibility, Tokyo (EMC' 14/Tokyo), 16A2-B2, pp.737-740 (2014).

- [11] G. Notermans, H.-M. Ritter, B. Laue, and S. Seider, "Gun tests of a USB3 host controller board," in Proc. EOS/ESD Symp., Garden Grove, CA, USA, 2016.

- [12] S. Marathe, H. Rezaei, D. Pommerenke, and M. Hertz, "Detection Methods for Secondary ESD Discharge During IEC 61000-4-2 Testing," 2017 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMCSI), pp. 152-157.

- [13] IEC 61000-4-2, 'Electromagnetic compatibility (EMC) Part 4-2: Electrostatic discharge immunity test', Ed. 2.0, 2008.

- [14] High Voltage Pulse Attenuator. [Online]. Available: https://www.esdemc.com/

- [15] Operators' manual WaveMaster 8 Zi/Zi-A/Zi-B Oscilloscopes [Online]. Available: http://cdn.teledynelecroy.com/files/manuals/wavemaster-8zi-ab-operators-manual.pdf

- [16] The Impact of Digital Oscilloscope Blind Time on Your Measurements Application Note [Online]. Available: https://www.rohde-schwarz.com/us/applications/the-impact-ofdigital-oscilloscope-blind-time-on-your-measurements-application-note\_56280-15813.html

- [17] S. Yang, J. Zhou, D. Pommerenke, and D. Liu, "A simple frequency response compensation method for current probe measurements of ESD currents," 2017 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMCSI), pp. 175-180.

- [18] SmartZap-Amber Precision Instruments [Online]. Available: http://www.amberpi.com/products\_smartzap.php

- [19] S. Marathe, D. Li A. Hosseinbeig, H. Rezaei, P. Wei, J. Zhou, and D. Pommerenke, "On Secondary ESD Event Monitoring and Full-wave Modeling Methodology," 2017 39th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Tuscon, AZ, 2017, pp. 1-6.

# II. MEASUREMENT-BASED CHARACTERIZATION AND FULL-WAVE MODELING OF ESD TO DISPLAY TOUCHSCREEN SENSORS

S. Marathe

Department of Electrical Engineering Missouri University of Science and Technology Rolla, Missouri 65409–0050 Tel: 573–202–1260 Email: skmcr4@mst.edu

## ABSTRACT

An electrostatic discharge (ESD) to display cover glass can damage touchscreen traces by sparkless corona discharges on the glass surface. The ESD induced currents are measured in an evaluation setup, which resembles the touch pattern. Each air discharge event leads to multiple waveforms, which are acquired using a fast-retrigger mode in the oscilloscope. The induced currents are analyzed using the peak value, and the total charge. The statistical behavior of the induced currents is determined for different parameters such as glass thickness, indium tin oxide layer equivalent resistance, sensor spacing to the ground plane, air discharge polarity and voltage, and ESD gun approach speed. The goal is to create a full-wave simulation model to predict the induced currents in the touchscreen sensors for various discharge parameters. Using the full-wave model, the source excitation current waveform is determined, which allows prediction of the displacement currents into

a single touchscreen sensor patch. The waveform then can be applied to different touchscreen sensor display geometries to determine if damage might occur.

**Keywords:** Air discharge, corona discharge, displacement current, display, human metal model (HMM), surface discharge.

### **1. INTRODUCTION**

Multiple mechanisms can damage a display if it is subjected to an Electrostatic Discharge (ESD) event. ESD events can lead to soft and hard-failures in display products [1]-[2]. A spark cannot penetrate through the display, but if the display is not well-insulated at the product edges, during an ESD event a spark can occur which can couple to the driving circuits of the display [3]. The spark may hit the flex cable or if the insulation undergoes an electrical breakdown [4], thus, leading to permanent damage to the insulation layer at the edges of the display. For well-designed displays products, the spark cannot occur, thus, leading to sparkless discharges. Even though there is no visual indication of the spark, a corona current charges the surface of the glass [5]-[6]. Displacement current flows through the display cover glass into the internal touchscreen structures.

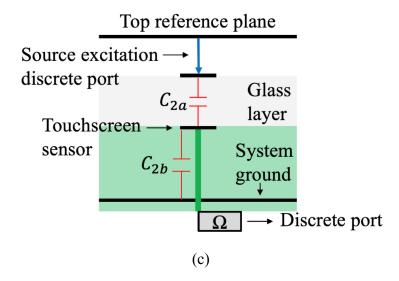

Many consumer electronic products provide display and touchscreen functionality. The touchscreen sensors are typically positioned under the display cover glass. The users touch the display cover glass and the touchscreen sensors record the touch location from the user. The user can be charged and may discharge on the display cover glass. The ESD event on the glass surface leads to induced currents through the display cover glass into the touchscreen sensors. Figure 1 illustrates the simplified stackup of a touchscreen display electronic product. Glass layer represents a display cover glass, which typically has the touchscreen sensors on the inner side of the display glass surface. The touchscreen sensor has a capacitance to its system ground. The indium tin oxide (ITO) layer which connects the sensor to the display IC has an equivalent series resistance whose value depends on the layout of trace connection between the sensor and the display IC.

Figure 1. Typical touchscreen sensor geometry. (a) Typical display with touchscreen sensors. (b) Equivalent circuit capacitances and resistances of a single touchscreen sensor.

The sparkless discharge leads to deposition of charges on the glass surface, which can be visualized using the Lichtenberg's dust figure [7]. The visualization of the charges illustrated that the positive discharges led to a branching structure, while the negative discharges led to more concentrated, not branching like charge deposition [6], [8]. However, the dust figure only allows the visualization of the charges but does not show the time-domain waveforms. To address this problem, Muller [9]-[11] proposed a setup to measure the partial currents by using a segmented ground plane. In [6], a similar approach was used to capture the charge, streamer velocity, time, and displacement currents.

This paper builds on the work performed by Gan *et al.* [6] and focuses on quantifying the worst-case risk due to sparkless ESD discharges to the touchscreen sensors

underneath the display cover glass. Since the display is an insulator, air discharge testing is performed. An automated measurement setup was developed to control parameters such as ESD generator approach speed, the temperature, and relative humidity. For a given display geometry, the ESD generator total discharge current, and the ESD induced waveforms into the touchscreen sensor patches are monitored. A full-wave simulation modeling approach is presented to obtain the source excitation waveforms, which leads to the ESD induced waveform into a single touchscreen sensor patch.

#### 2. MEASUREMENT SETUP

An evaluation geometry was designed and manufactured. The setup was automated to measure multiple waveforms for each test scenario. Since, the air discharge event has variations, having multiple discharges provides a statistical distribution of the induced currents into the touchscreen sensor patches. To control the parameters such as temperature and relative humidity, the setup was positioned in a climate chamber. The chamber held the temperature at 75°F (24°C) and relative humidity (RH) of 32% approximately. Human metal model (HMM) discharges were performed on the evaluation geometry to quantify the ESD risk, as the testing process of displays is performed using an ESD generator in air discharge mode with a rounded metal tip [12].

## 2.1. EVALUATION PRINTED CIRCUIT BOARD (PCB) GEOMETRY

An evaluation PCB is designed to analyze the influence of touchscreen sensor geometry parameters such as display glass thickness ( $C_{2a}$ ), sensor-to-system-ground capacitance ( $C_{2b}$ ), and the ITO layer equivalent resistance ( $R_{trace}$ ) as shown in Figure 1. The evaluation PCB is designed to match a typical touchscreen sensor geometry, as shown in Figure 2. Multiple squares are representative of the various touchscreen sensor patches below the display cover glass. These sensors are designed on the top layer of thee evaluation PCB. Vias connect each sensor to the bottom layer, where a surface mount metal electrode leadless face (MELF) resistor is connected in series. This resistance represents the equivalent Indium Tin Oxide (ITO) layer resistance in a display product. The third layer (inner layer) of the PCB is assigned the ground reference plane.

Figure 2. Designed evaluation PCB touchscreen sensor patch display geometry.

## 2.2. AUTOMATED HMM DISCHARGE SETUP

To enable acquisition of multiple discharges for measuring the statistical distribution of the ESD induced currents, the setup was automated. The block diagram of the full-automated setup is depicted in Figure 3.

**2.2.1. ESD Generator Approach Speed Control.** Guide-rods were used to guide the movement of the ESD generator. Two motors along with forward and return single pole double throw (SPDT) switches were installed to guide the movement of the ESD generator at a constant speed of approach toward the device under test (DUT). The

motor control board was designed to control the speed, direction, and movement of the motors.

**2.2.2. ESD Generator Voltage and Polarity.** A USB-to-Serial and Serial-to-Optical interfaces circuits were designed and implemented on the ESD generator control board. The control board allowed remote control setting of the ESD generator test voltage and polarity of the discharges.

**2.2.3. Shielded Enclosure.** The display cover glass and the evaluation PCB were installed vertically at the enclosure slot facing the ESD generator air discharge tip. The DUT was installed at the enclosure slot, to prevent any undesired field coupling from the ESD generator [6], [13]-[15] into the measured waveforms on the oscilloscope. The direct probing coax cables monitored the respective touchscreen sensor patch waveforms during an air discharge event. ESD attenuators and ESD protectors were connected between the coax cables and the individual oscilloscope channels to prevent any unintentional ESD stress damage to the oscilloscope channels.