# Scholars' Mine

**Doctoral Dissertations**

Student Theses and Dissertations

Summer 2015

# Advanced control of grid-connected multilevel power electronic rectifiers

Sangin Lee

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Electrical and Computer Engineering Commons

**Department: Electrical and Computer Engineering**

### **Recommended Citation**

Lee, Sangin, "Advanced control of grid-connected multilevel power electronic rectifiers" (2015). Doctoral Dissertations. 2411.

https://scholarsmine.mst.edu/doctoral\_dissertations/2411

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# ADVANCED CONTROL OF GRID-CONNECTED MULTILEVEL POWER ELECTRONIC RECTIFIERS

by

# SANGIN LEE

# A DISSERTATION

Presented to the Faculty of the Graduate School of the MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

DOCTOR OF PHILOSOPHY

in

**ELECTRICAL ENGINEERING**

2015

Mehdi Ferdowsi, Advisor Mariesa L. Crow Jonathan W. Kimball Jagannathan Sarangapani S. N. Balakrishnan

# PUBLICATION DISSERTATION OPTION

This dissertation consists of the following three articles:

- Paper I, Pages 14–37, "Phase-Shifting Reference Strategy for Voltage Balancing in Neutral-Point Clamped Converter," to be summitted in *IEEE Transactions on Power Electronics*.

- Paper II, Pages 38–53, "Capacitor Voltage Regulation and Pre-Charge Routine for a Hybrid Multilevel Rectifier," to be summitted in *IEEE Transactions on Power Electronics*.

- Paper III, Pages 54–70, "Multiple Reference Frame-Based Harmonic Compensation for Grid Currents in the Three Phase Hybrid Multilevel Rectifier," to be summited in *IEEE Transactions on Power Electronics*.

### **ABSTRACT**

Multilevel power electronic converters have been gaining attention due to their ability to supply high amounts of power and to handle high voltage levels. In this dissertation, grid connected AC–DC rectifier application is investigated with different topologies and control scheme.

At first, neutral point clamped (NPC) rectifier is employed to transfer power from the grid to the load. The NPC rectifier has two capacitors in order to build multilevel output voltage. However, it causes voltage unbalancing problem. Therefore, the new method has been proposed to regulate each capacitor voltage at the same voltage level. Experimental results show that it is effective to balance capacitor voltages of the NPC and it can improve total harmonic distortion (THD) of the grid current as a result.

Furthermore, 7 voltage levels can be achieved by using hybrid multilevel rectifier which consists of an NPC and cascaded H-bridges (CHB). Because the hybrid multilevel rectifier has total 8 capacitors which are completely discharged at first, large inrush currents from the grid might cause hazards. Therefore, the paper develops a pre-charge routine for building it up to steady state operation in which unity power factor control (PFC) and load voltage control are achieved.

Finally, multiple reference frame theory (MRF) is used to improve THD of the grid currents when the hybrid multilevel rectifier is connected with distorted grid voltage source. After calculating 5th harmonic of the grid current in real time, the voltage reference for the hybrid multilevel rectifier will be compensated in a feedback loop. Experimental results show validity in improving THD of the grid currents.

#### **ACKNOWLEDGEMENTS**

I would never have been able to finish my dissertation without the guidance of my committee members, help from friends, and support from my family. Especially for my advisor Dr. Mehdi Ferdowsi, I cannot express enough thanks to him for his continued support and encouragement. He has suggested not only solutions when I encountered problems during building up the experimental set, but also research topics that need me to develop new knowledge and technology. That made me study hard and finally gave me an opportunity to achieve better results. I would like to express my deepest gratitude to my advisor, Dr. Mehdi Ferdowsi, for his excellent guidance, caring, patience, and providing me with an excellent atmosphere for doing research.

I would like to thank Dr. Keith Corzine, who taught me the basic knowledge of power electronics and motor drives. Especially, I learned the concept of the multiple reference frame theory experience in the class. Therefore, it finally helped me apply the theory on grid current harmonic compensation. I would also like to thank Dr. Crow, Dr. Kimball, Dr. Sarangapani and Dr. Balakrishnan for guiding my research for the past several years and helping me to develop my background in power system engineering and optimal theory.

I would also like to thank my parents. They were always supporting and encouraging me with their best wishes and trying to rescue me from my deep loneliness. Also, I would like to appreciate encouragement and positivity from my brother, sister-in-law, my sister and brother-in-law.

# TABLE OF CONTENTS

| Pa                                                                                            | ιge  |

|-----------------------------------------------------------------------------------------------|------|

| PUBLICATION DISSERTATION OPTION                                                               | iii  |

| ABSTRACT                                                                                      | iv   |

| ACKNOWLEDGEMENTS                                                                              | v    |

| LIST OF ILLUSTRATIONS                                                                         | ix   |

| LIST OF TABLESx                                                                               | ciii |

| SECTION                                                                                       |      |

| 1. INTRODUCTION                                                                               | 1    |

| 1.1. APPLICATIONS                                                                             | 1    |

| 1.2. MULTI LEVEL CONVERTER TOPOLOGIES                                                         | 4    |

| 1.3. MODULATION METHODS FOR MULTILEVEL CONVERTER                                              | 6    |

| 1.4. NEW VOLTAGE BALANCING METHOD FOR NPC                                                     | 8    |

| 1.5. PRE-CHARGE ROUTINE FOR HYBRID MULTILEVEL RECTIFIER                                       | 8    |

| 1.6. GRID CURRENT HARMONIC COMPENSATION BY USING MRF                                          | 9    |

| PAPER                                                                                         |      |

| I. PHASE-SHIFTING REFERENCE STRATEGY FOR VOLTAGE BALANCING IN NEUTRAL-POINT CLAMPED CONVERTER | 10   |

| I. INTRODUCTION                                                                               | 10   |

| II. SWITCHING SCHEME AND TWO REFERENCE SIGNALS OF THE NPC TOPOLOGY                            | 13   |

| III. PHASE-SHIFTING REFERENCE STRATEGY                                                        | 16   |

| IV. OVERLAP PERIOD HAPPENING IN PHASE-SHIFTING REFERENCE                                      | 20   |

| V. PHASE COMPENSATION CONTROL LOOP                                                            | .22  |

|      | VI. SIMULATION AND EXPERIMENTAL RESULTS                                                                           | 23 |

|------|-------------------------------------------------------------------------------------------------------------------|----|

|      | VII. CONCLUSION                                                                                                   | 31 |

|      | REFERENCES                                                                                                        | 33 |

| II.  | CAPACITOR VOLTAGE REGULATION AND PRE-CHARGE ROUTINE FOR A HYBRID MULTILEVEL RECTIFIER                             | 36 |

|      | I. INTRODUCTION                                                                                                   | 36 |

|      | II. HYBRID MULTILEVEL RECTIFIER                                                                                   | 38 |

|      | III. REGULATING H-BRIDGE VOLTAGES                                                                                 | 40 |

|      | IV. UNITY POWER FACTOR CONTROL AND LOAD VOLTAGE CONTROL                                                           | 41 |

|      | V. PRE-CHARGE ROUTINE                                                                                             | 42 |

|      | VI. OPEN LOOP CONTROL OF THE HYBRID MULTILEVEL RECTIFIER                                                          | 44 |

|      | VII. EXPERIMENTAL RESULTS                                                                                         | 45 |

|      | VIII. CONCLUSION                                                                                                  | 50 |

|      | REFERENCES                                                                                                        | 51 |

| III. | MULTIPLE REFERENCE FRAME-BASED HARMONIC COMPENSATION FOR GRID CURRENTS IN THREE PHASE HYBRID MULTILEVEL RECTIFIER | 53 |

|      | I. INTRODUCTION                                                                                                   | 53 |

|      | II. HYBRID MULTILEVEL RECTIFIER                                                                                   | 55 |

|      | III. MULTIPLE REFERENCE FRAME THEORY                                                                              | 57 |

|      | IV. CONTROL LOOP FOR GRID CURRENT COMPENSATION                                                                    | 58 |

|      | V. SIMULATION                                                                                                     | 61 |

|      | VI. EXPERIMENTAL RESULTS                                                                                          | 65 |

|      | VII CONCLUSION                                                                                                    | 67 |

| REFERENCES | 68 |

|------------|----|

| SECTION    |    |

| 2. SUMMARY | 71 |

| REFERENCES | 73 |

| VITA       | 77 |

# LIST OF ILLUSTRATIONS

|                                                                                                                    | Page |

|--------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.1. Multilevel converter application overview                                                              | 2    |

| Figure 1.2. Multilevel converter in PV application                                                                 | 3    |

| Figure 1.3. Five-level cascaded multilevel converter connected to a multiple pole low-speed wind-turbine generator | 4    |

| Figure 1.4. Peak shaving and valley filling                                                                        | 4    |

| Figure 1.5. Neutral point clamped multilevel topology                                                              | 5    |

| Figure 1.6. Flying capacitor multilevel topology                                                                   | 5    |

| Figure 1.7. Cascaded H-bridge multilevel topology                                                                  | 5    |

| Figure 1.8. Hybrid multilevel topology                                                                             | 6    |

| Figure 1.9. Selective harmonic elimination method                                                                  | 7    |

| Figure 1.10. Selective harmonic elimination PWM method                                                             | 7    |

| Figure 1.11. Asymmetric modulation method                                                                          | 7    |

| Figure 1.12. Asymmetric PWM method                                                                                 | 7    |

| PAPER I                                                                                                            |      |

| Figure 1. Three-phase neutral-point clamped AC/DC rectifier                                                        | 14   |

| Figure 2. Three modes of switching in a case of phase A                                                            | 15   |

| Figure 3. Two reference signals and the output $V_{\rm u0}$                                                        | 16   |

| Figure 4. PSR strategy with upper and lower reference signals                                                      | 17   |

| Figure 5. Simulation result when applying no voltage balancing method                                              | 18   |

| Figure 6. Two capacitor voltages when applying +0.2 rad. (+11.5°) as <i>phase_compensation</i> on (2) and (3)      | 19   |

| as phase_compensation on (2) and (3)                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------|

| Figure 8. Overlap period when applying $-0.2$ rad. $(-11.5^{\circ})$ as <i>phase_compensation</i> on (2) and (3)      |

| Figure 9. An impractical case of the overlap period with $-0.7$ rad. $(-40^{\circ})$ of the <i>phase_compensation</i> |

| Figure 10. Feedback control block diagram for PSR strategy                                                            |

| Figure 11. Experimental set configuration and control block diagram24                                                 |

| Figure 12. Experimental set configuration                                                                             |

| Figure 13. TMS320F28335 DSP, analog input board (AIB) and optical signal transmission board                           |

| Figure 14. Transient response of the two capacitor voltages and   phase_compensation value                            |

| Figure 15. <i>Phase_compensation</i> value of (2) and (3) in a steady state in Figure 14. from 2.7 sec to 2.75 sec    |

| Figure 16. Simulation result in a steady state without a voltage balancing method27                                   |

| Figure 17. Simulation result in a steady state using the PSR method                                                   |

| Figure 18. Experimental results in a steady state without a voltage balancing method                                  |

| Figure 19. Experimental results in a steady state using the PSR method29                                              |

| Figure 20. Transient response of the two capacitor voltages                                                           |

| Figure 21. Magnitude spectrum of the grid current and THD comparison31                                                |

| PAPER II                                                                                                              |

| Figure 1. Hybrid multilevel rectifier consisting of the NPC and the CHBs39                                            |

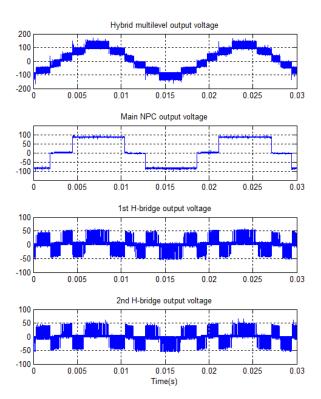

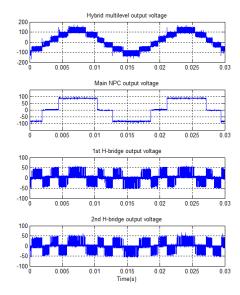

| Figure 2. Experimental results explaining hybrid modulation method39                                                  |

| Figure 3. Feedback loop block diagram for regulating H-bridge voltage40                                               |

| Figure 4. Feedback loop block diagram for unity displacement power factor control and load voltage control                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5. Large inrush currents without damping resistors                                                                                                    |

| Figure 6. Acceptable grid currents with damping resistors                                                                                                    |

| Figure 7. Calculation of the value $V_m$ and $\phi$                                                                                                          |

| Figure 8. Acceptable grid currents with damping resistors after connecting with the grid                                                                     |

| Figure 9. Acceptable grid currents after removing damping resistors46                                                                                        |

| Figure 10. Grid currents and the rectifier output voltage Vu0 after activating NPC and CHB switching                                                         |

| Figure 11. Transient responses of grid current and hybrid multilevel phase voltage output when voltage feedback loop is activated with $V_{DC\_ref}$ =200V47 |

| Figure 12. Transient responses of NPC voltages $V_{DC1}$ and $V_{DC2}$ when voltage feedback loop is activated with $V_{DC\_}$ ref=200                       |

| Figure 13. Transient responses of H-bridge voltages VHBa2, VHBa1, VHBb1 and VHBc1 when voltage feedback loop is activated with $V_{DC\_ref}$ =20048          |

| Figure 14. Steady state waveforms of grid current $I_a$ and hybrid multilevel output $V_{u0}$ with $V_{DC\_} ref = 165$                                      |

| Figure 15. Steady state waveforms of grid current $I_a$ and hybrid multilevel output $V_{u0}$ with $V_{DC\_}ref=180$                                         |

| Figure 16. Steady state waveforms of grid current $I_a$ and hybrid multilevel output $V_{u0}$ with $V_{DC\_}$ ref=20050                                      |

| PAPER III                                                                                                                                                    |

| Figure 1. Hybrid multilevel rectifier consisting of the NPC and the CHBs56                                                                                   |

| Figure 2. Experimental results explaining hybrid modulation method56                                                                                         |

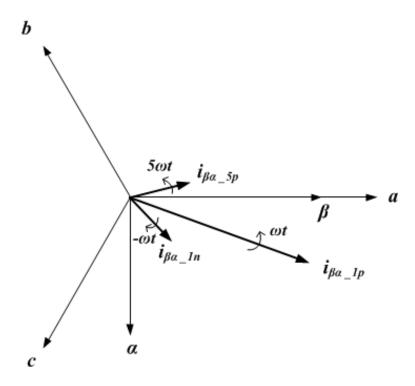

| Figure 3. Grid current vectors and axes of the multiple reference frame58                                                                                    |

| Figure 4. Extraction and conversion of 5th harmonic                                                                                                          |

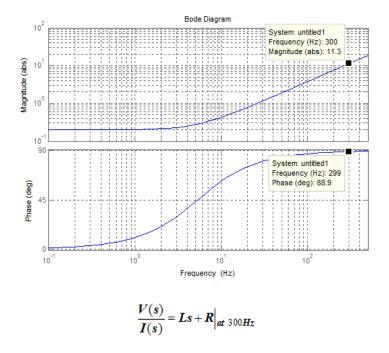

| Figure 5. Magnitude and phase at 5th harmonic frequency on the bode plot60                                                                                   |

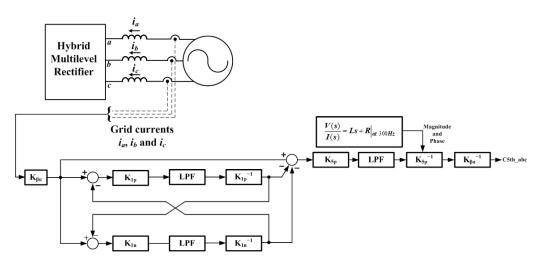

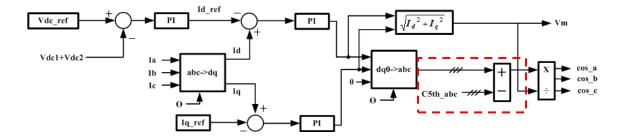

| Figure 6. Voltage reference compensation in the feedback loop61                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------|

| Figure 7. Grid voltage source waveforms that are used in simulation                                                             |

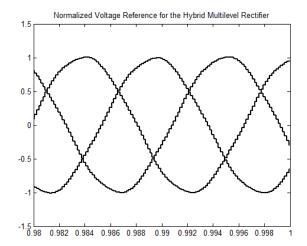

| Figure 8. Normalized voltage reference for the hybrid multilevel rectifier after voltage reference compensation                 |

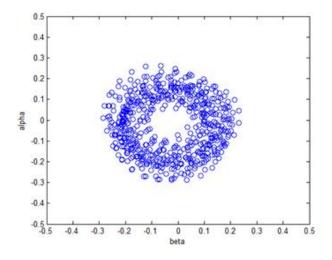

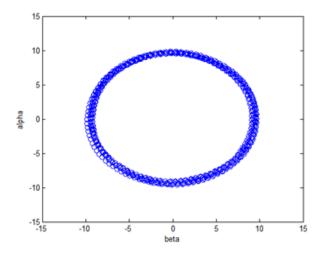

| Figure 9. 5th grid current harmonic on βα plane after applying MRF63                                                            |

| Figure 10. Grid current at fundamental frequency on βα plane after applying MRF63                                               |

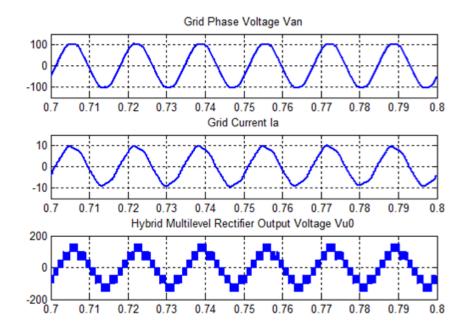

| Figure 11. Simulation results representing $V_{an}$ , $I_a$ and $V_{u0}$ before grid current compensation                       |

| Figure 12. Simulation results representing V <sub>an</sub> , I <sub>a</sub> and V <sub>u0</sub> after grid current compensation |

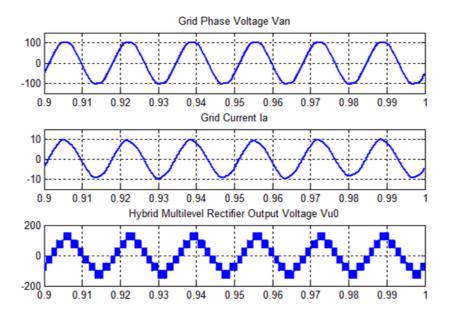

| Figure 13. Experimental result without compensating the grid currents66                                                         |

| Figure 14. Experimental result after compensating the 5th harmonic67                                                            |

# LIST OF TABLES

|          | Page                                                            |

|----------|-----------------------------------------------------------------|

| PAPER I  |                                                                 |

| Table 1. | Three Level of Output Voltage According to Switch State         |

| PAPER II |                                                                 |

| Table 1. | Operation Modes for Starting up the Hybrid Multilevel Rectifier |

### 1. INTRODUCTION

Because of technical limitations on producing high-voltage semiconductor devices with fast switching capabilities, multilevel topologies using low switching frequency schemes have been accepted as the dominant approach in high power applications. However, output current distortion and physically heavy filters have been continuously reported as serious problems associated with these converters. Keeping the pace with the progress in producing semiconductor devices with medium voltage ratings and fast switching characteristics, various high frequency switching schemes for multilevel power conversion systems have been suggested in order to satisfy total harmonic distortion (THD) regulations on grid currents and to reduce overall weight of the system in high power multilevel applications [1]–[3].

## 1.1. APPLICATIONS

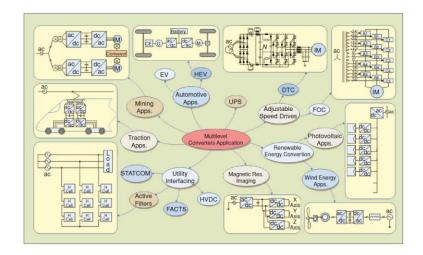

Renewable energy sources have been considered as alternative resources for electric power generation. Well-known two-level converters achieve good performance in medium power applications for providing power from the renewable source to utility grid or electric motors. On the other hand, in high power application in which switches should handle high voltage and the power circuit should produce low total harmonic distortion (THD) of grid currents, multilevel power converter topologies are more attractive. Figure 1.1. that is captured from [4] shows multilevel converters application. Multilevel converters can be used in utility interfacing applications because its multilevel output

voltages help improve THD of grid currents in applications such as static synchronous compensators (STATCOM), Active Filters and flexible alternating current transmission

Figure 1.1. Multilevel converter application overview

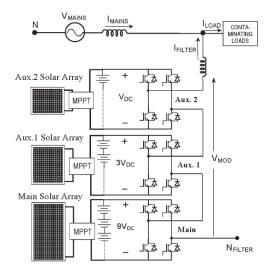

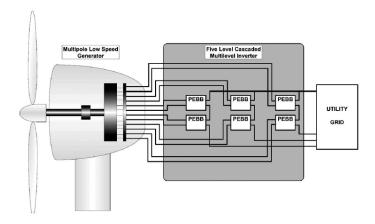

systems (FACTS). Electric locomotive uses high voltage to provide high power to AC motors. Therefore, recently multilevel converters have been applied instead of using low frequency switching scheme with semiconductor switches like Thyristors. In PV application, multiple numbers of panels will be placed in arrays. Then each panel will have power converters to provide power to the utility grid in a way depicted in Figure 1.2. [5]. With this application, multilevel power conversion topologies will be more useful to combine all the electric energy and to provide it to the utility. The low-speed permanent-magnet generator is designed to have a large number of poles with multiple wounds as depicted in Figure 1.3. [6]. In this case, the power-electronic building block (PEBB) can be placed between the grid and the wind turbine. Increasing the nominal power of wind-

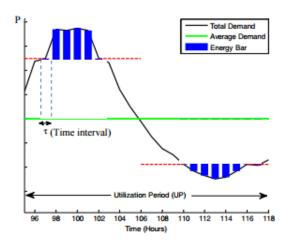

turbines is the current trend on the market. This makes the multilevel converter suitable for modern high-power wind-turbine applications. Recently along with the smart grid system in which the price of electricity is determined based on supply and demand in real time, energy storage system (ESS) has been gaining attention in peak-shaving application. Thus, electrical power will be stored in batteries at night time from the grid when the price of electricity is low because the overall demand is low. Then, the electrical energy stored in the battery can be used at daytime when the price of electricity is high. Therefore, factories or large buildings that consume large electricity everyday might prefer to equip with the ESS to save cost on electricity in long term. In the perspective of the electrical power provider, the ESS can be helpful to increase power security by doing peak-shaving and valley-filling [7] as described in Figure 1.4. In these high power applications, multilevel power conversion system will offer practical solutions.

Figure 1.2. Multilevel converter in PV application

Figure 1.3. Five-level cascaded multilevel converter connected to a multiple pole low-speed wind-turbine generator

Figure 1.4. Peak shaving and valley filling

# 1.2. MULTILEVEL CONVERTER TOPOLOGIES

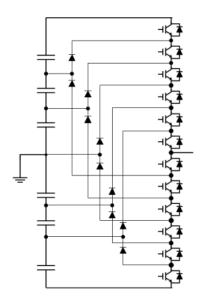

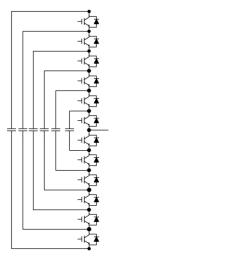

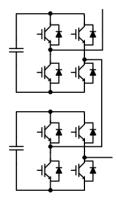

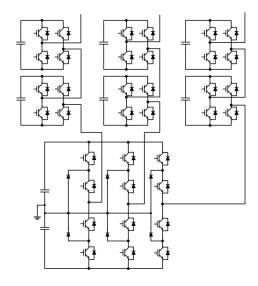

Multilevel topologies can be largely categorized into neutral point clamped (NPC or diode clamped) [8]–[11] as described in Figure 1.5., flying capacitors (capacitor clamped) [12]–[16] shown in Figure 1.6., cascaded H-bridges (CHB) [18]–[19] depicted

in Figure 1.7., and hybrid [20], [21] as represented in Figure 1.8. Recently, hybrid topologies have been suggested to combine an NPC and cascaded H-bridges in series.

Figure 1.5. Neutral point clamped multilevel topology

Figure 1.7. Cascaded H-bridge multilevel topology

Figure 1.8. Hybrid multilevel topology

### 1.3. MODULATION METHODS FOR MULTILEVEL CONVERTERS

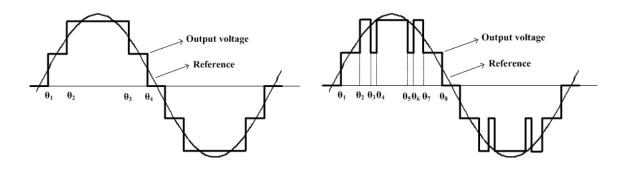

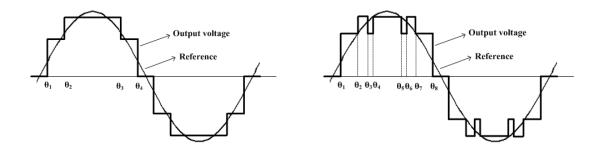

Various modulation methods have been suggested and developed including selective harmonic elimination [22]–[26], selective harmonic elimination pulse width modulation (PWM) [27]–[32], asymmetric modulation [33], asymmetric PWM [34], subharmonic elimination PWM [35]–[37], and hybrid modulation [38]–[40]. The selective harmonic elimination as shown in Figure 1.9. is called stepped waveform modulation. Main and series cells are operating with stacked square waveforms in a way that a group of switching angles of  $\theta$  according to a reference eliminates a specific low harmonic. Therefore, it usually has a look-up table formed by calculation with a Fourier series equation in advance of an experiment. In Figure 1.10., selective harmonic elimination PWM is a similar method but it chops down a square waveform several times so that it removes several low harmonics. Asymmetric modulation in Figure 1.11. and asymmetric modulation PWM in Figure 1.12. are similar methods except that the strategy to make

voltages in each cell is different. The methods described in Figure 1.9.-1.12. are all based on low switching frequency. Sub-harmonic elimination modulation uses high switching frequency so that an output voltage of a multilevel inverter has no low frequency harmonics except switching frequency harmonics.

Figure 1.9. Selective harmonic elimination Figure 1.10. Selective harmonic elimination method

PWM method

Figure 1.12. Asymmetric PWM method Figure 1.11. Asymmetric modulation method

### 1.4. NEW VOLTAGE BALANCING METHOD FOR NPC

In paper I, the three phase NPC topology is used in a grid connected rectifier. In the three-level NPC topology, there are two dc link capacitors which equally split the dc voltage. The two dc link capacitors are charged by the grid current coming from the grid. Therefore, with distorted grid currents, the NPC topology may suffer from capacitor voltage differences since the average neutral current flowing into and out of the neutral point of the dc link may not be zero, especially, during transients. The proposed voltage balancing method separates one sinusoidal reference into upper and lower references. Then, the upper and lower references are shifted to opposite directions. By charging the two NPC capacitors with different amount of grid currents, it balances them effectively. Simulation and experimental results verify the proposed voltage balancing method.

### 1.5. PRE-CHARGE ROUTINE FOR HYBRID MULTILEVEL RECTIFIER

In the paper II, a three phase hybrid multilevel topology is employed to provide power from the grid to the resistive load. The hybrid multilevel topology has an NPC and CHBs which are modulated with a hybrid modulation method. Selective harmonic elimination method will modulate the NPC with 60Hz switching frequency. Then semiconductor devices of CHBs will be switched with high switching frequencies. Since the hybrid multilevel rectifier has many capacitors that are completely discharged at the beginning of the operation, large inrush currents will come from the grid at start-up. Therefore, this paper proposes a start-up routine for the hybrid multilevel rectifier to be landed safely on a steady state condition. Along with the start-up procedure, this paper

also considers the three main goals in a grid connected rectifier application: 1) unity power factor control (PFC), 2) load voltage regulation and 3) capacitor voltage regulation of CHBs which are connected in series with the NPC. Control block diagrams and phasor diagrams explain not only the pre-charge routine but also control methods for the three main goals with details. Simulation and experimental results show the verification of the proposed method.

## 1.6. GRID CURRENT HARMONIC COMPENSATION BY USING MRF

Grid current harmonic compensation by using MRF for the hybrid multilevel rectifier is discussed in the paper III. In a practical application of grid connected power converters, grid voltage sources are a little bit distorted for various reasons. Thus with distorted grid voltage sources, grid connected rectifier might draw distorted grid currents from the grid to the converter. Therefore, this paper suggests a method for compensating the 5th harmonic of grid currents by using multiple reference frame theory for the hybrid multilevel rectifier. The grid currents resulted by the rectifier are analyzed with the multiple reference frame theory to extract only 5th harmonic. Then, magnitude and phase value at 5th harmonic frequency in a Bode plot will be used to convert the calculated 5th harmonic to the voltage references which modulate the hybrid multilevel rectifier. The feedback control loop for accomplishing load voltage control and unity PFC is explained with block diagrams. Simulations and experimental results show the verification of the suggested method.

#### **PAPER**

# I. PHASE-SHIFTING REFERENCE STRATEGY FOR VOLTAGE BALANCING IN NEUTRAL-POINT CLAMPED CONVERTER

Abstract— This paper suggests a new method to balance two capacitor voltages in the three-level neutral-point clamped (NPC) converter. Usually, a carrier-based PWM method using a sinusoidal reference and two carriers is employed to run a three-level NPC converter. In this paper, the single reference is separated into upper and lower references. By creating a slight phase shift between these two references, the proposed method is able to balance two NPC capacitor voltages. In most conventional approaches, capacitor charging time is controlled in a way of manipulating pulse width in NPC output voltages. However, in the proposed method, capacitor charge/discharge is achieved by moving the upper and lower portions of the NPC output voltage toward/away from the grid peak current. The new voltage balancing technique is compared with the existing traditional methods and verified by simulation and experimental results.

## I. INTRODUCTION

In high power applications, it is difficult to use two-level converters because of the limited voltage rating on IGBTs or MOSFETs. Therefore, multilevel converters have been considered as an alternative topology in such applications [1]. Neutral point clamped (NPC) and cascaded H-bridge (CHB) converters are preferred to flying capacitor (FC) topologies as there is a difficulty in balancing flying capacitor voltages [2].

Also, in a three phase rectifier application, CHB needs isolated DC/DC converters to create each floating voltage that feeds the H-bridges. This is more expensive and bulky. On the other hand, in the three-level NPC topology, there are two dc link capacitors which equally split the dc voltage. The NPC topology may suffer from capacitor voltage differences. NPC converters have inherent unbalanced capacitor voltage problems since the average neutral current flowing into and out of the neutral point of the dc link may not be zero, especially, during transients [3], [4]. Also, distorted ac currents (linear imbalance) and a nonlinear load can cause voltage imbalance on the NPC inverter in motor drive application [31]. In addition, aging parameter variations and temperature may cause a drift in the value of the capacitors. Unequal values for capacitors will aggravate the voltage imbalance issue. As a result, many literatures have suggested methods to resolve this problem.

One of the suggested methods is to place additional circuits between dc link capacitors and the load [5]–[8]. With this method, the control strategy for the NPC is simple and easy to implement. However, it requires additional semiconductor switches and inductors. Therefore, it increases the overall costs and power losses. Another suggested method is to use the SVPWM (space vector pulse width modulation) strategy [9]–[16]. With SVPWM, one can use redundant switch states in order to make the average neutral current zero. So the SVPWM strategy allows balancing the two capacitor voltages effectively. However, this method requires some time to analyze every switching situation. Only after rigorous analysis on every switching state, one can apply SVPWM on balancing the two capacitor voltages. Also, many methods have been recommended based on SPWM (sinusoidal PWM) [17]–[24]. Although each method is

processed based on difference information, conceptual approach is same. There, voltage balancing is accomplished by injecting offset signal to a reference signal. Additionally, a different concept called multicarrier PWM strategy has been suggested [25]–[27]. There, triangular carriers are changed in ways of level-shifted carrier PWM or phase-shifted carrier PWM. In [26], the amplitudes of the triangular carriers are variable through a feed–forward compensation loop but the carriers have fixed phase differences. On the other hand, the phase difference between carriers will be determined by a pre-calculation while they have fixed peak amplitude [25], [27]. The common strategy of the offset injection method and the feed–forward compensated multicarrier PWM is to control the charging time of the target capacitors based on the severity of voltage imbalance. In these cases, the voltage unbalance problem is resolved by generating narrower or wider pulses depending on how the voltages are unbalanced.

In a situation operating near over-modulation region with the two conventional methods, a system might experience over-modulation because they manipulate pulse width by adding an offset to a reference or changing the magnitude of carriers. Rather than changing the width of the PWM pulses, the phase-shifting reference (PSR) method overcomes the voltage unbalance problem by moving the PWM pulses toward or away from the peak of grid currents. So it can naturally avoid over-modulation. Also, THD of the grid current gets slightly better since the balanced voltage by the proposed method increased the magnitude of the NPC output voltage at fundamental frequency.

The remainder of this paper is organized as follows. Section II explains why two reference signals are necessary to balance two capacitor voltages in the NPC. Then, simple simulation results describe a strategy of the PSR method in section III. Then

section IV explains an overlap and gap period which occurs in the PSR method. Section V shows a feedback control block diagram which output adjusts phase angle of two reference signals. In section V, experiment and simulation setting is explained and listed with details. It contains pictures and block diagrams which indicates the whole procedure of the experiment. Then waveforms from simulation and experiments prove the validity of the PSR method.

# II. SWITCHING SCHEME AND TWO REFERENCE SIGNALS OF THE NPC TOPOLOGY

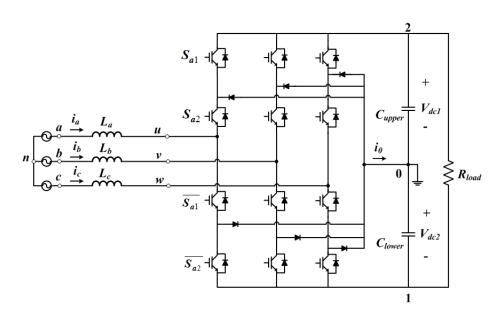

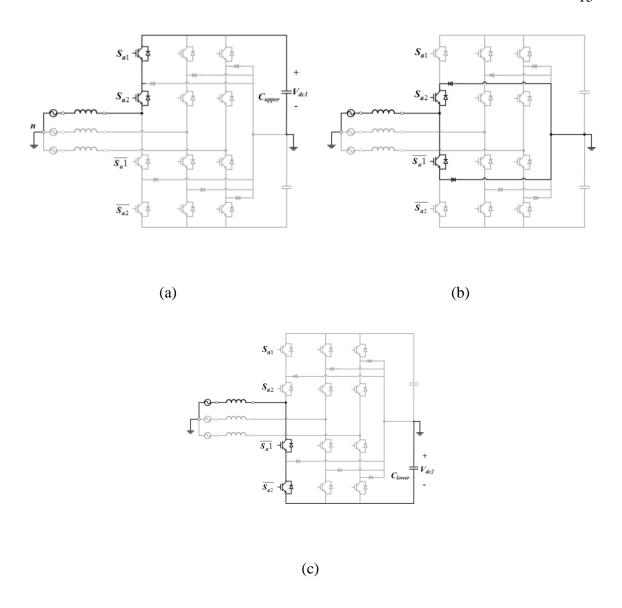

Figure 1. shows a three-phase neutral-point clamped AC/DC rectifier that is used in this paper.  $S_{a1}$ ,  $\overline{S_{a1}}$  and  $S_{a2}$ ,  $\overline{S_{a2}}$  are switch pairs in phase A. Table 1. demonstrates the relationship between the switch states and output voltage  $V_{u0}$ . If switches  $\{S_{a1}, S_{a2}, \overline{S_{a1}}, \overline{S_{a2}}\}$  are  $\{On\ On\ Off\ Off\}$ , then node u will be connected to node 2. In this case,  $V_{u0}$  would equal to  $V_{dc1}$ . The circuit of this switch state is described as mode (a) in Figure 2-(a). In mode (b) described in Figure 2-(b).,  $V_{u0}$  becomes 0. Similarly, the output voltage  $V_{u0}$  voltage would be  $-V_{dc2}$  in the event of  $\{Off\ Off\ On\ On\}$  for switches  $\{S_{a1}, S_{a2}, \overline{S_{a1}}, \overline{S_{a2}}\}$  which relates to mode (c) of Figure 2-(c). With the assumption that  $V_{dc1}$  and  $V_{dc2}$  are constant, the switching scheme can be explained easily using Figure 3. There are upper and lower reference signals that are compared with carriers. Then on-off status of switches  $\{S_{a1}, S_{a1}, \overline{S_{a1}}, \overline{S_{a1}}, \overline{S_{a1}}\}$  are determined by

$$\begin{split} &\text{if $V_{upper\_r} > V_{upper\_tri}$} & \text{then $S_{a1}$, $\overline{S_{a1}}$} \Rightarrow \{On \ Off\}, \\ &V_{upper\_r} < V_{upper\_tri}$ & \text{then $S_{a1}$, $\overline{S_{a1}}$} \Rightarrow \{Off \ On\}, \\ &\text{if $V_{lower\_r} > V_{lower\_tri}$} & \text{then $S_{a2}$, $\overline{S_{a2}}$} \Rightarrow \{On \ Off\}, \\ &V_{lower\_r} < V_{lower\_tri}$ & \text{then $S_{a2}$, $\overline{S_{a2}}$} \Rightarrow \{Off \ On\} \end{split}$$

Figure 1. Three-phase neutral-point clamped AC/DC rectifier

Table 1. Three Level of Output Voltage According to Switch State

| Switch State { $S_{a1}$ , $S_{a2}$ , $\overline{S_{a1}}$ , $\overline{S_{a2}}$ } | Output V <sub>u0</sub> | Connection | Mode |

|----------------------------------------------------------------------------------|------------------------|------------|------|

| {On On Off Off}                                                                  | $V_{dc1}$              | 2          | (a)  |

| {Off On On Off}                                                                  | 0                      | 0          | (b)  |

| {Off Off On On}                                                                  | $-V_{dc2}$             | 1          | (c)  |

Figure 2. Three modes of switching in a case of phase A : (a) when  $\{S_{a1}, S_{a2}, \overline{S_{a1}}, \overline{S_{a2}}\}$  are  $\{\text{On On Off Off}\}$ , (b) when  $\{S_{a1}, S_{a2}, \overline{S_{a1}}, \overline{S_{a2}}\}$  are  $\{\text{Off On On Off}\}$ , (c) when  $\{S_{a1}, S_{a2}, \overline{S_{a1}}, \overline{S_{a2}}\}$  are  $\{\text{Off Off On On}\}$

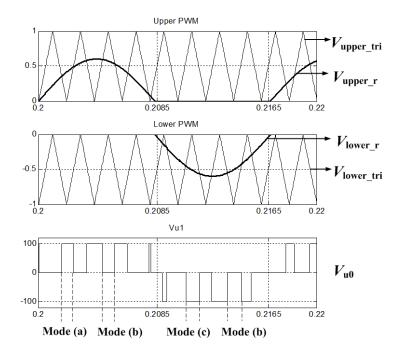

Figure 3. also shows a typical output voltage  $V_{u0}$  which has 3 levels. It can be seen that mode (a) and (b) are alternating during the first half cycle, which is related to the upper capacitor voltage  $V_{dc1}$ . As a result, if modes (a) and (b) are managed during the first half cycle,  $V_{dc0}$  can be controlled. Similarly, one can control  $V_{dc2}$  by managing

modes (b) and (c) during the second half of the cycle. Therefore, two separate reference signals are needed to balance both capacitor voltages.

Figure 3. Two reference signals and the output  $V_{u0}$

## III. PHASE-SHIFTING REFERENCE STRATEGY

Figure 4. describes the PSR strategy for balancing the two NPC capacitor voltages. The solid sinusoidal waveforms are the original reference signals while the dotted waveforms are phase-shifted reference signals. With the proposed PSR strategy, the upper and lower references move to the right or the left based on the *phase\_compensation* value by using (2) and (3). The *phase\_compensation* value is an outcome of a closed loop, which is explained with block diagrams and codes in section V.

$$upper\_m_a = m \times \cos(\theta) \qquad \mp phase\_compensation)$$

$$upper\_m_b = m \times \cos(\theta - \frac{2}{3}\pi \ \mp phase\_compensation)$$

$$upper\_m_c = m \times \cos(\theta + \frac{2}{3}\pi \ \mp phase\_compensation)$$

(2)

$$lower _m_a = m \times cos(\theta \pm phase\_compensation)$$

$$lower _m_b = m \times cos(\theta - \frac{2}{3}\pi \pm phase\_compensation)$$

$$lower _m_c = m \times cos(\theta + \frac{2}{3}\pi \pm phase\_compensation)$$

(3)

Figure 4. PSR strategy with upper and lower reference signals

The plus and minus signs in front of *phase\_compensation* in (2) and (3) can be changed according to inverter or rectifier application. To show the concept of controlling target voltages using the proposed method, a simulation is carried out using only one phase of the NPC rectifier. The simulation circuit has an ideal current source  $i_a$  replacing the inductor for the purpose of removing the effect of the distorted grid current on the two capacitor voltages. Also, the switching frequency is chosen to be 500 Hz for the simulation to show better graphical PWM action. As a starting point before applying any

voltage balancing method, simulation conditions are intentionally selected for  $V_{dc1}$  and  $V_{dc2}$  to have the same average value in Figure 5.

After applying +0.2/-0.2 rad. (11.5°) of *phase\_compensation*, the upper reference signal moves toward/away from the upper peak of the grid current  $I_a$  while the lower reference signal is shifted away from / toward the bottom peak of the grid current  $I_a$  as shown in Figure 6. / Figure 7. It is worth mentioning that the angle 0.2 rad. is much larger than practical cases. Since the charging current delivered to the  $C_{upper}/C_{lower}$  has been increased/ decreased,  $V_{dc1}$  goes higher than  $V_{dc2}$  as depicted in Figure 6. This explanation also applies on the result in Figure 7. Since the PSR method shifts the two references to right or left, not up or down, it can naturally avoid over-modulation. Over-modulation can degrade grid current THD [30].

Figure 5. Simulation result when applying no voltage balancing method

Figure 6. Two capacitor voltages when applying +0.2 rad. (+11.5  $^{\circ}$ ) as phase\_compensation on (2) and (3)

Figure 7. Two capacitor voltages when applying -0.2 rad.  $(-11.5^{\circ})$  as *phase\_compensation* on (2) and (3)

# IV. OVERLAP PERIOD HAPPENING IN PHASE-SHIFTING REFERENCE

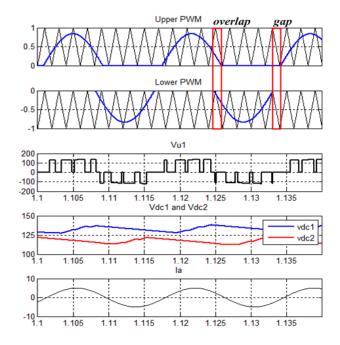

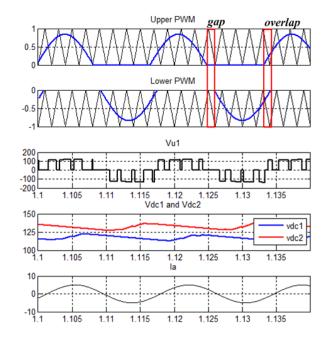

As the upper and lower references shift to right or left, an overlap and a gap period will be occurred as shown in red rectangles in Figures 6.-7. In order to show switch state during the overlap period, a simple simulation is conducted with the same conditions except an actual switching frequency of 6 kHz. Figure 8. shows the switch state transition during the overlap period that is indicated in the red rectangle in Figure 7.

Normally, as described in Figures 3.-4., switching mode alternates between two modes. However, during the overlap period, switch mode will be changing between three modes. When the *phase\_compensation* value becomes -0.7 rad.  $(-40^{\circ})$  for an impractical case as presented in Figure 9., switch state should transit from mode (a) to mode (c) instantly. Therefore, an arm short hazard may occur because it requires all of the four switches to turn on or off simultaneously. As long as the *phase\_compensation* value is within  $\pm 0.53$  rad.  $(\pm 30^{\circ})$  as a worst case when the peak reference is 1, the system will be safe from the hazard. In order to avoid extreme cases, the *phase\_compensation* value is limited within  $\pm 0.06$  rad.  $(3.44^{\circ})$  in the DSP code. In a practical case during a steady state, the *phase\_compensation* is usually smaller than 0.01 rad.  $(0.57^{\circ})$ . Therefore, the gap and overlap period do not persist for a long time.

Figure 8. Overlap period when applying -0.2 rad.  $(-11.5^{\circ})$  as *phase\_compensation* on (2) and (3)

Figure 9. An impractical case of the overlap period with -0.7 rad.  $(-40^{\circ})$  of the *phase\_compensation*.

## V. PHASE COMPENSATION CONTROL LOOP

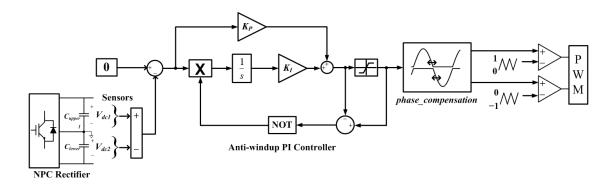

Figure 10. shows the feedback control loop in which *phase\_compensation* is generated. For balancing  $V_{dc1}$  and  $V_{dc2}$  equally, the reference of the control loop is zero. Voltage difference between  $V_{dc1}$  and  $V_{dc2}$  is fed back to the loop. In the feedback loop an anti-windup PI controller is adopted, which can achieve lower overshoot response during transients. However, the anti-windup PI controller degrades the settling time. Generally, the voltage unba lance has a slow time response compared to other voltage and current control loops in the system. Among many types of anti-windup PI controllers, the anti-windup PI conditioned is a good alternative to reduce the overshoot [28], [29]. In Figure 10., the output of the anti-windup PI controller is limited by a certain value  $(\pm 0.01 \times 2\pi)$ .

Figure 10. Feedback control block diagram for PSR strategy

When the limitation occurs, the input of the integrator becomes zero, but the previous value of the integrator in the digital PI controller will be held. Otherwise, the anti-windup PI controller will show same characteristics with a conventional PI controller.

Referring to the design of the anti-windup controller,  $K_P$  and  $K_I$  should be small enough so that a system can reduce overshoot of *phase\_compensation* during transients. Thus in this paper,  $K_P$  and  $K_I$  are selected as 0.001 and 1, respectively. Since this topology is a rectifier, the plus-minus signs in (2) and (3) are selected as a minus in (2) and a plus in (3). The *phase\_compensation* shifts the upper and lower references in an opposite direction. Then they are compared with each triangular carrier.

# VI. SIMULATION AND EXPERIMENTAL RESULTS

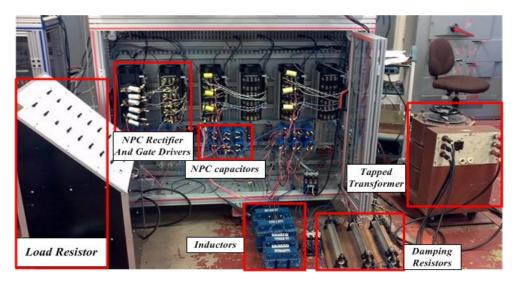

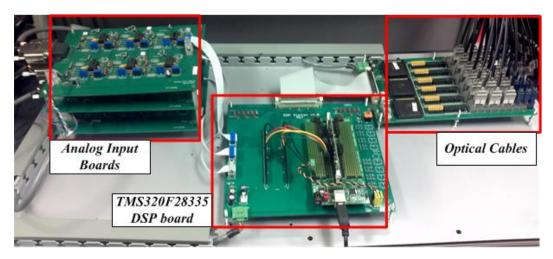

The specifications of the simulation model as well as the hardware setup are as follows: phase voltage  $V_{grid\_peak} = 100$  V, grid frequency=60 Hz, switching frequency = 6 kHz, L = 6 mH,  $C_{upper} = 7.8$  mF,  $C_{lower} = 11.7$  mF for experimental set,  $C_{upper} = 800$  µF,  $C_{lower} = 1$  mF for MATALB/Simulink simulation,  $R_{load} \approx 90$   $\Omega$ . In order to make the simulation fast, upper and lower capacitances are decreased. Figure 11. displays an overview of the experimental setup and the control block diagram. The sampling and switching frequencies are the same. The PLL block is designed based on a synchronous reference frame [32] and forms a closed loop control which will detect the angle of the grid phase voltage  $V_{an}$ . The DSP board has a push button so that a signal from 'Star/Stop' can trigger or stop the suggested method in the DSP. The experimental setup uses damping resistors ( $R_{damping} \approx 15 \Omega$ ) for reducing the inrush current from the grid at startup. After the capacitors are charged at a certain level, the damping resistors are removed by using magnetic switches. There are pictures displaying NPC rectifier prototype for the test in Figures 12. and 13. The white colored capacitors in the NPC rectifier are film

capacitors placed in parallel with the electrolytic capacitors. They filter noise and reduce stray inductance. For safety reasons, a tapped transformer provides magnetic isolation between the set and the grid. The voltage information measured by LV 25-P is transferred to the AIB board described in Figure 13. Then the DSP generates the PWM signals that are transformed to optic signals and consequently sent to the gate driver boards.

Figure 11. Experimental set configuration and control block diagram

Figure 12. Experimental set configuration

Figure 13. TMS320F28335 DSP, analog input board (AIB) and optical signal transmission board

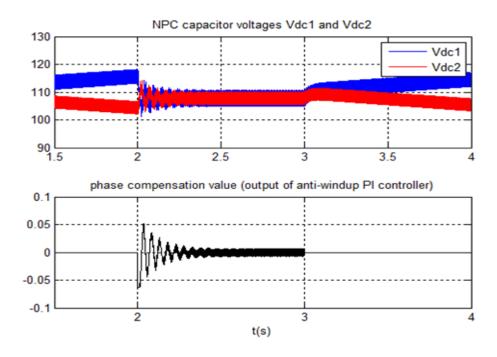

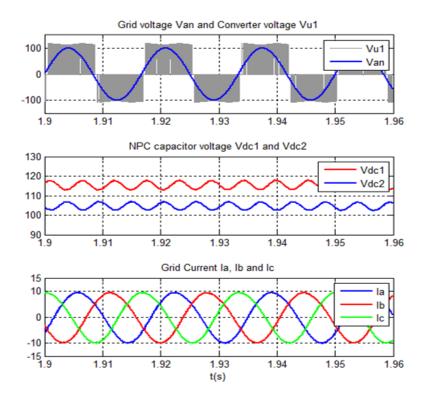

Figure 14. shows the transient response of the two capacitor voltages and the *phase\_compensation* value in simulation. From time 1.5s to 2s, the voltage balancing method is not applied. After time 2s, the PSR method is activated. Two capacitor voltages are well balanced with zero steady state error in the simulation. Again, the PSR

method is deactivated at 3 s. It looks like the two voltages are diverging unboundedly. However, it will be actually saturated at some point. The waveform in Figure 15. is the *phase\_compensation* value during the steady state. The sinusoidal waveform has 180 Hz which is same with oscillation frequency of the two capacitor voltages. Figures 16. and 17. describe steady state waveforms with and without the PSR method in the simulation.

Figure 14. Transient response of the two capacitor voltages and *phase\_compensation* value

Figure 15. *Phase\_compensation* value of (2) and (3) in a steady state in Figure 14. from 2.7 sec to 2.75 sec

Figure 16. Simulation result in a steady state without a voltage balancing method

Figure 17. Simulation result in a steady state using the PSR method

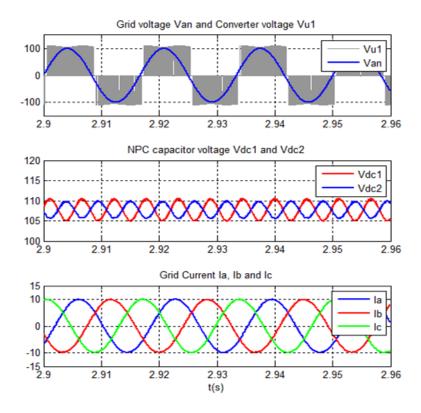

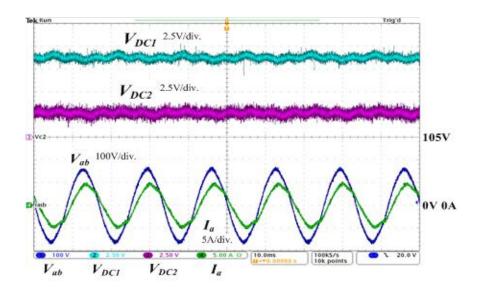

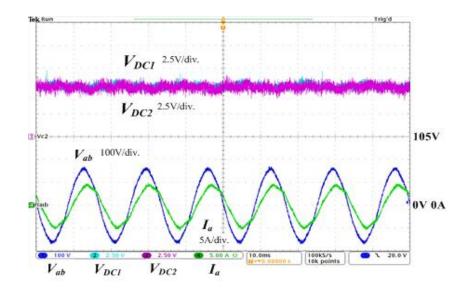

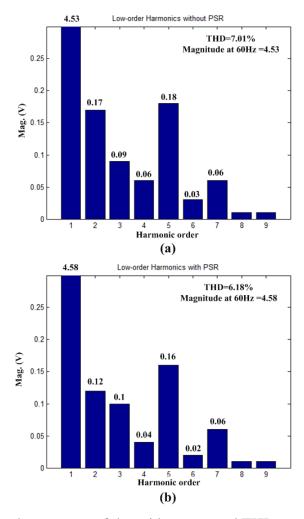

Figure 18. depicts the steady state waveforms showing upper and lower capacitor voltages  $V_{dc1}$  and  $V_{dc2}$ , line—line grid voltage  $V_{ab}$  and the grid current  $I_a$ . The upper capacitor voltage is 114 V and the lower capacitor voltage is 107 V. So the voltage difference is approximately 7 V during the steady state without any voltage balancing technique. After applying the PSR method, the two capacitor voltages become 110.5 V as shown in Figure 19. The grid current waveforms in Figure 18. and Figure 19. look same. In order to figure out the difference between the two current waveforms precisely, Fast Fourier Transform (FFT) needs to be applied. Fig 21 shows the result after applying FFT

on the two currents in Figure 18. and Figure 19. THD of the grid current has been improved a little with the suggested PSR method because the fundamental magnitude of

Figure 18. Experimental results in a steady state without a voltage balancing method

Figure 19. Experimental results in a steady state using the PSR method

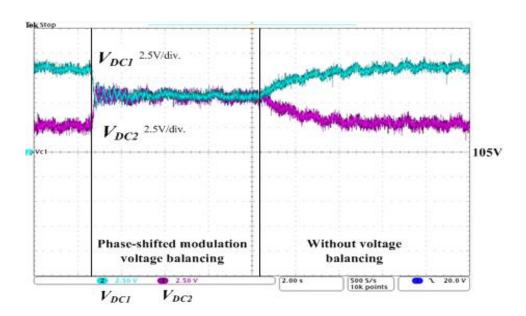

the grid current becomes slightly larger from 4.53 to 4.58 and overall harmonics are reduced a little. The equally balanced capacitor voltages improved the output PWM voltage, which lead to make the fundamental output grid current a little larger. The transient response can be found in Figure 20. with 2 sec/div on the time axis. The DSP board has an external button to give a trigger signal to the DSP chip. When the button is pushed, the voltage balancing method will be activated. As described in the Figure 20., the close loop using PSR method produces low overshoot during transients and zero steady state error as similar with simulation results described in Figure 14.

Figure 20. Transient response of the two capacitor voltages

Figure 21. Magnitude spectrum of the grid current and THD comparison (a) using the grid current  $I_a$  in Figure 18., (b) using the grid current  $I_a$  in Figure 19.

# VII. CONCLUSION

Having conceptually different approach from the offset injection method and a feed-forward compensated multicarrier PWM for balancing voltages in a NPC, this paper suggests the phase-shifting reference (PSR) method to balance capacitor voltages. With the PSR method, a system balances target voltages by moving the upper and lower reference in an opposite way. Eventually the compensated NPC output pulses charge the

two capacitors with different amount of grid currents. On the other hand, the conventional methods control charging time by injecting offsets. Also, the PSR method does not require to develop a model or to calculate rigorous equations. The controller design using the PSR is simple and straightforward. Over—modulation situation can be naturally prevented since it moves the upper and lower references to right or left. Also, switch states and a possible hazard during the overlap period are analyzed and explained. The transient response on the two capacitors shows stable transition and less overshoot with zero steady state error. The THD comparison brings a conclusion that the proposed method can effect slightly on the grid current THD. Therefore, the PSR method for 3-level NPC is verified with experimental and simulation results.

### **REFERENCES**

- [1] J. Rodriguez, J.S. Lai, F.Z. Peng, "Multilevel inverters: a survey of topologies, controls and applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 724–738, Aug. 2002.

- [2] S. Kouro, M. Malinowski, K. Gopakumar, L. G. Franquelo, J. Pou, J. Rodriguez, B. Wu, M. A. Perez and J. I. Leon, "Recent Advances and Industrial Applications of Multilevel Converters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, Aug. 2010.

- [3] S. Ogasawara and H. Akagi, "Analysis of variation of neutral point potential in neutral-point-clamped voltage source PWM inverters," in *Proc. IAS Annu. Meeting*, 1993, pp. 965–970.

- [4] J. Rodriguez, S. Bernet, P. K. Steimer, and I. E. Lizama, "A survey on neutral-point-clamped inverters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2219–2230, Jul. 2010.

- [5] K. Hasegawa and H. Akagi, "A new dc-voltage-balancing circuit including a single coupled inductor for a five-level diode-clamped PWM inverter," *IEEE Trans. Ind. Appl.*, vol. 47, no. 2, pp. 841–852, Mar./Apr. 2011.

- [6] S. Busquets-Monge, S. Alepuz, J. Bordonau and J. Peracaula, "Voltage Balancing Control of Diode-Clamped Multilevel Converters With Passive Front-Ends," *IEEE Trans. Power Electron.*, vol. 23, no. 4, pp. 1751–1758, Jul. 2008.

- [7] A. von Jouanne, D. Shaoan and Z. Haoran, "A multilevel inverter approach providing DC-link balancing, ride-through enhancement, and common-mode voltage elimination," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 739–745, Aug. 2002.

- [8] R. Stala, "A natural DC-link voltage balancing of diode-clamped inverters in parallel systems," *IEEE Trans. Ind. Electron.*, vol. 60, no. 11, pp. 5008–5018, Nov. 2013.

- [9] J.I. Leon, S. Vazquez, R. Portillo, L.G. Franquelo, J.M. Carrasco, P.W. Wheeler and A.J. Watson, "Three-Dimensional Feedforward Space Vector Modulation Applied to Multilevel Diode-Clamped Converters," *IEEE Trans. Ind. Electron.*, vol. 56, no. 1, pp. 101–109, Jan. 2009.

- [10] J. Pou, R. Pindado, D. Boroyevich and P. Rodriguez, "Evaluation of the low-frequency neutral-point voltage oscillations in the three-level inverter," *IEEE Trans.*, *Ind. Electron.*, vol. 52, no. 6, pp. 1582–1588, Dec. 2005.

- [11] J. Pou, D. Boroyevich and R. Pindado, "New feedforward space-vector PWM method to obtain balanced AC output voltages in a three-level neutral-point-clamped converter," *IEEE Trans., Ind. Electron.*, vol. 49, no. 5, pp. 1026–1034, Oct. 2002.

- [12] Y. Jiao, F.C. Lee and S. Lu, "Space Vector Modulation for Three-Level NPC Converter With Neutral Point Voltage Balance and Switching Loss Reduction," *IEEE Trans. Power Electron.*, vol. 29, no. 10, pp. 5579–5591, Oct. 2014.

- [13] N.M.R. Santos, J.F. Silva, J. Verveckken, V.M.F. Pires and R.M.G. Castro, "Enhancing the Ride-Through Capability of DC-Link Voltage in NPC Multilevel Unified Power–Flow Controllers," *IEEE Trans. Power Del.*, vol. 29, no. 4, pp. 1542–1550, Aug. 2014.

- [14] S. Busquets-Monge, S. Somavilla, J. Bordonau, D. Boroyevich, "Capacitor Voltage Balance for the Neutral Point Clamped Converter using the Virtual Space Vector Concept With Optimized Spectral Performance," *IEEE Trans., Power Electron.*, vol. 22, no. 4, pp. 1128–1135, Jul. 2007

- [15] H. Zhang, S.J. Finney, A. Massoud, B.W. Williams, "An SVM Algorithm to Balance the Capacitor Voltages of the Three-Level NPC Active Power Filter," *IEEE Trans. Power Electrons.*, vol. 23, no. 6, pp. 2694–2702, Nov. 2008

- [16] G.I. Orfanoudakis, M.A. Yuratich, S.M. Sharkh, "Nearest-Vector Modulation Strategies With Minimum Amplitude of Low-Frequency Neutral-Point Voltage Oscillations for the Neutral-Point-Clamped Converter," *IEEE Trans. Power Electron.*, vol. 28, no. 10, pp. 4485–4499, Oct. 2013.

- [17] J. Pou, J. Zaragoza, P. Rodriguez, S. Ceballos, V.M. Sala, R.P. Burgos and D. Boroyevich, "Fast-Processing Modulation Strategy for the Neutral-Point-Clamped Converter With Total Elimination of Low-Frequency Voltage Oscillations in the Neutral Point," *IEEE Trans. Ind. Electron.*, vol. 54, no. 4, pp. 2288–2294, Aug. 2007.

- [18] K.R.M.N. Ratnayake, Y. Murai and T. Watanabe, "Novel PWM scheme to control neutral point voltage variation in three-level voltage source inverter," in *Proc. 34th IAS Annu. Meeting*, 1999, pp. 1950-1955.

- [19] R.M. Tallam, R. Naik and T.A. Nondahl, "A carrier-based PWM scheme for neutral-point voltage balancing in three-level inverters," *IEEE Trans. Ind. Appl.*, vol. 41, no. 6, pp. 1734–1743, Nov./Dec. 2005.

- [20] R. Maheshwari, S. Munk-Nielsen and S. Busquets-Monge, "Design of Neutral-Point Voltage Controller of a Three-Level NPC Inverter With Small DC-Link Capacitors," *IEEE Trans. Ind. Electron.*, vol. 60, no. 5, pp. 1861–1871, May 2013.

- [21] W. Song, X. Feng and K.M. Smedley, "A Carrier-Based PWM Strategy With the Offset Voltage Injection for Single-Phase Three-Level Neutral-Point-Clamped

- Converters," IEEE Trans. Power Electron., vol. 28, no. 3, pp. 1083–1095, Mar. 2013.

- [22] J. Pou, J. Zaragoza, S. Ceballos, M. Saeedifard and D. Boroyevich, "A Carrier-Based PWM Strategy With Zero-Sequence Voltage Injection for a Three-Level Neutral-Point-Clamped Converter," *IEEE Trans. Power Electron.*, vol. 27, no. 2, pp. 642–651, Feb. 2012.

- [23] J. Shen, S. Schroder, B. Duro, R. Roesner, "A Neutral-Point Balancing Controller for a Three-Level Inverter With Full Power-Factor Range and Low Distortion," *IEEE Trans. Ind. Appl.*, vol. 49, no. 1, pp. 138–148, Jan./Feb. 2013.

- [24] J. Zaragoza, J. Pou, S. Ceballos, E. Robles, C. Jaen, and M. Corbalan, "Voltage-balance compensator for a carrier-based modulation in the neutral-point-clamped converter," *IEEE Trans. Ind. Electron.*, vol. 56, no. 2, pp. 305–314, Feb. 2009.

- [25] S. Busquets-Monge and A. Ruderman, "Carrier-based PWM strategies for the comprehensive capacitor voltage balance of multilevel multileg diode-clamped converters," in *Proc. ISIE*, 2010, pp. 688–693.

- [26] S. Kouro, P. Lezana, M. Angulo and J. Rodriguez, "Multicarrier PWM With DC-Link Ripple Feedforward Compensation for Multilevel Inverters," *IEEE Trans. Power Electron.*, vol. 23, no. 1, pp. 52–59, Jan. 2008.

- [27] N.A. Rahim, M.F.M. Elias, W.P. Hew, "Transistor-Clamped H-Bridge Based Cascaded Multilevel Inverter With New Method of Capacitor Voltage Balancing," *IEEE Ind. Electron.*, vol. 60, no. 8, pp. 294–2956, Aug. 2013.

- [28] Y. Ping, D. Vrancic, and R. Hanus, "Anti-windup, bumpless, and conditioned transfer techniques for PID controllers," *IEEE Trans. Contr. Syst. Technol.*, vol. 16, pp. 48–57, Jul. 1996.

- [29] J. Espina, A. Arias, J. Balcells and C. Ortega, "Speed Anti-Windup PI strategies review for Field Oriented Control of Permanent Magnet Synchronous Machines," in *Proc. CPE* '09, 2009, pp. 279–285.

- [30] S. Albatran, Y. Fu, A. Albanna, "Comprehensive Mathematical Description and Harmonic Analysis of Hybrid Two-Dimensional—Three-Dimensional Space Vector Modulation," *IEEE Trans. Ind. Electron.*, vol. 61, no. 7, pp. 3327–3336, Jul. 2014.

- [31] J. Pou, D. Boroyevich, R. Pindado, "Effects of imbalances and nonlinear loads on the voltage balance of a neutral-point-clamped inverter," *IEEE Trans. Power Electrons.*, vol. 20, no. 1, pp. 123–131, Jan. 2005.

- [32] V. Kaura and V. Blasco "Operation of a phase locked loop system under distorted utility conditions", *IEEE Trans. Ind. Appl.*, vol. 33, no. 1, pp.58–63 Jan./Feb. 1997.

# II. CAPACITOR VOLTAGE REGULATION AND PRE-CHARGE ROUTINE FOR A HYBRID MULTILEVEL RECTIFIER

Abstract—This paper investigated a routine for the three phase hybrid multilevel rectifier to be landed safely on a steady state. The three-phase hybrid multilevel rectifier consists of a neutral point clamped (NPC) and cascaded H-bridges (CHBs). The NPC has 2 capacitors and CHBs have 9 capacitors. If they are completely discharged and the system is connected with the grid, the rectifier might experience large inrush currents which can destroy the experimental set if components have current rating lower than the inrush current. Experiment had conducted with different voltage references under load resistance change. Load voltage regulation control scheme is described with block diagrams. Unity power factor control (PFC) is also achieved and explained with details. The system regulates 6 capacitor voltages in CHBs without using independent DC power sources. Experimental results show a pre-charge routine after connection with the grid as well as load voltage control and unity PFC for steady state.

### I. INTRODUCTION

Multilevel power conversion has been gaining a lot of attention in recent years due to the pressure of satisfying better power quality, efficiency and low cost simultaneously in high power application [1] [2]. Largely, three types of multilevel topology have been widely studied and researched, which are neutral-point clamped (NPC) [3], flying capacitor [4] and cascaded H-bridge [5]. Each type of topologies has different advantages

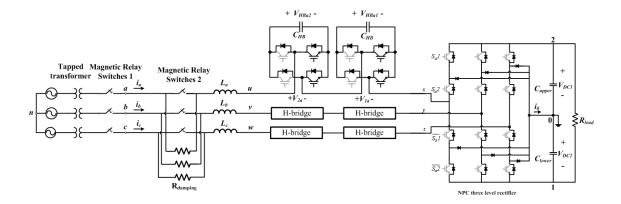

and disadvantages among various applications. So far, research has been mainly focusing on one single switching strategy which will govern all switching devices in the topology. It can be sinusoidal pulse width modulation (SPWM), space-vector modulation (SVM) or staircase modulation at fundamental switching frequency. Recently, papers have been published with an effort of trying to use two different types of semiconductor devices. Normally, thyristor such as Integrated Gate Commutated Thyristor (IGCT) or Gate Turn-Off (GTO) thyristor can be characterized with high voltage blocking capability and large current rating, but with slow switching speed. On the other hand, popularity of Insulated Gate Bipolar Transistors (IGBTs) and Metal-Oxide Semiconductor Field Effect Transistors (MOSFETs) is based on their medium voltage blocking capability and medium current rating with fast switching speed. So, hybrid multilevel topology is based on hybrid usage of the two kinds of devices [6]-[19]. At first, the hybrid multilevel topology has been researched with a strategy using independent DC power supplies on each CHBs [6]-[12]. In order to save cost of DC power supplies, many methods that regulate CHB capacitor voltages have been suggested [13]–[19].

In an active rectifier application, a pre-charge routine is needed to protect the set from inrush currents [22]. The three-phase hybrid multilevel rectifier has 2 capacitors on the NPC and 9 capacitors on the CHBs. Therefore, large inrush currents can cause hazards on the set if they are completely discharged and components of the set have low current rating than the inrush current. Thus the 11 capacitor voltages need to be charged before unity PFC and load voltage control are activated in a feedback control. The precharge routine has several steps including 1) grid connection, 2) removing damping resistors, 3) open loop control and 4) closed loop control. Regarding the open loop

control, a reference for the hybrid multilevel rectifier is calculated based on a vector diagram.

There are three main goals in a grid-connected rectifier application: 1) unity PF generating grid line currents in phase with phase voltages, 2) load voltage regulation even under load change circumstances and 3) capacitor voltage regulation of CHBs which are connected in series with a NPC. Experiment had been conducted with a TMS320F28335 DSP board. The multilevel converter has totally 36 switching devices excluding diodes. This paper is also describing how to generate 36 switching signals with only one DSP.

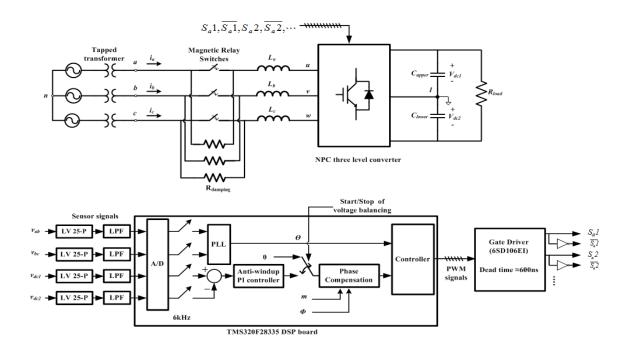

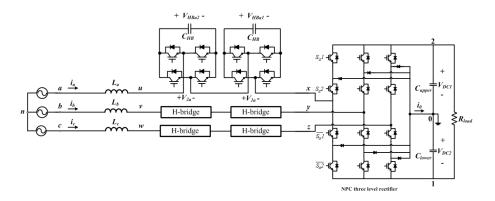

# II. HYBRID MULTILEVEL RECTIFIER

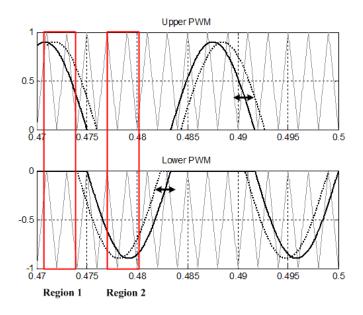

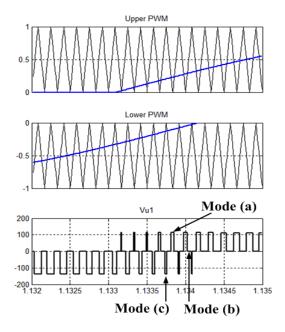

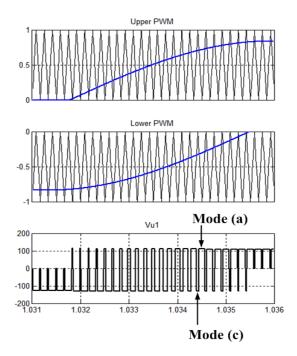

Figure 1. is the hybrid multilevel rectifier which consists of three phase NPC and 6 CHBs. The main NPC operates with square waveforms at fundamental frequency. So, the NPC provides most power to the load R. Figure 2. shows the modulation strategy that governs the hybrid multilevel rectifier. The NPC phase voltage  $V_{x0}$  forms a square voltage waveform. In order to make the grid current sinusoidal, the 6 CHBs generates harmonics for the output voltage  $V_{ag}$ . So, the rectifier output voltage  $V_{u0}$  builds 7-level PWM voltage waveform by summing  $V_{x0}+V_{1a}+V_{2a}$ . As the main NPC provides power to the load R, the output of the CHBs is not connected to any resistive load. They are just floating voltage regulated by a closed loop which is discussed in section IV with details.

Figure 1. Hybrid multilevel rectifier consisting of the NPC and the CHBs

Figure 2. Experimental results explaining hybrid modulation method (a)  $V_{u0}$ , the hybrid multilevel rectifier output voltage,

- (b)  $V_{x0}$ , square waveform for the NPC,

- (c)  $V_{1a}$ , output voltage of the 1st H-bridge

- (d) V<sub>2a</sub>, output voltage of the 2nd H-bridge

# III. REGULATING H-BRIDGE VOLTAGES

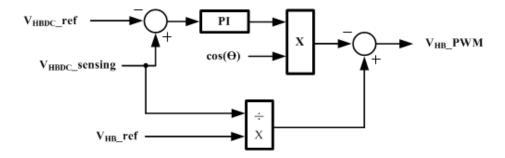

Since the hybrid multilevel rectifier does not use independent voltage sources on the CHB capacitors, feedback loops for regulating CHB voltages are required. Figure 3. shows a feedback loop block diagram. The  $V_{HBDC}$ \_ref is DC value calculated by simply using  $(V_{DC1}+V_{DC2})\times0.25$  and  $V_{HBDC}$ \_sensing is information from voltage sensors. The  $V_{HB}$ \_ref can be calculated by subtracting the square waveform in Figure 2. from a sinusoidal reference. There are two stages of H-bridges after NPC, thus  $V_{HB}$ \_ref would be divided by 2. The signal  $\cos(\theta)$  is just for phase A, so it can be  $\cos(\theta\pm2\pi/3)$  for phase B and C. The result  $V_{HB}$ \_PWM is compared with triangular waveforms of ePWM channels in a DSP. When  $V_{HBDC}$ \_sensing on phase A went higher than the desired  $V_{HBDC}$ \_ref, output of the PI controller multiplied with  $\cos(\theta)$  will be subtracted from  $V_{HB}$ \_ref. That process causes PWM pulses of the CHB on phase A narrower so that a capacitor on phase A is charging less. As a result, the feedback loop of Figure 3. regulates CHB voltages as well as it creates the CHB output voltage similar with 1st and 2nd CHB output voltages as depicted in Figure 2.

Figure 3. Feedback loop block diagram for regulating H-bridge voltage

# IV. UNITY POWER FACTOR CONTROL AND LOAD VOLTAGE CONTROL

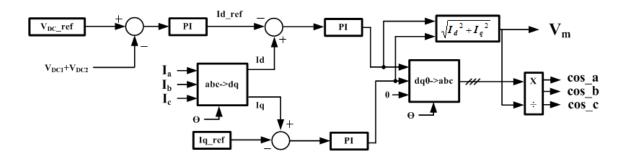

Unlike SPWM or SVPWM strategy, hybrid multilevel uses low frequency switching for the NPC and high switching frequency for CHBs. So the output of a closed loop should be  $V_m$  (maximum modulation index) and three phase sinusoidal waveform with amplitude  $\pm 1$ . Figure 4. displays feedback loop for unity PFC and load voltage control. The  $V_{DC\_ref}$  is the reference for the NPC capacitor voltages ( $V_{DC1}+V_{DC2}$ ). The sensing information of  $V_{DC1}+V_{DC2}$  is fed back to the loop and is compared with the  $V_{DC\_ref}$ . The outputs of the PI controller for the load voltage control are  $I_{q\_ref}$  and  $I_{d\_ref}$ . It needs to be limited by a certain value depending on the grid current rating of the system. The three grid currents  $I_a$ ,  $I_b$  and  $I_c$  are transformed to dq-axis with grid voltage angle  $\theta$ , which is the result of PLL. Because this control is for achieving unity PFC, the  $I_{q\_ref}$  is zero.

Figure 4. Feedback loop block diagram for unity displacement power factor control and load voltage control.

#### V. PRE-CHARGE ROUTINE

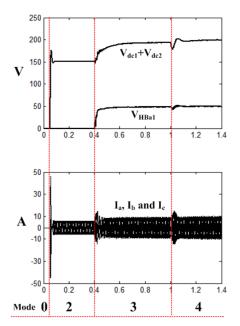

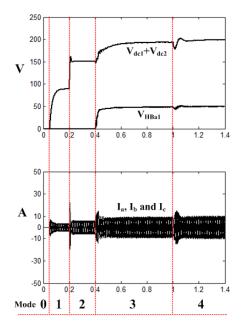

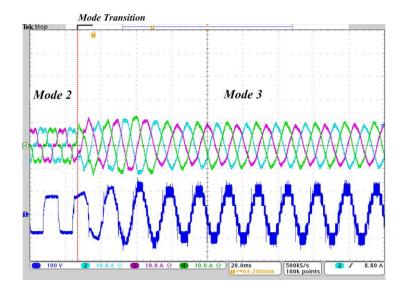

Before achieving regulation of CHB voltages (section III), unity PFC and load voltage control (section IV), the hybrid multilevel rectifier should pre-charge capacitors for preventing large inrush current from the grid. Table I represents operation modes for starting up the hybrid multilevel rectifier. In mode 0, the rectifier is completely disconnected from the grid. In mode 1, the experimental set is connected by turning on the magnetic relay switch 1 with damping resistors as described in Figure 1. The damping resistors is removed from the set by using the magnetic relay switch 2 as defined in mode 2. Therefore, the two NPC capacitors are charged to certain level during mode 1 and mode 2. Also, the on/off states of the all switches in the rectifier are shown in Figure 1. The grayed switches in Figure 1. are off so that CHBs are by-passed and the NPC acts like a diode rectifier. During the mode 3, the switching action for the NPC and HBs is activated and 6 HB capacitors are charged. The critical difference between mode 3 and 4 is the feedback control loop described in Figure 4. Mode 3 uses fixed voltage reference for the rectifier, which is explained in section VI. Figure 5. shows the simulation result that describes large inrush current from the grid when damping resistors are not used. Figure 6. represents acceptable grid currents with damping resistors.

Table 1. Operation Modes for Starting up the Hybrid Multilevel Rectifier

| Mode | Grid connection | Damping resistors | Charging<br>CHB caps | Charging<br>NPC caps | Unity PFC<br>Load<br>voltage |

|------|-----------------|-------------------|----------------------|----------------------|------------------------------|

| 0    | X               | 0                 | X                    | X                    | X                            |

| 1    | 0               | 0                 | X                    | O (low level)        | X                            |

| 2    | 0               | X                 | X                    | O (high level)       | X                            |

| 3    | 0               | X                 | О                    | O                    | X                            |

| 4    | 0               | X                 | О                    | 0                    | О                            |

Figure 5. Large inrush currents without damping resistors

Figure 6. Acceptable grid currents with damping resistors

# VI. OPEN LOOP CONTROL OF THE HYBRID MULTILEVEL RECTIFIER

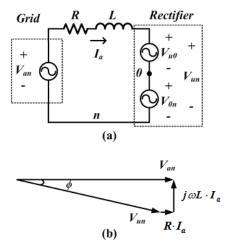

Figure 7. explains how the value  $V_m$  and  $\phi$  are calculated and used during the mode 3. Figure 7-(a). is a simplified circuit with only phase A. The resistor R is parasitic resistance in the filter inductor L. The circuit can be expressed by (1). In turn, (1) gives phasor representation. From Figure 7-(b)., the value  $V_m$  and  $\phi$  can be calculated by using (2). With conditions of Ia\_peak=10 A, R=0.2 $\Omega$ ,  $V_m$ =100.5765 and cos\_a=  $\cos(\theta+\phi)=\cos(\theta-0.2268)$ . Therefore, during the mode 3, the rectifier voltage reference is fixed with  $V_m$ ,  $\cos_a$ ,  $\cos_b$  and  $\cos_c$ . Otherwise during the mode 4,  $V_m$ ,  $\cos_a$ ,  $\cos_b$  and  $\cos_c$  are determined by the feedback loop depicted in Figure 4.

$$-V_{an} + (R + j\omega L)I_a + V_{un} = 0 \tag{1}$$

$$\phi = -\tan^{-1} \frac{\omega L \cdot I_a}{V_{an} - R \cdot I_a}, \quad |V_{un}| = V_m = \sqrt{(V_{an} - R \cdot I_a)^2 + (\omega L \cdot I_a)^2}$$

(2)

Figure 7. Calculation of the value  $V_m$  and  $\phi$  (a) simplified power circuit only with phase A ,(b) Phasor representation that makes the rectifier achieve unity PF

# VII. EXPERIMENTAL RESULTS

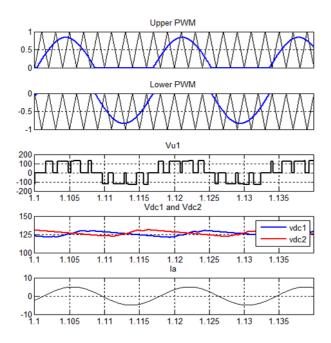

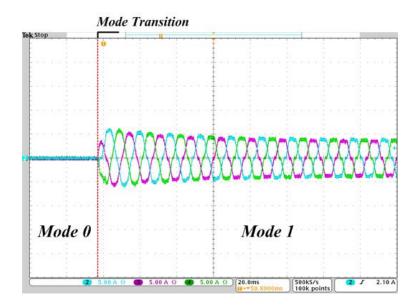

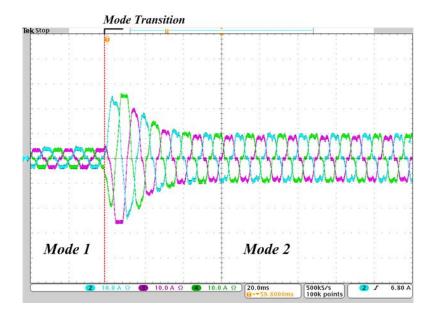

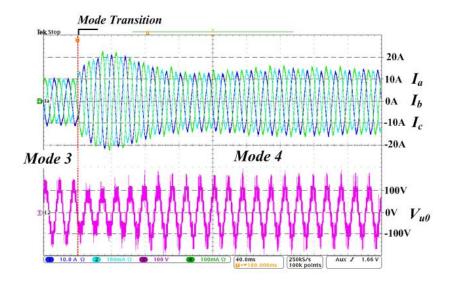

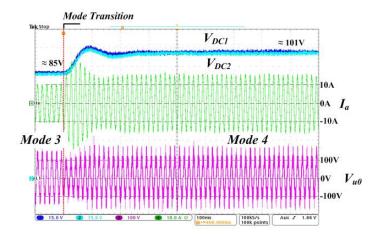

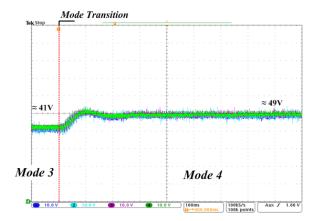

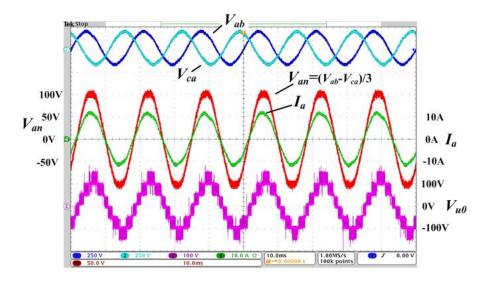

The specifications of the system are as follows: phase voltage  $V_{grid\_peak} = 100 \text{ V}$ , grid frequency=60 Hz, switching frequency for CHBs = 6 kHz, sampling frequency = 6kHz, L = 6 mH,  $C_{upper} = C_{lower} = 11.7$  mF,  $C_{HB} = 3.9$ mF,  $R_{damping} \approx 15 \Omega$ ,  $R_{load} \approx 24 \Omega$ . This experiment was conducted with one TMS320F28335 DSP board. Voltage sensors are LV 25-P and current sensors are LA 55-P. Since this system acts as a rectifier, the grid current's direction is set from the grid to the rectifier. The actual angle of the grid voltage will be calculated by using PLL after the rectifier is connected with the grid. The PLL is designed based on synchronous reference frame and it forms feedback loop [20]. TMS320F28335 DSP has 6 ePWM modules and each module can generate 2 PWM signals. So 12 PWM channel are set to generate switching signals for 6 CHBs. The 1st and 2nd stage of CHB has 90 degree difference in triangular waveforms [21]. Figure 8. shows the acceptable grid currents with damping resistors after mode transition from mode 0 to mode 1. Figure 9. represents grid currents after removing damping resistors. Regarding the transition from mode 2 to mode 3, three grid currents and the hybrid multilevel rectifier output voltage V<sub>u0</sub> are described in Figure 10. Figures 11.–13. display transient responses of grid currents, rectifier output voltage, NPC voltages and CHB voltages for mode transition from mode 3 to mode 4. From Figures 12. and 13., the load voltage control described in Figure 4. works well by observing the NPC voltage=202 V and CHB voltage 49 V with V<sub>dc</sub>\_ref=200V.

Figure 8. Acceptable grid currents with damping resistors after connecting with the grid (from mode 0 to mode 1)

Figure 9. Acceptable grid currents after removing damping resistors (from mode 1 to mode 2)

Figure 10. Grid currents and the rectifier output voltage  $V_{u0}$  after activating NPC and CHB switching (from mode 2 to mode 3)

Figure 11. Transient responses of grid current and hybrid multilevel phase voltage output when voltage feedback loop is activated with  $V_{DC\_ref}=200V$  (from mode 3 to mode 4).

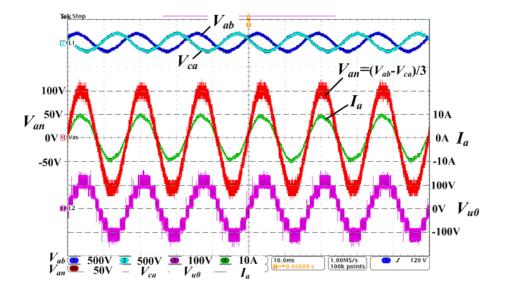

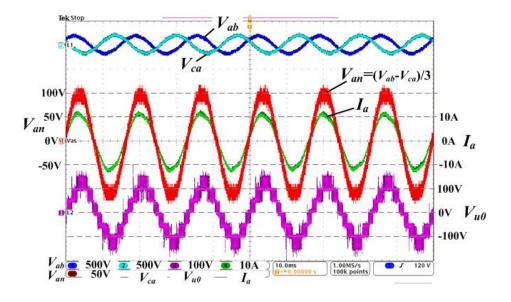

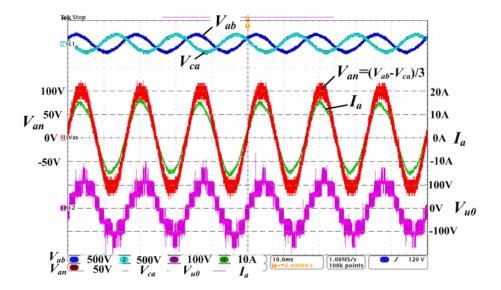

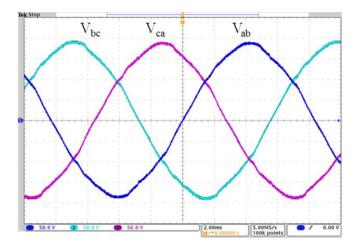

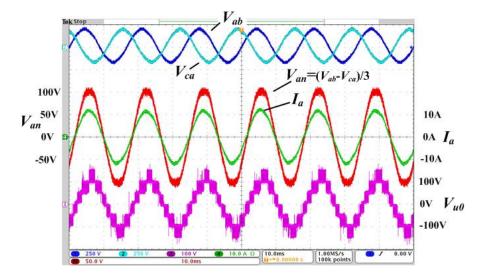

Figure 14.–16. demonstrates that the unity PFC achieves the grid current  $I_a$  in phase with the grid phase voltage  $V_{an}$  which is calculated by using  $(V_{ab}-V_{ca})/3$  in the oscilloscope during mode 4 with three different  $V_{DC}$ \_ref.

Figure 12. Transient responses of NPC voltages  $V_{DC1}$  and  $V_{DC2}$  when voltage feedback loop is activated with  $V_{DC\_}$ ref=200 (from mode 3 to mode 4).

Figure 13. Transient responses of H-bridge voltages VHBa2, VHBa1, VHBb1 and VHBc1 when voltage feedback loop is activated with  $V_{DC}$ \_ref=200 (from mode 3 to mode 4).

Figure 14. Steady state waveforms of grid current  $I_a$  and hybrid multilevel output  $V_{u0}$  with  $V_{DC\_}$ ref=165 (mode 4).

Figure 15. Steady state waveforms of grid current  $I_a$  and hybrid multilevel output  $V_{u0}$  with  $V_{DC\_}$ ref=180 (mode 4).

Figure 16. Steady state waveforms of grid current  $I_a$  and hybrid multilevel output  $V_{u0}$  with  $V_{DC\_ref}$ =200 (mode 4).

# VIII. CONCLUSION

This paper has presented complete procedure of start-up routine to run the hybrid multilevel rectifier which consists of the NPC and the CHBs. The hybrid multilevel has total 11 capacitors that need to be charged before achieving unity PFC and load voltage regulation. In a worst case of completely discharged capacitors, large inrush grid currents can destroy devices in the set. Therefore, a safe start-up routine is essential. This paper suggests the start-up routine from a situation that the rectifier is disconnected with the grid, to steady state responses that achieve CHB voltage regulation, load voltage regulation and unity PFC step by step. The experimental results have verified the start-up routine and steady state operation of the hybrid multilevel rectifier.

### REFERENCES

- [1] M. D. Manjrekar, P. K. Steimer, and A. Lipo, "Hybrid multilevel power conversion system: A competitive solution for high power applications," IEEE Trans. Ind. Appl., vol. 36, no. 3, pp. 834–841, Jun. 2000.

- [2] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L.G. Franquelo, B. Wu, J. Rodriguez, M.A. Perez, J.I. Leon, "Recent Advances and Industrial Applications of Multilevel Converters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2553-2580, Aug. 2010.

- [3] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," IEEE Trans. Ind. Appl., vol. 1A-17, no. 5, pp. 518–523, Sep./Oct. 1981.

- [4] M. F. Escalante, J. C. Vannier, and A. Arzande, "Flying capacitor multilevel inverters and DTC motor drive applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 809–815, Aug. 2002.

- [5] F. Z. Peng, J.W. McKeever, and D. J. Adams, "Cascade multilevel inverters for utility applications," in Proc. IEEE IECON 1997, vol. 2, pp. 437–442.

- [6] M. Manjrekar and T. A. Lipo, "A hybrid multilevel inverter topology for drive application," in Proc. Appl. Power Electron. Conf., 1998, vol. 2, pp. 523–529.

- [7] K. Corzine and Y. Familiant, "A new cascaded multilevel H-bridge drive," IEEE Trans. Power Electron., vol. 17, no. 1, pp. 125–131, Jan. 2002.

- [8] C. A. Silva, L. A. Cordova, P. Lezana, and L. Empringham, "Implementation and control of a hybrid multilevel converter with floating dc links for current waveform improvement," IEEE Trans. Ind. Electron., vol. 58,no. 6, pp. 2304–2312, Jun. 2011.

- [9] C. Rech and J. R. Pinheiro, "Impact of hybrid multilevel modulation strategies on input and output harmonic performances," IEEE Trans. Power Electron., vol. 22, no. 3, pp. 967–977, May 2007.

- [10] S. Fukuda, T. Yoshida, and S. Ueda, "Control strategies of a hybrid multilevel converter for expanding adjustable output voltage range," IEEETrans. Ind. Appl., vol. 45, no. 2, pp. 827–835, Mar./Apr. 2009.

- [11] M. K. Menshawi, M. N. Abdul Kadir, and S. Mekhilef, "Voltage Vector Approximation Control of Multistage—Multilevel Inverter Using Simplified Logic Implementation," IEEE Trans. Ind. Informatics, vol. 9, no. 4, pp. 2052–2062, Nov. 2013.

- [12] A. Nami, F. Zare, A. Ghosh, F. Blaabjerg, "A Hybrid Cascade Converter Topology With Series-Connected Symmetrical and Asymmetrical Diode-Clamped H-Bridge Cells," *IEEE Trans. Power Electron.*, vol. 26, no. 1, pp. 51-65, Jan. 2011.

- [13] H. Sepahvand, M. Ferdowsi, and K. A. Corzine, "Fault recovery strategy for hybrid cascaded H-bridge multi-level inverters," in Proc. IEEE Appl. Power Electron. Conf. Expo., 2011, pp. 1629–1633.

- [14] L. Jingsheng, K. Corzine, and M. Ferdowsi, "A new control method for single-dc-source cascaded H-bridge multilevel converters using phase shift modulation," in Proc. 23rd Annu. IEEE APEC, 2008, pp. 886–890.

- [15] D. Sixing, J. Liu, J. Lin, and Y. He, "A novel DC voltage control method for STATCOM Based on hybrid multilevel H-bridge converter," IEEE Trans. Power Electron., vol. 28, no. 1, pp. 101–111, Jan. 2013.