# Scholars' Mine

**Doctoral Dissertations**

Student Theses and Dissertations

Spring 2015

# Electromagnetic compatibility in power inverter design

Natalia Bondarenko

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Electromagnetics and Photonics Commons Department: Electrical and Computer Engineering

#### **Recommended Citation**

Bondarenko, Natalia, "Electromagnetic compatibility in power inverter design" (2015). *Doctoral Dissertations*. 2378. https://scholarsmine.mst.edu/doctoral\_dissertations/2378

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# ELECTROMAGNETIC COMPATIBILITY IN POWER INVERTER DESIGN

by

# NATALIA BONDARENKO

### A DISSERTATION

Presented to the Faculty of the Graduate School of the

# MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

# DOCTOR OF PHILOSOPHY

in

# ELECTRICAL ENGINEERING

## 2015

Approved Daryl G. Beetner, Advisor James L. Drewniak Jun Fan David J. Pommerenke Albert E. Ruehli Daniel S. Stutts

### PUBLICATION DISSERTATION OPTION

This dissertation has been prepared in the form of four papers for publication.

The first paper, from pages 4 to 30, presents A Measurement-Based Model of the Electromagnetic Emissions from a Power Inverter. This extended work has been accepted for publication with the IEEE Transactions on Power Electronics. The second paper, from pages 31 to 61, presents the Development of Simple Physics-Based Interconnect Models for Power Electronics, and is to be submitted to IEEE Transactions on Electromagnetic Compatibility. The third paper, from pages 61 and 74, presents Prediction of Common-Mode Current Reduction Using Ferrites in Systems with Cable Harnesses, and has been published in the Proceeding of the IEEE EMC Symposium 2012, Pittsburgh, August 2012, pp. 80-84. The fourth paper, from pages 74 to 100, presents a Common-mode Impedance of a Ferrite Choke on a Cable Harness, and has been submitted to IEEE Transactions on Electromagnetic Compatibility.

#### ABSTRACT

Power inverter systems generate significant electromagnetic emissions. Methods were studied to model these systems and to reduce their emissions. Three topics are presented in this dissertation.

Methods were developed to obtain simple SPICE models for complex systems which relate circuit components to physical geometry within the system. These models were derived using measurements or using partial element equivalent circuit (PEEC) and model size reduction techniques developed in this dissertation. Methods were proposed for developing a measurement-based model and were applied to a real power inverter/motor system. The model was used to identify system geometries responsible for critical resonances and to guide development of emission reduction strategies. A method was also proposed for developing a simple SPICE circuit by collapsing the many elements in a PEEC model into a reasonable number of elements which can still be related directly to the physical geometry responsible for the parasitics. This method was validated on realistic interconnects used in power electronics based on the frequencydependent behavior of port impedances.

Methods were also developed to predict the effects of ferrite chokes on the commonmode impedance and common-mode current of an active power systems when the ferrite is placed on the power cables. A high frequency analytical ferrite choke model was developed. Active common-mode loop impedance is found using the dual current clamp technique. The effectiveness of the approach was demonstrated on a real, active power/inverter system.

#### ACKNOWLEDGMENTS

I would like to take this opportunity and thank all the people that helped me with this research. First of all I want to sincerely thank my adviser Dr. Daryl Beetner. Without his guidance, patience and immense knowledge I would not be able to fulfill this work. Special thanks to Dr. James Drewniak for his advice, encouragement and trust in my abilities. Many thanks to Dr. David Pommerenke and Dr. Jun Fan for very interesting and inspiring classes that helped greatly with my research. I would like to thank Dr. Albert Ruehli, Dr. Marina Koledintseva and Dr. Tom Van Doren for their help and valuable advice along the way I was pursuing my degree. I am also grateful to Dr. Daniel Stutts, Dept. of Mechanical and Aerospace Eng., for his time and guidance. Additional gratitude is owed to Phil Berger for supporting my research during my PhD studies.

It is my pleasure to thank all the former and current members of the EMC Laboratory for their collaboration and hard work.

Finally, I want to thank my whole family and all my friends for their support and encouragement towards achieving this degree. Especially, I am thankful to my parents, my dear husband Andriy and little daughter Milana for emotional support and love.

# TABLE OF CONTENTS

|                                                     | Page |

|-----------------------------------------------------|------|

| PUBLICATION DISSERTATION OPTION                     | iii  |

| ABSTRACT                                            | iv   |

| ACKNOWLEDGMENTS                                     | v    |

| LIST OF ILLUSTRATIONS                               | ix   |

| LIST OF TABLES                                      | xiii |

| SECTION                                             |      |

| 1. INTRODUCTION                                     | 1    |

| PAPER                                               |      |

| I. A MEASUREMENT-BASED MODEL OF THE ELECTROMAGNETIC |      |

| EMISSIONS FROM A POWER INVERTER                     | 4    |

| I. INTRODUCTION                                     | 4    |

| II. CONSTRUCTION OF THE EQUIVALENT CIRCUIT          | 7    |

| A. AC and DC cables                                 | 9    |

| B. DC Link                                          | 10   |

| C. IGBT                                             | 13   |

| D. AC bus bars                                      | 14   |

|                                                     |      |

| ACKNOW   | VLEDGMENTS                                      | v    |

|----------|-------------------------------------------------|------|

| LIST OF  | ILLUSTRATIONS                                   | ix   |

| LIST OF  | TABLES                                          | xiii |

| SECTION  | 1                                               |      |

| 1. IN7   | FRODUCTION                                      | 1    |

| PAPER    |                                                 |      |

| I. A MEA | SUREMENT-BASED MODEL OF THE ELECTROMAGNETIC     |      |

| EMISS    | IONS FROM A POWER INVERTER                      | 4    |

| I.       | INTRODUCTION                                    | 4    |

| II.      | CONSTRUCTION OF THE EQUIVALENT CIRCUIT          | 7    |

|          | A. AC and DC cables                             | 9    |

|          | B. DC Link                                      | 10   |

|          | C. IGBT                                         | 13   |

|          | D. AC bus bars                                  | 14   |

|          | E. Complete system                              | 15   |

| III.     | VALIDATION OF COMPLETE MODEL                    | 16   |

| IV.      | CORRELATION OF SYSTEM RESONANCES WITH GEOMETRY. | 18   |

| V.       | MITIGATION OF SYSTEM RESONANCES                 | 20   |

|          | A. Adding low frequency ferrite chokes          | 21   |

|          | B. Adding RC filters                            | 22   |

|          | C. Combined mitigation strategies               |      |

|          | D. Validation of mitigation techniques          |      |

| VI.      | RADIATED EMISSIONS                              |      |

| VII      | . GENERAL METHODOLOGY                           | 25   |

| VII      | I. CONCLUSIONS                                  |      |

| IX.      | APPENDICES                                      |      |

|          |                                                 |      |

| Х.        | REFERENCES                                          | 29 |

|-----------|-----------------------------------------------------|----|

| II. DEVE  | LOPMENT OF SIMPLE PHYSICS-BASED INTERCONNECT MODELS |    |

| FOR P     | OWER ELECTRONICS                                    | 30 |

| I.        | INTRODUCTION                                        | 31 |

| II.       | PEEC FORMULATION                                    | 33 |

|           | A. Partial elements                                 | 34 |

|           | B. PEEC analysis                                    | 36 |

| III.      | PHYSICS-BASED MODEL SUZE REDUCTION                  | 37 |

|           | A. R and L matrices reduction                       | 38 |

|           | B. Branch Tearing for Loops                         | 40 |

|           | C. Example with the loop for L reduction            | 43 |

|           | D. C model reduction                                | 46 |

| IV.       | APPROACH VALIDATION                                 | 48 |

|           | A. Simple structure                                 | 49 |

|           | B. Real DC link                                     | 55 |

|           | C. Error estimation                                 | 57 |

| V.        | RULES FOR REDUCTION METHOD                          | 58 |

| VI.       | CONCLUSIONS                                         | 59 |

| VII       | . REFERENCES                                        | 60 |

| III. PRED | ICTION OF COMMON-MODE CURRENT REDUCTION USING       |    |

| FERR      | ITES IN SYSTEMS WITH CABLE HARNESSES                | 61 |

| I.        | INTRODUCTION                                        | 62 |

| II.       | ANALYTICAL MODEL                                    | 63 |

| III.      | MEASUREMENT OF COMMON-MODE LOOP IMPEDANCE           | 65 |

| IV.       | APPLICATION OF ANALYTICAL MODEL TO A SIMPLE SYSTEM  | 67 |

| V.        | APPLICATION OF ANALYTICAL MODEL TO A REAL POWER     |    |

|           | SYSTEM                                              | 69 |

| VI.       | CONCLUSIONS                                         | 72 |

| VII       | . AKNOWLEDGMENT                                     | 72 |

| VII       | I. REFERENCES                                       | 72 |

| IV. COMMON-MODE IMPEDANCE OF A FERRITE CHOKE ON A CABLE |     |

|---------------------------------------------------------|-----|

| HARNESS                                                 | 74  |

| I. INTRODUCTION                                         | 74  |

| II. ANALYTICAL MODEL                                    | 77  |

| A. Calculation of per-unit-length inductance (L)        |     |

| B. Calculation of per-unit-length resistance (R)        | 81  |

| C. Calculation of per-unit-length capacitance (C)       | 82  |

| D. Calculation of per-unit-length conductance (G)       | 84  |

| III. EXPERIMENTAL VALIDATION OF THE SYSTEM              | 84  |

| A. Modeling the test structure                          | 85  |

| B. Test-structure impedance without ferrite             | 88  |

| IV. APPLICATION TO A REAL POWER SYSTEM                  | 95  |

| V. CONCLUSIONS                                          | 97  |

| VI. REFRENCES                                           | 98  |

| SECTION                                                 |     |

| 2. CONCLUSIONS                                          | 100 |

| VITA                                                    | 102 |

# LIST OF ILLUSTRATIONS

|                                                                                                                                                                                                                                                   | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| PAPER I                                                                                                                                                                                                                                           |      |

| Fig. 1. Power inverter/motor system                                                                                                                                                                                                               | 7    |

| Fig. 2. Power inverter enclosure with DC link capacitor, DC bus bars, IGBT and AC bus bars.                                                                                                                                                       |      |

| Fig. 3. Location of the main "noise" source inside the IGBT module                                                                                                                                                                                | 8    |

| Fig. 4. Validation of the transmission line model for the open ended DC cable.<br>Measured values are shown with a solid line and simulated values with a dashed line.                                                                            | 9    |

| Fig. 5. Schematic of DC link.                                                                                                                                                                                                                     | 11   |

| <ul><li>Fig. 6. Example measurement made to obtain the DC link capacitor block parasities</li><li>(a) from connected DC+ cable, DC link and Y-caps connected to chassis, at 1 MHz and (b) from impedance looking into Y-caps at 10 MHz.</li></ul> |      |

| Fig. 7. Equivalent model of one phase of the IGBT module, IGBT connection and A bus bar                                                                                                                                                           |      |

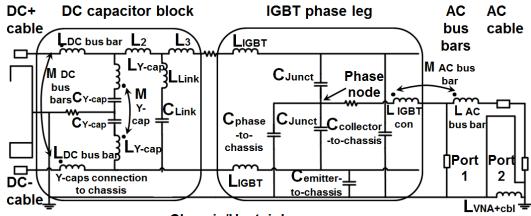

| Fig. 8. Complete equivalent circuit model. Port one: between phase node and chassi<br>Port 2: between inner and outer conductors at the end of the AC cable                                                                                       | -    |

| Fig. 9. Measurement setup used to validate overall inverter model.                                                                                                                                                                                | 16   |

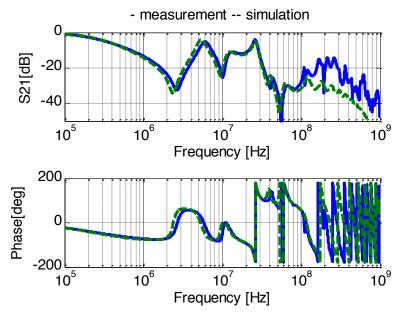

| Fig. 10. Magnitude and phase of S21 between the phase node and the output of the AC cable.                                                                                                                                                        | 17   |

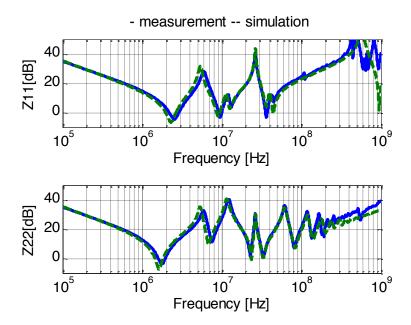

| Fig. 11. Magnitude of Z11 looking into the phase node and Z22 looking into the AC cable output.                                                                                                                                                   |      |

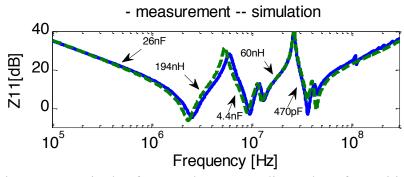

| Fig. 12. Magnitude of Z11 and corresponding value of parasitics.                                                                                                                                                                                  | 18   |

| Fig. 13. Analysis of current path for one problematic frequency (5 MHz).                                                                                                                                                                          | 19   |

| Fig. 14. Change in S21 from added low-frequency ferrites                                                                                                                                                                                          | 22   |

| Fig. 15. Predicted effect of combined countermeasures on S21                                                                                                                                                                                      | 23   |

| Fig. 16. Measured and simulated values of S21 when RC filters and a ferrite are added to the inverter                                                                                                                                             | 24   |

| Fig. 17. Setup used for radiated emissions measurements                                                                                                                                                                                           | 25   |

| Fig. 18. Correlation between changes in S21 and radiated emissions                                                                                                                                                                                | 25   |

| Fig. 19. Effect of AC and DC cable length on S21                                                                                                                                                                                                  | 28   |

| Fig. 20. Effect of DC cable length when the cable is low loss                                                                                                                                                                                     | 29   |

# PAPER II

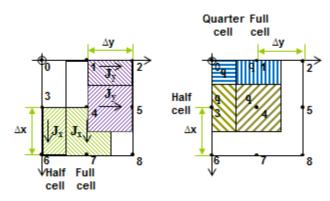

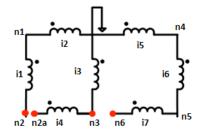

| Fig. 1. Example of inductive and capacitive cells for a thin metal plane                                                 | 36 |

|--------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2. Example of a classic PEEC cell circuit.                                                                          | 36 |

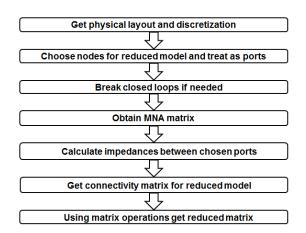

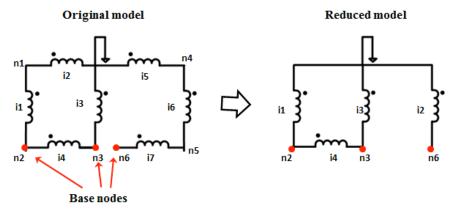

| Fig. 3. Steps for R and L matrices reduction.                                                                            | 38 |

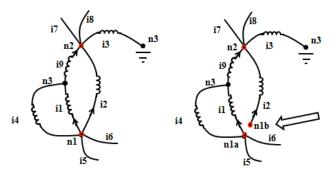

| Fig. 4. Simplest example of the loop problem for reduction.                                                              | 40 |

| Fig. 5. Loop definition and example of breaking a loop                                                                   | 41 |

| Fig. 6. Example of grouping loops                                                                                        | 42 |

| Fig. 7. Using reduced row echelon form to find possible locations to break loops                                         | 43 |

| Fig. 8. Connectivity matrix after breaking two loops                                                                     | 43 |

| Fig. 9. Simple structure with a closed and a semi closed loop.                                                           | 44 |

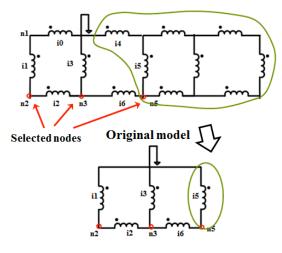

| Fig.10. Original model and desired reduced model with ports representing nodes that we want to keep in the reduced model | 44 |

| Fig.11. Grouping two parts of a loop                                                                                     | 44 |

| Fig.12. Increasing number of mesh cells and defining "boundaries"                                                        | 45 |

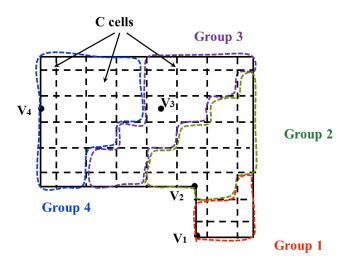

| Fig.13. Forming groups for capacitance reduction based on voltage distribution                                           | 46 |

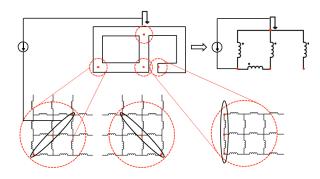

| Fig.14. Simple structure used to validate the method                                                                     | 49 |

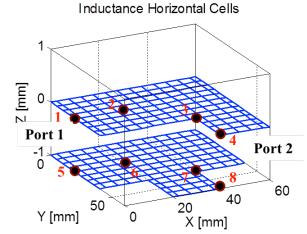

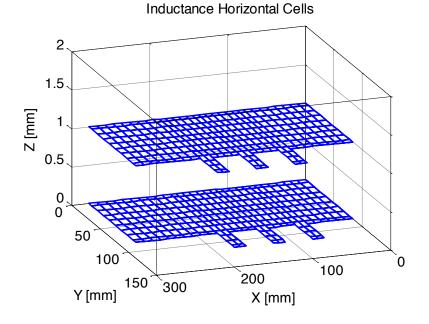

| Fig. 15. Inductive cells and base nodes of a simple structure                                                            | 50 |

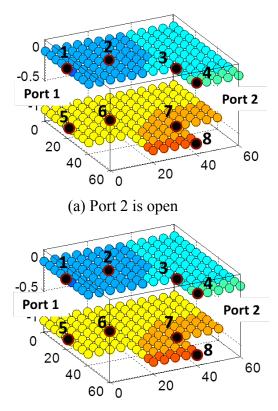

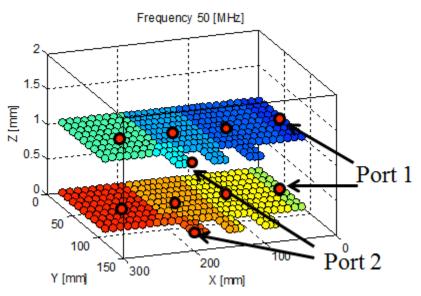

| Fig. 16. Capacitive groups around base nodes for cases when Port 2 is open and closed at 50 MHz.                         | 50 |

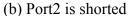

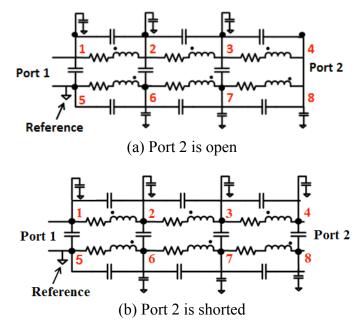

| Fig. 17. Reduced model with 19 self terms when Port 2 is open. Node numbers correspond to nodes marked in Fig. 16.       | 51 |

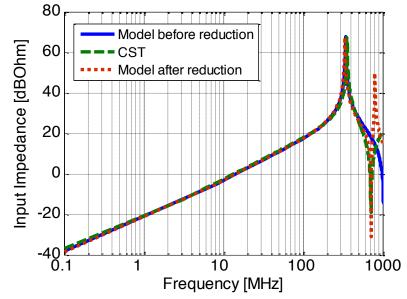

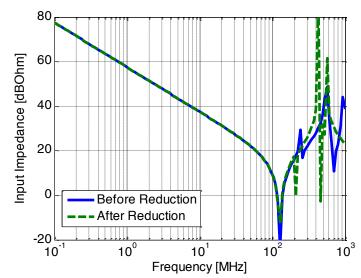

| Fig. 18. Magnitude of the input impedance of a simple test structure when Port 2 is shorted.                             | 52 |

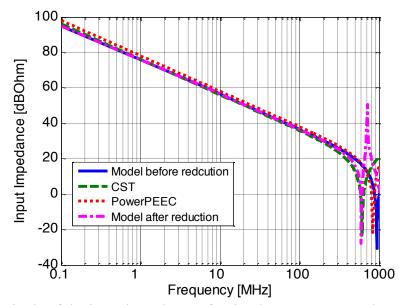

| Fig. 19. Magnitude of the input impedance of a simple test structure when Port 2 is open.                                | 53 |

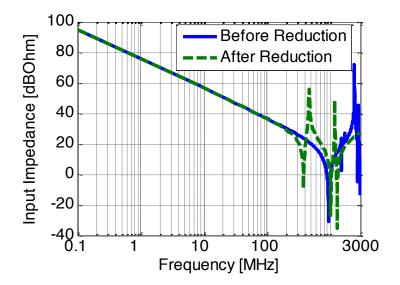

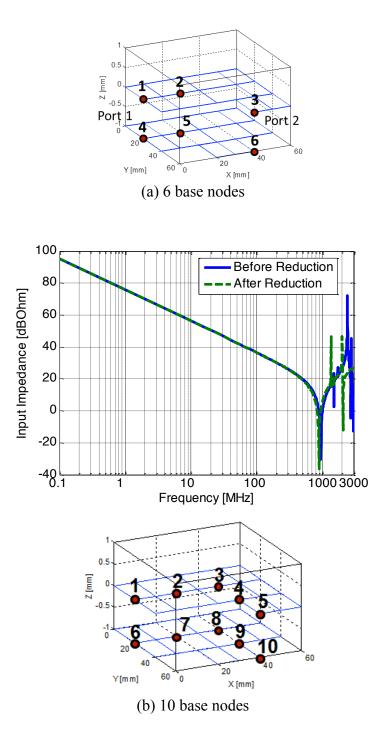

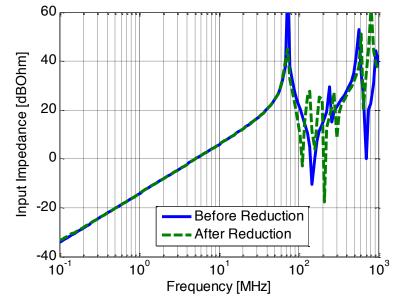

| Fig. 20. Input impedance for Port 2 open case with different number of base nodes                                        | 54 |

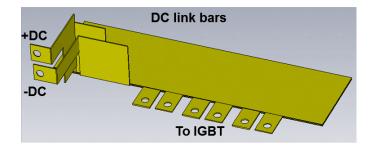

| Fig. 21. DC link in power inverter system.                                                                               | 55 |

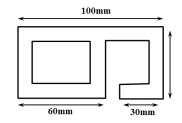

| Fig. 22. Geometry of the power inverter DC link capacitor.                                                               | 55 |

| Fig. 23. Inductive cells for upper and lower DC link bus bars.                                                           | 56 |

| Fig. 24. Capacitive groups for 50 MHz frequency when Port 2 is open                                                      | 56 |

| Fig. 25. Magnitude of Z11 before and reduction for open DC link case                                                     | 57 |

| Fig. 26. Magnitude of Z11 before and after reduction for shorted DC link case                                            | 57 |

| Fig. 27. Error estimation of reduction method                                                                            | 58 |

# PAPER III

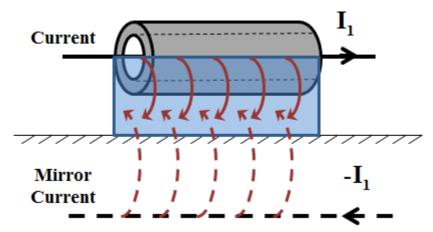

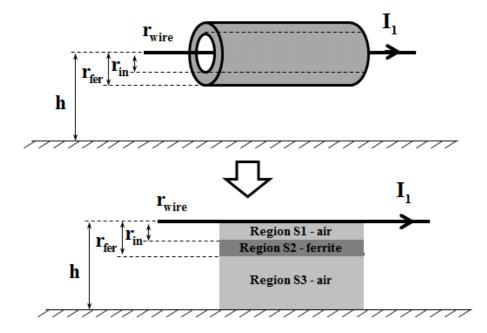

| Fig. 1. | Geometry associated with the ferrite over the return plane                                                                                                                                              | 64  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

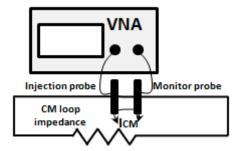

| Fig. 2. | Common-mode loop impedance measurement setup for the dual current clamp method                                                                                                                          | 66  |

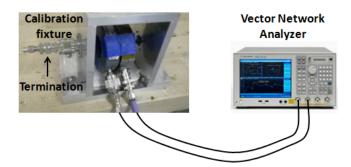

| Fig. 3. | Setup for calibration using a calibration fixture.                                                                                                                                                      | 67  |

| Fig. 4. | Simple passive system with a ferrite core.                                                                                                                                                              | 67  |

| Fig. 5. | Prediction of ferrite influence on CM loop impedance for simple passive structu                                                                                                                         |     |

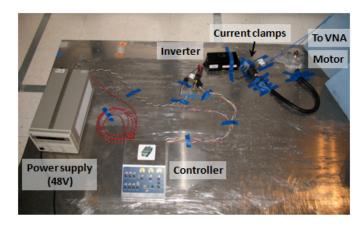

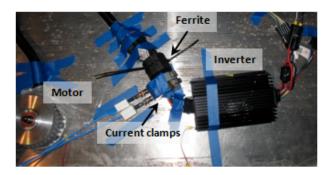

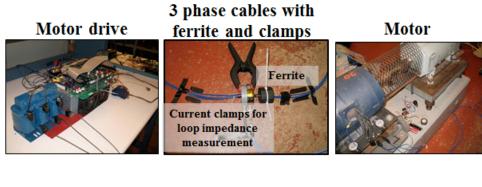

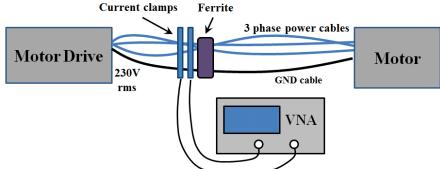

| Fig 6   | Measurement setup for real active power inverter system.                                                                                                                                                |     |

| -       | Placement of DCC current clamps and the broad band ferrite.                                                                                                                                             |     |

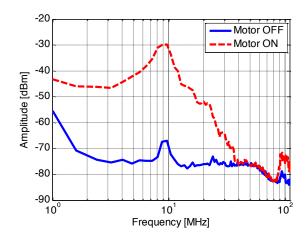

| -       | CM current when the motor is on and off.                                                                                                                                                                |     |

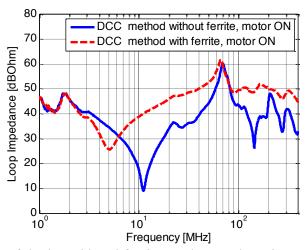

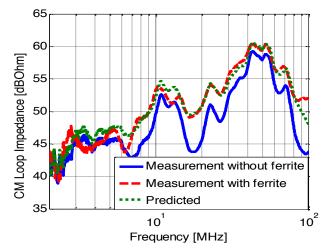

| -       | . Influence of the broad band ferrite on the CM loop impedance of the system                                                                                                                            |     |

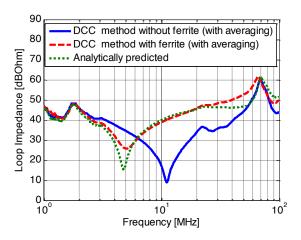

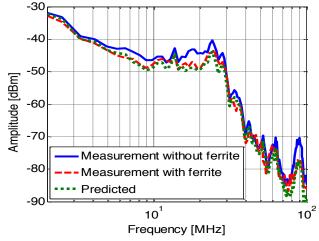

| -       | ). Measured and predicted common mode impedance with an added ferrite                                                                                                                                   |     |

|         | . Measured and predicted common mode current with an added ferrite.                                                                                                                                     |     |

| PAPE    |                                                                                                                                                                                                         | , 1 |

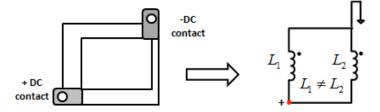

| Fig. 1. | A power system with a power cable bundle using a ferrite choke.                                                                                                                                         | 75  |

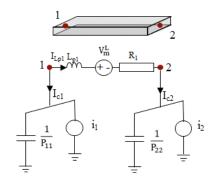

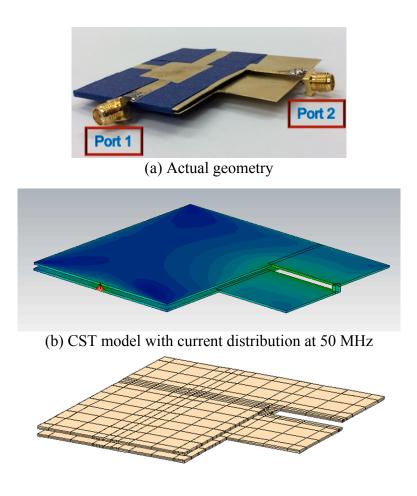

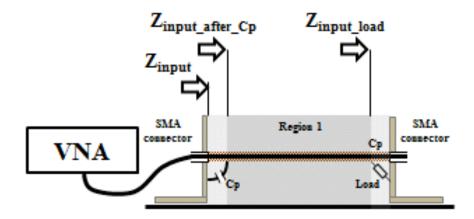

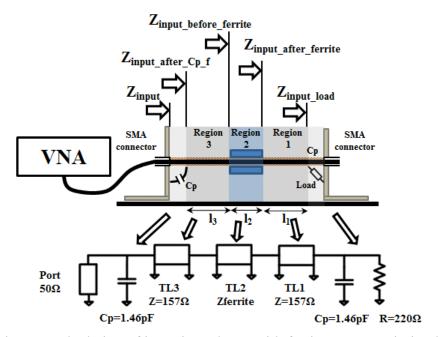

| Fig. 2. | Simplified structure of the system under test: (a) representation of the system<br>as a conductor over a return plane connecting a source and load, and (b) an<br>equivalent circuit for the structure. | 77  |

| Fig. 3. | Calculation of the inductance per unit length of the transmission line through the ferrite choke.                                                                                                       |     |

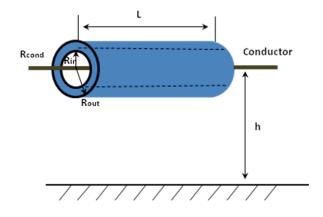

| Fig. 4. | Geometry associated with the ferrite over the return plane                                                                                                                                              | 81  |

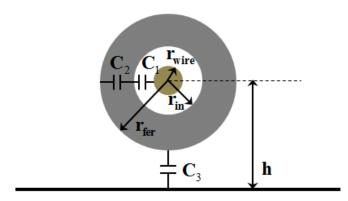

| Fig. 5. | Cross- section of the cable and ferrite over the return plane                                                                                                                                           | 83  |

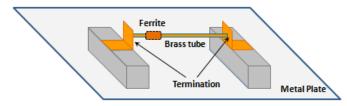

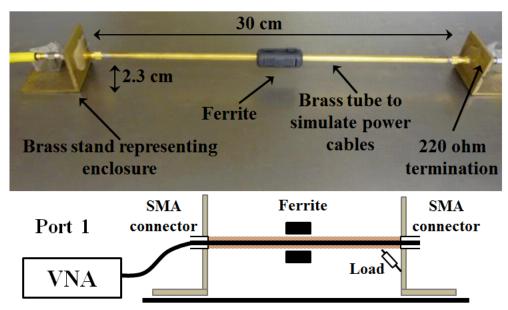

| Fig. 6. | Simplified test structure based on the real power system                                                                                                                                                | 85  |

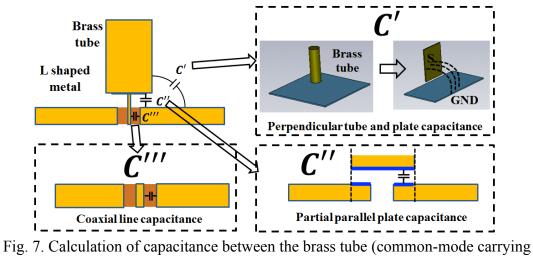

| Fig. 7. | Calculation of capacitance between the brass tube (common-mode carrying conductor) and the brass stand ("enclosure").                                                                                   | 87  |

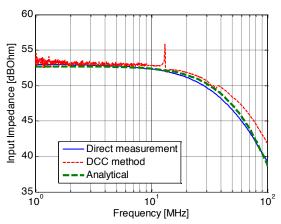

| Fig. 8. | Distinguishing input impedances of the structure.                                                                                                                                                       | 89  |

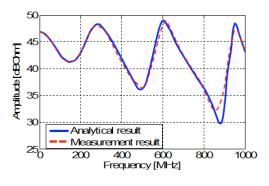

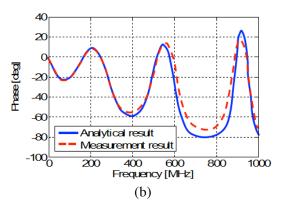

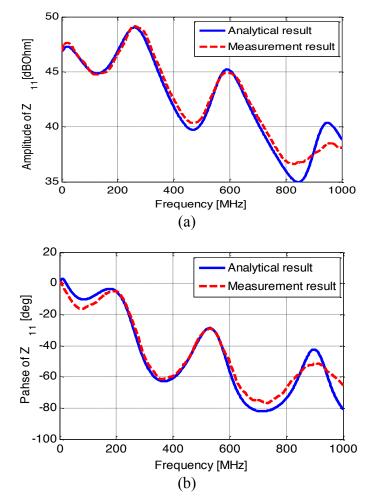

| Fig. 9. | Magnitude (a) and phase (b) of the measured and estimated input impedance of the test structure without a ferrite.                                                                                      | 90  |

| Fig. 10 | ). Calculation of input impedance with ferrite on transmission line                                                                                                                                     | 92  |

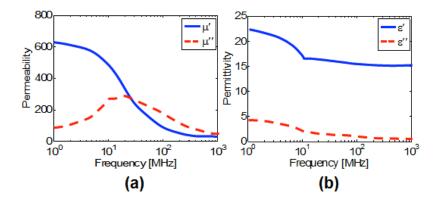

| Fig. 11 | . Permeability (a) and permittivity (b) of the ferrite choke.                                                                                                                                           | 92  |

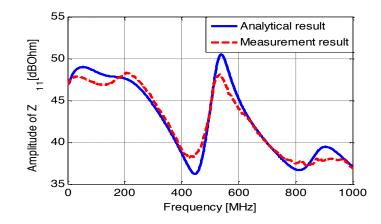

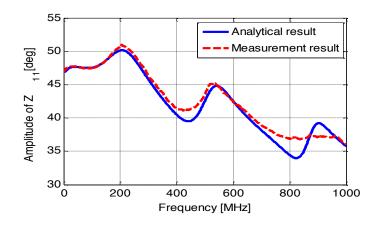

| Fig. 12 | 2. Magnitude (a) and phase (b) of the measured and estimated input impedance<br>of the test structure when the ferrite is placed close to the source                                                    | 93  |

| Fig. 13 | 8. Magnitude of the measured and estimated input impedance of the test structure when the ferrite is placed at the center of the brass tube                                                             | 94  |

| Fig. 14 | . Magnitude of the measured and estimated input impedance of the test<br>structure when the ferrite is placed at a height of 7.7 cm and close to the |    |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|         | source                                                                                                                                               | 94 |

| Fig. 15 | . Power system measurement setup.                                                                                                                    | 96 |

| Fig. 16 | . Measured and predicted CM impedance with an added ferrite                                                                                          | 97 |

| Fig. 17 | . Measured and predicted CM current with an added ferrite.                                                                                           | 97 |

# LIST OF TABLES

| Table                                                    | Page |

|----------------------------------------------------------|------|

| PAPER I                                                  |      |

| Table I 11                                               |      |

| Equations Describing DC link Capacitor Block Inductances |      |

| Table II                                                 | 15   |

| Values of Components within Equivalent Circuit           |      |

| Table III. Elements Responsible for Resonances           |      |

| PAPER II                                                 |      |

| Table I                                                  |      |

| Validation of simple double loop case                    |      |

| Table II                                                 |      |

| Validation of loop inductance and plate capacitance      |      |

| PAPER IV                                                 |      |

| Table I                                                  |      |

| Different Ferrites Under Test                            |      |

### **1. INTRODUCTION**

Electromagnetic Interference (EMI) is one of the major challenges to design of modern high power inverter/motor drive systems. EMI is mainly generated through fast switching of inverter outputs, leading to large dv/dt and di/dt components interacting with inverter parasitics to create conducted and/or radiated emissions. The switching times of the insulated gate bipolar transistors (IGBTs) in power inverters must be fast for efficiency and thermal reasons. The high values of dv/dt and di/dt cannot be easily reduced. The design of the inverter electronics, heatsink, harness and grounding structure, however, can be modified. Adding filtering or modifying the inverter parasitics can decrease the unwanted electromagnetic emissions.

While full wave modeling is accurate, applying full wave models to complex systems like power/inverters is difficult, as it requires substantial time and memory. More importantly, such simulations are often a "black box" that without additional simulations and effort generally do not help improve understanding of which parts of the system are responsible for a particular EMI problem and how to solve it. Many such systems also often contain non-linear elements that cannot be modeled easily with a full-wave solver and should be considered using circuit analysis. Thus development of a SPICE based model of the complex system is a better approach. This model should have straightforward correlation between system geometry and parasitic circuit elements. It can be used to better understand the physics behind the creation of common mode current in an inverter/motor system. Such a model can be obtained based on schematics, harness information, and the overall system layout (e.g. the IGBT, heatsink, and enclosure geometry). Parasitic inductive and capacitive elements inside the inverter are needed for this SPICE model.

One of the well-known methods to extract SPICE elements from complex geometries is the PEEC method, where a problem is transferred from the electromagnetic domain to the circuit domain. Generally with the PEEC approach many (sometimes thousands) of extracted parasitic L and C elements are obtained. This is too many elements for a basic understanding of the system, so some reduction is required. Some known model order reduction (MOR) techniques help to obtain an equivalent circuit representation, but these circuits are purely functional and do not provide physical insight into the device. Another approach is obtaining an equivalent model based on measurements or combination of measurements and full-wave simulations.

In this dissertation two approaches to obtain such model are presented: a measurement-based method and a method using PEEC followed by developed physicsbased model size reduction (PMSR) technique. The first method involves dividing the system into a number of subsystems and obtaining simple equivalent elements from step by step measurements. This method allows one to obtain rather simple equivalent model without 3D modeling. The second approach requires development of PMSR technique to collapse the many elements obtained using PEEC into a reasonable number of elements which can still be related directly to the physical geometry responsible for the parasitics. In both cases the resulting simplified model will have similar basic topology containing only a few circuit elements and the real geometry will be correlated to these elements. Both approaches are validated through experiments and full-wave modeling. Further the obtained SPICE models can be used to better understand the physics behind the creation of common mode current in an inverter/motor system.

Another contribution of the work is the introduction of a methodology to predict the effects of ferrite chokes on the common-mode impedance and common-mode current of active power electronics systems when the ferrite is placed on the cable harness. The method is based on combination of high frequency analytical ferrite choke model and dual current clamp measurement technique for common-mode loop impedance. Effectiveness of the approach is demonstrated on a real active power/inverter system.

The main contributions of the dissertation include:

A methodology is developed to obtain relatively simple measurement-based SPICE models of complete power systems with clear correlation between system geometry and circuit elements (paper 1).

The methodology is validated on a real power inverter system up to 100 MHz (paper 1).

The equivalent model is analyzed to determine possible causes of radiated emissions (paper 1).

Recommendations are made based on the SPICE model to mitigate main resonances of the system (paper 1).

Effectiveness of proposed countermeasure techniques is demonstrated (paper 1).

Prediction of reduction in radiated emissions with presence of mitigation techniques is shown (paper 1).

A methodology is developed to obtain simple physics-based SPICE circuit from large PEEC models, where there is a clear correlation between geometry and parasitic circuit elements (paper 2).

With the method the number of inductors and capacitors is reduced separately, which helps to ensure physicality of the reduced model (paper 2).

An approach to deal with model reduction containing a closed loop is introduced (paper 2).

Methodology is applied to a simple power electronics component (paper 2).

Error estimation of the reduced model is done using port impedance (paper 2).

The approach can potentially allow an easy combination of both the macro- and micro-models (paper 2)

A methodology is developed to predict effect of a ferrite choke on common-mode current and common-mode impedance of power inverter systems (paper 3, paper 4).

A high frequency analytical model of a ferrite choke is derived using transmission line model quasi static approximation (paper 4).

Application of the dual current clamp for predicting impact of a ferrite is considered (paper 3, paper 4)

The method is validated on simple passive structures and active real power inverter/motor system. The prediction agrees with measurements within 3 dB (paper 3, paper 4).

#### PAPER

# I. A MEASUREMENT-BASED MODEL OF THE ELECTROMAGNETIC EMISSIONS FROM A POWER INVERTER

# Natalia Bondarenko, Zhai Li, Bingjie Xu, Guanghua Li, Tamar Makharashvili, David Loken, Phil Berger, *Member, IEEE*, Tom Van Doren, *Fellow, IEEE*, Daryl Beetner, *Senior Member, IEEE*

*Abstract*—Rapidly switching semiconductors in modern high power inverter/motordrive systems generate fast changing voltages and currents which may result in unwanted emissions. While models of power inverters have been built in the past to predict emissions, they are typically "black box" models where the cause of and solution to emissions problems is difficult to analyze. To improve inverter system design strategies, a detailed measurement-based SPICE model of a power inverter system was built in which there is a straightforward correlation between system geometry and parasitic circuit elements. This model was validated through measurements. The model was able to predict transfer characteristics between ports of the inverter within 4 dB from 100 kHz to 100 MHz. Once built, this model was used to identify structures responsible for resonances and to determine possible improvements of the power inverter design to reduce emissions. Measurements of S21 and radiated emissions after adding these improvements demonstrated that they were able to reduce emissions by 10-20 dB, thus confirming the accuracy of the model and its ability to improve understanding of emission mechanisms and to guide development of emissions reduction strategies.

*Index Terms*— Electromagnetic interference (EMI), electromagnetic modeling, parameter estimation, variable speed drives, electromagnetic radiation

#### I. INTRODUCTION

Electromagnetic Interference (EMI) is a major challenge to design of modern high power inverter/motor drive systems. EMI is mainly generated through fast switching of inverter outputs. Large dv/dt and di/dt components in the output interact with inverter parasitics to create conducted and/or radiated emissions [1]-[3]. The switching times of the insulated gate bipolar transistors (IGBTs) in power inverters must be fast for efficiency and thermal reasons, so the high values of dv/dt and di/dt cannot be easily reduced. The design of the inverter electronics, heatsink, harness and grounding structure, however, can be modified and filtering can be added to reduce electromagnetic emissions. Ideally, the impact of such mitigation techniques could be evaluated early in the design process through accurate models of the system.

While full wave models are accurate, applying full wave models to complex systems like a power inverter is difficult, as they require substantial computational time and memory [4], [5]. More importantly, such full wave models are often a "black box" that does not directly show which parts of the system are responsible for a particular EMI problem or how to solve the problem without additional simulations and effort. Models of inverters also often require non-linear elements that cannot be modelled easily with a full-wave solver and should be considered using circuit analysis. An equivalent SPICE based model which includes the system parasitics is a better approach, since it can give a straightforward correlation between system geometry and parasitic circuit elements and the resulting common-mode currents.

A SPICE based model can be obtained from schematics, harness information, and system layout (e.g. the IGBT, heatsink, and enclosure geometry). Several methods are available for extracting parasitic SPICE parameters from a complex geometry [6]-[8]. Many of these methods are based on 3D finite-element analysis [4],[5] or the partial element equivalent circuit (PEEC) method [9]-[12]. The output from finite-element analysis is not typically a simple SPICE circuit but a black box measure of circuit characteristics, for example the S parameter values between two ports. The PEEC approach provides a SPICE model of parasitics in terms of RLGC matrices, but may require hundreds or thousands of elements to represent even a simple geometry, which is too many for an intuitive understanding of how the circuit works. Model order reduction (MOR) techniques may help provide an equivalent circuit representation [13], but these circuits are purely functional and, like the S parameters, do not provide significant physical insight into the inner workings of the device. In [14], equivalent SPICE circuit elements are determined from Z-parameters found from 3D full-wave models. While the

resulting circuit is useful, modelling the complete power inverter (whose precise geometry may be unknown) requires substantial time and effort.

Parasitics may also be obtained through measurements or a combination of measurements and full-wave simulations. One approach is to use Time Domain Reflectometry (TDR) and transmission line theory to extract parasitics [15]. This approach is limited by the ability to accurately extract parasitics which may be much larger or smaller than 50 ohms. Impedance measurements were similarly used in [16] to determine equivalent circuits for some inverter modules. In another recent study [17] a measurement-based inverter model was presented, where scattering parameters were converted to equivalent common mode (CM) and differential mode (DM) impedances. Although the model is based on measurement, it is still a "black box" model of the inverter which does not represent specific parasitics. A study is presented in [18] which develops a low-frequency parameter-based model of induction machines using DM and CM impedance measurements. A number of other studies [4], [19]-[20] have demonstrated the usefulness of using a combination of measurements and simulations.

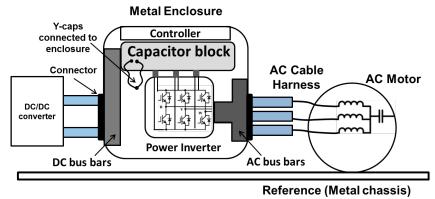

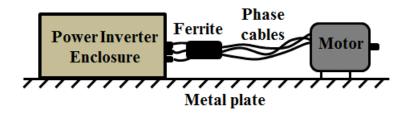

Existing studies lack the development of a simple model for a complete power inverter system and do not demonstrate how to use this model to reduce radiated emissions. A methodology is presented in the following paper to build a rather simple, yet accurate, equivalent model of a real power inverter which has a clear correlation between parasitic circuit elements and system geometry. The method is applicable up to 100 MHz, which is above the frequency where problems are typically seen in power inverter systems, and was the maximum frequency of interest specified by our industry partners. For this application, the power inverter and attached motor (Fig. 1) was divided into subsystems representing the DC cables, DC link capacitance block with DC bus bars, IGBT module, AC bus bars, AC cables, and motor/load. A simple equivalent model was built for each subsystem and validated through measurements. The subsystem models were assembled to create a model of the complete system. This relatively simple model was used to find the system components responsible for the most important resonances and then, based on the understanding of these resonances, to demonstrate how changes could be made to the system to mitigate these resonances. The effectiveness of the mitigation strategies was demonstrated through measurements of the output voltage and radiated emissions.

Fig. 1. Power inverter/motor system.

### II. CONSTRUCTION OF THE EQUIVALENT CIRCUIT

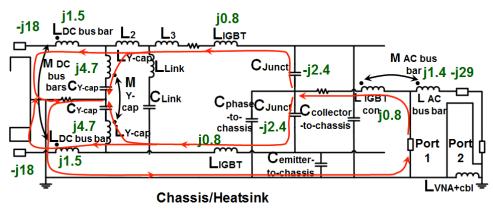

An example of the power inverter/motor system is shown in Fig. 1. The equivalent circuit should include information about the cables (both DC and AC), parasitic inductances of the Y capacitors, parasitic inductances due to the DC link capacitor, inductances due to the terminals of the IGBT module, the capacitances between the IGBT and chassis, and the high-frequency impedance of the motor (or dummy load). As the Pulse Width Modulated (PWM) inverter structure is symmetrical, it is only necessary to model the behaviour of one inverter leg.

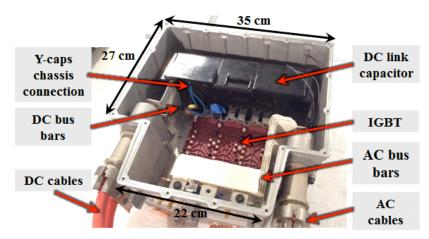

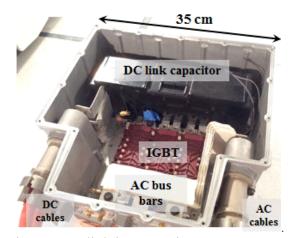

The inverter under study is housed in a metal enclosure (Fig. 2) and generally well shielded from its environment. All power cables going in or out of the enclosure are shielded, with the shields making a good 360° connection at the enclosure. The one location where there is a good potential to drive parasitic antennas and cause radiated emissions is at the connection between the AC cables and the motor. While a good 360° connection of the shield at this location may be used, in many cases a long pigtail is used to connect the shield to the motor housing. Even with a good connection, the RF shielding within the motor itself is highly variable. Because the cable connection to the motor is the only place where emissions may reasonably be generated by this well-shielded device, the voltage between the inner conductor and shield of the AC cable at

the connection to the motor was used as a reference when proposing schemes to mitigate emissions. Later measurements confirm the suitability of this approach.

Fig. 2. Power inverter enclosure with DC link capacitor, DC bus bars, IGBT and AC bus bars.

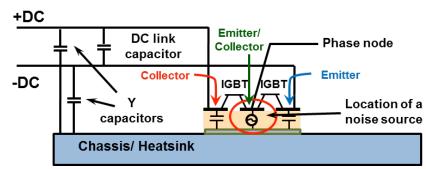

A simple model of the IGBT is illustrated in Fig. 3. For each IGBT phase leg there are parasitic capacitances from the emitter to chassis, from collector to chassis and from phase (the emitter/collector node) to chassis. Most emissions are expected to result from the voltage between the phase node and chassis, since the switching occurs at this node and this common-mode voltage can directly drive a voltage between the center conductor and shield of the AC cable at the motor connection.

Fig. 3. Location of the main "noise" source inside the IGBT module.

The parasitic antenna that drives emissions is primarily composed of the shields of the cables and the motor and inverter housings. The characteristics of this antenna cannot be changed significantly during testing, since standards specify the placement of these components. Since this antenna is driven primarily by the voltage at the end of the AC cable, and this voltage results primarily from the voltage between the IGBT phase node and chassis, the value of S21 between the phase-node-to-chassis voltage and the center-conductor-to-shield voltage of the AC cable connection to the motor is critical to understanding and mitigating emissions mechanisms.

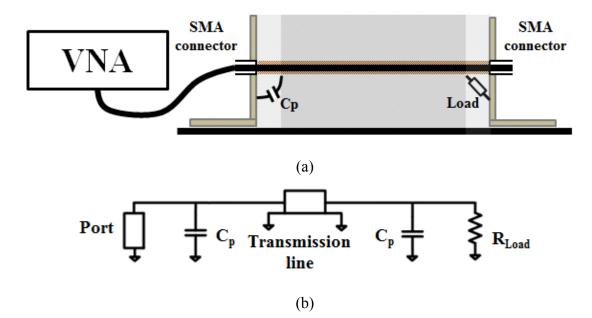

## A. AC and DC cables

The DC and AC cables were modelled as transmission lines. This model requires information like the characteristic impedance, dielectric constant of the insulation and loss tangent. The datasheet provided only geometrical information, so measurements were made with a Time Domain Reflectometer (TDR) and a Vector Network Analyzer and parameters were determined from the measurements. Fig. 4 shows a comparison of the predicted and measured impedance, where simulations were performed using a transmission line model of a 1.86 m long cable with  $Z_0 = 8.56 \Omega$ ,  $\varepsilon_r = 2.65$ , and loss tangent of 0.108. A 4 nH parasitic inductance was placed in series with the cable to model the SMA connector used to make the measurement.

Fig. 4. Validation of the transmission line model for the open ended DC cable. Measured values are shown with a solid line and simulated values with a dashed line.

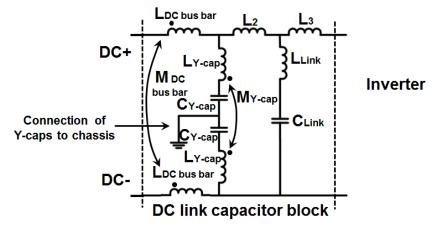

The DC link capacitor block consists of a DC link capacitance (with nominal C=1028  $\mu$ F) and two Y-capacitances (with nominal C=0.98  $\mu$ F), as illustrated in the model shown in Fig. 5. This circuit template was constructed with some information of circuit geometry. Parameter values could then be filled in later through measurements. While inductance is a property of loops, an approximate model was constructed using partial inductances. The inductances L<sub>DC bus bar</sub> and M<sub>DC bus bar</sub> are due to the bus bars of the capacitor block, L2 and L<sub>Link</sub> are parasitic inductances associated with the link capacitor, L<sub>y-cap</sub> and M<sub>y-cap</sub> are associated with the Y-capacitors, and L3 is the inductance due to the output of the capacitor block (where it connects to the IGBT module). The simple model without mutual inductances was used initially, but later it was found useful to split L<sub>DC bus bar</sub> between the DC+ and DC- buses, and to include the mutual inductance between the buses. The mutual inductances help to differentiate between the impedance seen by common mode and differential mode currents.

### B. DC Link

Measurements of the DC link capacitor block were performed with the capacitor block alone and also with the block connected to the DC cable to determine the values of the parasitic inductances due to Y-capacitors and DC bus bars. A number of Z11 and Z22 measurements were performed while other ports were made open or short. The value of Z11 looking into the Y-capacitors was also obtained by measuring impedance between one of the Y-capacitor connections and the chassis. The values of the parasitic inductances could not be determined from a single measurement, but could be determined mathematically from the set of measurements. The measurements and associated equations are illustrated in Table 1, where parameters used in the equations are given in Fig. 5.

| Equations Describing DC link Capacitor Block Inductances                                  |  |  |

|-------------------------------------------------------------------------------------------|--|--|

| Equation                                                                                  |  |  |

| $L_{@1MHz} \approx L_{DC \ cable} + L_{DC \ bus \ bar} + \frac{L_{Y-cap} + M_{Y-cap}}{2}$ |  |  |

| $L_{@2MHz} \approx L_{DC \ cable} + L_{DC \ bus \ bar} + L_2 + L_{Link}$                  |  |  |

| $L_{@10MHz} \approx 2(L_{Y-cap} - M_{Y-cap}) + L_2 + L_{Link}$                            |  |  |

| $L_{@14MHz} \approx L_3 + L_{Link} \parallel (L_{DC \ bus \ bar} + L_2)$                  |  |  |

| $L_{@11MHz} \approx L_3 + L_{Link}$                                                       |  |  |

|                                                                                           |  |  |

Table I

Fig. 5. Schematic of DC link.

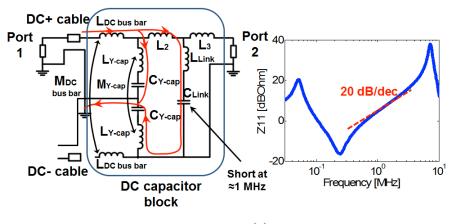

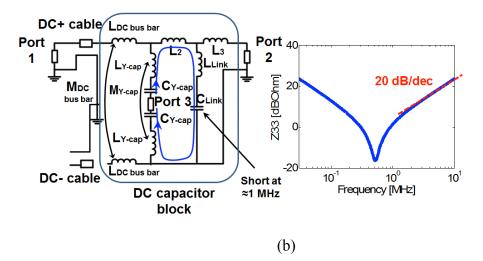

Example measurements are demonstrated in Fig. 6. In the measurement in Fig. 6a, Port 1 is at the beginning of the DC+ cable and Port 2 is at the output of the DC capacitor block. The DC- cable is not connected. The Y-capacitors are connected to the chassis. The shields of both DC cables are connected to the enclosure. At about 1 MHz the capacitance due to the DC block ( $C_{Link}$ =1028 µF) looks like a short, the current returns to the chassis through both Y-capacitors, and the input impedance is equivalent to a 272 nH inductor. Tracing the currents during the Z11 measurement at this frequency gives:

$$L_{1MHz} \approx L_{DC+cable} + L_{DC\ bus\ bar} + \frac{L_{Y-cap} + M_{Y-cap}}{2} \approx 272\ \text{nH}.$$

(1)

An additional measurement of the  $L_{Y-cap}$  inductance is made by breaking the connection of one Y-capacitor to the chassis, and measuring the impedance looking into the Y-capacitor break, as shown in Fig. 6b. Tracing this impedance at10 MHz gives,

$$L_{10MHz} \approx 2\left(L_{Y-cap} + M_{Y-cap}\right) + L_2 + L_{LINK} \approx 214 \ nH \ . \tag{2}$$

Using these equations (along with other measurements), the mutual inductance  $M_{Y-cap}$  was found to be 108 nH, and the self inductance associated with each Y-capacitors to be about 150 nH. As demonstrated by the relative size of  $M_{Y-cap}$  and  $L_{Y-cap}$ , the mutual inductance could not be ignored. The importance of mutual inductances between busses was noted on several occasions while developing the model.

Fig. 6. Example measurement made to obtain the DC link capacitor block parasitics (a) from connected DC+ cable, DC link and Y-caps connected to chassis, at 1 MHz and (b) from impedance looking into Y-caps at 10 MHz.

#### C. IGBT

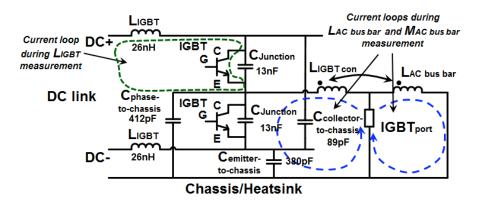

To model the IGBT module, two Z11 measurements were made looking into the output of the module while the input was open or short. These measurements were used to determine the IGBT junction capacitance and the loop inductance due to the IGBT bus bars (provided this inductance is not dominated by the inductance of the probe used to make the measurement). The measured junction capacitance across both the pull-up and pull-down IGBTs when the DC- and DC+ terminals were shorted was about 13 nF, as illustrated in Fig. 7. The IGBT bus bar inductance was determined from a Z11 measurement looking into the IGBT when a return was provided using a large metal plate. This measurement gives an estimate of the loop inductance associated with one phase leg of the IGBT module. This inductance was found to be approximately 26 nH. The measured parasitic capacitance from the phase node to chassis (across the direct bonded copper substrate) was measured using an LCR meter. The measured value was about 850 pF. This capacitance is a distributed capacitance (from collector to chassis, from emitter to chassis and from the phased node to chassis) as shown in Fig. 3. From the size of the plates collector, emitter, and phase nodes plates in the IGBT, and the measured total capacitance, the size of each parasitic capacitances was estimated to be 412 pF, 380 pF and 89 pF, as shown in Fig. 7 [16]. As will be demonstrated later, it is the total value of capacitance, 850 pF, which is critical to resonances in the circuit.

Fig. 7. Equivalent model of one phase of the IGBT module, IGBT connection and AC bus bar.

#### D. AC bus bars

To estimate the loop inductance associated with the AC bus bars, which carry current from the output of the IGBT to the AC cables (Fig. 2), a measurement of Z11 looking into the output of the IGBT module was made while its input was open and the end of AC bus bars was shorted to the enclosure. This setup creates two current loops: one from the input port through the AC bus bars and chassis and another loop from the input port through the IGBT connection, through the parasitic capacitance to the chassis as indicated in Fig. 7. These currents must return to Port 1 through a metal connector approximately 2 cm long (connecting the SMA connector to the chassis). The shared return path through the connector creates a large mutual inductance between the loop associate with the AC bus bar and the loop associated with the IGBT connection. The partial self-inductances were directly extracted from Z11 and are about 130 nH and 25 nH respectively. The mutual term was approximated from a measurement of S21 for a port between the phase node to chassis and a port at the end of the AC cable. As the length of the metal connector is about 2 cm, the mutual inductance should be around 10-20 nH. The mutual inductance was found to be about 12 nH by comparing the simulated and measured values of S21 while tuning the mutual inductance.

### E. Complete system

The model of the complete circuit was assembled from the models of the individual subsystems, as shown in Fig. 8. This model is for a single phase leg of the IGBT and a single AC cable. The motor is not shown, since measurements determined its impedance was too large to be significant over the frequency band of interest. The values of the circuit parameters are shown in Table II.

#### **Chassis/Heatsink**

Fig. 8. Complete equivalent circuit model. Port one: between phase node and chassis, Port 2: between inner and outer conductors at the end of the AC cable.

| Component                             | Value  | Component                             | Value   |

|---------------------------------------|--------|---------------------------------------|---------|

| $L_{DC\ bus\ bar}$                    | 50 nH  | $M_{\scriptscriptstyle DC\ bus\ bar}$ | 40 nH   |

| $C_{Y-cap}$                           | 700 nF | $L_{Y-cap}$                           | 150 nH  |

| $M_{_{Y-cap}}$                        | 108 nH | $L_2$                                 | 2 nH    |

| $L_3$                                 | 12 nH  | $C_{Link}$                            | 1028 uF |

| $L_{Link}$                            | 10 nH  | $C_{Junction}$                        | 13 nF   |

| L <sub>IGBT</sub>                     | 26 nH  | $C_{\it phase-to-chassis}$            | 412 pF  |

| $C_{collector-to-chassis}$            | 89 pF  | $C_{emitter-to-chassis}$              | 380 pF  |

| $L_{IGBT\ con}$                       | 25 nH  | $L_{\scriptscriptstyle AC\ bus\ bar}$ | 130 nH  |

| $M_{\scriptscriptstyle AC\ bus\ bar}$ | 12 nH  |                                       |         |

Table II. Values of Components within Equivalent Circuit

#### **III. VALIDATION OF COMPLETE MODEL**

Each subsystem was modelled and characterized separately because accurate models of these systems cannot reasonably be obtained using only measurements of the complete system. Characterizing the subsystems separately, however, assumes that the parasitic coupling between subsystems is small. This assumption is reasonable because of the distances between components, but must be verified through measurements of the complete, assembled system.

Fig. 9. Measurement setup used to validate overall inverter model.

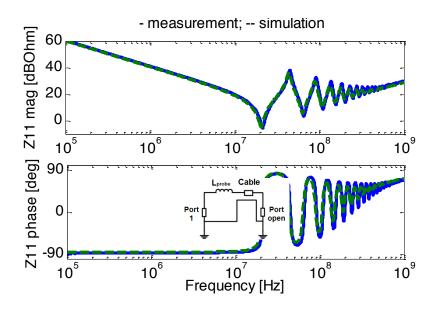

The model was validated, in part, by comparing the input impedance and/or Sparameters at ports of both the individual subsystems as well as the overall model. The complete circuit model was validated using the experimental setup shown in Fig. 9. Port 1 was placed between the phase node and chassis (at the source of switching) and Port 2 was placed between the inner and outer conductors at the end of the AC cable (where the noise is most likely to drive radiated emissions). Comparisons of the simulated and measured transfer characteristics between these ports are shown in Fig. 10 from 100 kHz to 1 GHz. Measured and simulated values of Z11 and Z22 are presented in Fig. 11. The model describes behavior of the system at these ports within 4 dB from 100 kHz to 100 MHz. It should be noted that there is some difference in the level of S21 for frequencies higher than 100 MHz, which may be caused by parasitic couplings between the subsystems, which were not included in the model, but that become important at those frequencies.

Fig. 10. Magnitude and phase of S21 between the phase node and the output of the AC cable.

Fig. 11. Magnitude of Z11 looking into the phase node and Z22 looking into the AC cable output.

#### IV. CORRELATION OF SYSTEM RESONANCES WITH GEOMETRY

A significant advantage of a simple model is that one can more easily understand the causes of specific behaviors and how to modify the system to improve this behavior. Resonances within the inverter cause peaks in the transfer characteristics from the phase node to the output of the AC cable, which may also cause peaks in the radiated emissions. If one can understand which components or current paths are involved in these resonances, one can better understand how to remove or mitigate their effect.

The most critical resonant frequencies associated with this power inverter system are around 5 MHz, 10 MHz and 30 MHz, as seen in the values of S21 in Fig. 10 and later in measurements of radiated emissions (Fig. 18). When Port 1 is between the phase node and chassis, Z11 and S21 are closely related since both are highly dependent on the impedance looking into the IGBT. Since Z11 is easier to relate to inductance or capacitance, Z11 was studied to identify causes of resonances. Fig. 12 is marked with a value of inductance or capacitance that *might* be associated with each portion of the curve. These approximations were used to help guide the analysis.

Fig. 12. Magnitude of Z11 and corresponding value of parasitics.

Fig. 13. Analysis of current path for one problematic frequency (5 MHz).

To illustrate the methodology used to determine the current path and elements responsible for each resonance, consider the resonance at 5 MHz. To help find the elements responsible for the resonance, the impedance of each circuit element at 5 MHz was determined as shown in Fig.13. At 5 MHz the impedance of the DC cable is about –  $j18 \Omega$ :

$$Z_{DCcable} = \frac{1}{j\omega C_{cable}} = \frac{1}{j2\pi f^* c_{p.u.l}^* l_{cable}} \approx -j18 \text{ ohm}$$

(3)

where  $c_{pul}$  is the capacitance per-unit-length of the cable and  $l_{cable}$  is its length. The effective impedance of the two DC cables in parallel is about –j9  $\Omega$ . If the inductance due to DC bus bars ( $j2\pi f(L+M) \approx j3$  ohm) is included, the effective impedance for the DC cable and bus bars is about -j6  $\Omega$ . At 5 MHz the effective impedance associated with the two Y-capacitors in parallel is about j6  $\Omega$ :

$$Z_{Y-caps+} = j\omega(\frac{L_{y-caps}}{2} + M_{Y-caps}) \approx j6 \text{ ohm.}$$

(4)

While other impedances may also play a role, the impedances of the DC cable capacitance and Y-cap inductance are sufficiently close to reliably identify these components as responsible for the resonance around 5 MHz.

A similar analysis was conducted at other resonant frequencies. The elements determined to be responsible for critical resonances are listed in Table 3.

| Frequency        | Responsible elements                                 |

|------------------|------------------------------------------------------|

| Below 2 MHz      | IGBT collector to emitter capacitances (26 nF        |

|                  | total)                                               |

| 2 MHz resonance  | Collector to emitter capacitances of IGBT and        |

|                  | inductance of Y-caps                                 |

| 5 MHz resonance  | Capacitances of DC cables and inductance of Y-       |

|                  | caps                                                 |

| 9 MHz resonance  | Transmission line resonance of DC cables and         |

|                  | additional series inductance                         |

| 10 MHz resonance | Inductance of the DC bus bars and cable              |

|                  | resonating with the capacitance looking toward the   |

|                  | AC bus bar and cables                                |

| 30 MHz resonance | IGBT capacitance between the DC+, DC-, and           |

|                  | phase nodes to the chassis (881pF) and the effective |

|                  | inductance of the AC + DC cables + bus bars          |

# V. MITIGATION OF SYSTEM RESONANCES

The impact of resonances within the inverter can be reduced by lowering their quality factor, or in some cases by changing the frequency at which they occur (thus moving them to a frequency which is unimportant). Some possibilities for mitigating the impact of resonances at 5 MHz, 10 MHz and 30 MHz were proposed and tested.

In general, to reduce the amount of energy coupled from the noise source between the phase node and chassis to the end of the AC cables, the overall magnitude of S21 between these ports should be reduced. The equivalent model shows that any significant increase in impedance of the AC cable will reduce S21 and thus should reduce emissions. For example, ferrites around the set of AC cables should decrease S21 since the commonmode impedance from the phase-node to motor will increase (a ferrite cannot be added to an individual cable because the high intended current would saturate the ferrite). Similarly, any significant decrease in the impedance between the AC cable and shield will reduce emissions. For example, adding a filtered connector (possibly with some losses) to the AC cable should decrease S21. While this suggestion was added for completeness, it should be noted that adding capacitance to any switching node is challenging due to the substantial current this capacitor may consume during operation.

Mitigation strategies depend on which components become important at specific frequencies. For example, at 5 MHz, where the resonance includes common-mode current through the Y-capacitors, a ferrite around the capacitor connections can be used to add loss and reduce the quality factor of the resonance. Similarly at 5 MHz, a lossy capacitive filter (connected with low inductance) could be added in front of the DC cables, with a larger capacitance than the DC cables, so the 5 MHz resonance occurs between the Y-capacitor inductance and the lossy capacitive filter, rather than the capacitance of the cables. Placing a lossy capacitor across the DC cables is reasonable since the high-frequency voltage on the DC cables is low. This resonance also involves common-mode current flowing through the DC bus-bars, which implies that a ferrite choke around the bus bars could also add loss to reduce this resonance.

A similar analysis was performed at other resonant frequencies to determine potential mitigation strategies. These strategies were tested as explained in the following section. Strategies included adding ferrite chokes to the Y-capacitors, DC bus bar, AC bus bar, and adding an RC filter to the DC cables and AC bus bar. A combination of these countermeasures (using a model of a real ferrite choke) was also investigated to demonstrate their overall impact. Individual strategies were tested through simulation. The best of the strategies were validated through measurements.

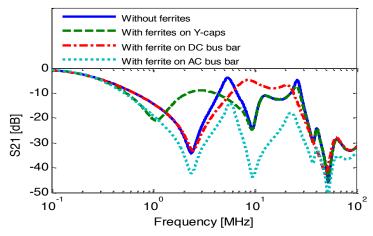

### A. Adding low frequency ferrite chokes

Low frequency ferrite chokes were added in simulation to the Y-capacitors, the DC bus bars and the AC bus bars. The ferrites were modeled as a simple parallel RLC circuits, with an associated mutual inductance with the circuit sharing the choke. Values

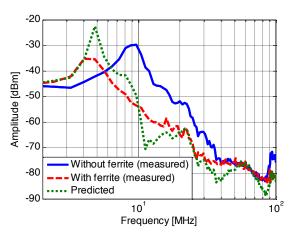

of R, L, and C were chosen similar to parameters for commercially available ferrites (R=20  $\Omega$ , L=12 uH and C=2 pF). The ferrite choke significantly reduced the peak values of S21 as demonstrated in Fig. 14.

Fig. 14. Change in S21 from added low-frequency ferrites.

### B. Adding RC filters

An RC filter was added to the DC and the AC bus bars. The capacitance of the filter was set so that the filter would generally have a lower impedance than the DC cable, and thus would impact resonant peaks that would normally be due to the DC cable. In this study it was found that adding an RC filter to the DC cables is more effective at 5 MHz at reducing the resonance peak than adding a low-frequency ferrite choke, especially when the capacitance value is higher than 1 nF. When the capacitance is increased, the peak of S21 is mitigated more effectively. The series resistance of the RC filter should be greater than about 2  $\Omega$ .

While the AC cables were not initially identified as part of the resonance at 5 MHz, adding the capacitive filter to the AC cables made them more important at lower frequencies, so the filter also had an impact at 5 MHz. In general, the larger the value of capacitance, the greater the reduction in emissions.

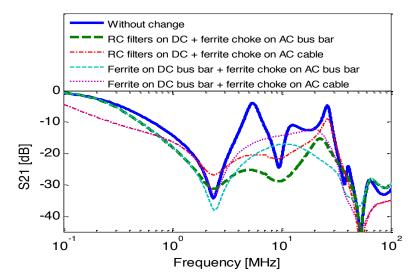

#### C. Combined mitigation strategies

The impact of a combination of the proposed mitigation strategies is shown in Fig. 15. The most effective reduction of emissions was obtained when RC filters (C=50 nF, R=10  $\Omega$ ) were added between the DC cables and the shield and a low-frequency ferrite choke (C=60 pF, L=12 uH and R=38  $\Omega$ ) was added to the AC bus bars. This strategy was able to reduce values of S21 by 10-20 dB at critical resonant frequencies.

Fig. 15. Predicted effect of combined countermeasures on S21.

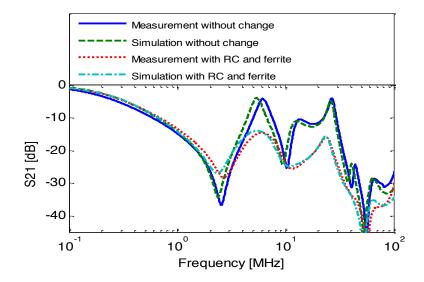

### D. Validation of mitigation techniques

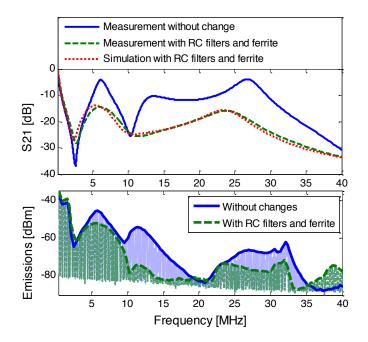

Two of the mitigation techniques discussed above were applied to the real system. Specifically RC filters (C=56 nF, R=13  $\Omega$ ) were added to the DC bus bars and a ferrite choke (high frequency ferrite by Laird) was added to the AC bus bar. The ferrite was modelled as a parallel RLC circuit (60  $\Omega$ , 0.35 uH, 0.1 pF), which was found from datasheet and measurement information. Comparison of measured and predicted values of S21 is shown in Fig. 16. The values match within a few decibels from 100 kHz to 100 MHz. Some disagreement is expected, particularly at high frequencies, because of difficulty in modelling the ferrite.

Fig. 16. Measured and simulated values of S21 when RC filters and a ferrite are added to the inverter.

### VI. RADIATED EMISSIONS

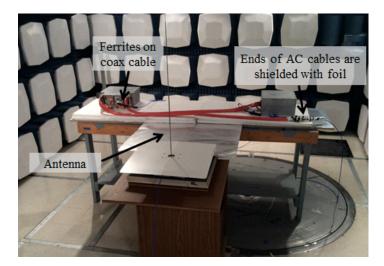

To further validate the model and demonstrate its effectiveness, changes in radiated emissions were predicted and measured while using the mitigation strategies. Radiated emissions were measured inside a semi anechoic chamber, as shown in Fig. 17. The IGBT phase node was driven with a rectangular pulse to mimic a switching noise source. The measurement setup is similar to the CISPR 25 standard. During measurement, the ends of the DC cables were shielded with foil, since in the real setup the shields are connected at 360 degree to the chamber wall and the ends are thus well shielded. Fig. 18 shows the predicted impact of the mitigation strategies on S21 and the measured impact on radiated emissions. The predicted changes in S21 correlate well with the changes in the radiated emissions up to about 35 MHz. The correlation is not perfect, as adding circuitry can change the interaction between the circuit and the parasitic radiating antenna (for example, changing the antenna resonance). While the model cannot predict such changes, as it does not include a model of the antenna, it still provides good guidance toward the impact of design changes on radiation.

Fig. 17. Setup used for radiated emissions measurements.

Fig. 18. Correlation between changes in S21 and radiated emissions.

### VII. GENERAL METHODOLOGY

While this paper demonstrates the development of a model for a specific power inverter, the methodology can be applied to more general power systems. The model can be developed in the following steps:

Step 1. Divide main system into subsystems for analysis.

Step 2. Estimate rough equivalent model based on parasitics associated with subsystem geometry (e.g. for cables – a transmission line model, for DC link - a combination of link capacitor, Y capacitors and some related bus bar inductances, etc.).

Step 3. Identify the location of the main noise source (for a power inverter usually between the phase node and chassis) and the most critical point where energy could be coupled to cables or other antenna structures (e.g. at the end of the AC cables). These locations are used as ports.

Step 4. Perform network parameters measurements on each subsystem to identify the values of parasitic R, L and Cs.

Step 5. Assemble complete model from equivalent models of all subsystems. Validate model with measurements and make minor reasonable adjustments as needed. During this step, it may be necessary to adjust for coupling between subsystems that was not accounted for in steps 2-4.

Step 6. Correlate circuit elements (representing real geometry components) of the model with the most important resonances of the system by tracing currents at these resonant frequencies.

Step 7. Use critical circuit elements at (or between) resonances to determine practical countermeasures to mitigate or reduce unwanted emissions.

Critical to this method is dividing the system into simple subcomponents that can be characterized with simple models, and then using the overall (simple) model to understand the root components involved at frequencies where problems occur.

### **VIII. CONCLUSIONS**

The development and analysis of a model for a complex power system was illustrated in this paper. While the methodology was applied to a power inverter system, it can be applied to other systems as well, where frequencies of interest are below 100 MHz. The equivalent model contains only the most important parasitic elements of the system. Each element can be clearly correlated with real system geometry. The model developed here was able to describe the impedance of a real inverter system well from 100 kHz to 100 MHz. Simulations of S21 for this system showed resonances at frequencies similar to those at which peak radiation has been observed from the real system.

A substantial advantage of a simple circuit representation is that it allows analytic determination of the possible causes of and mitigations strategies for emissions. This process is possible because the circuit is simple and because circuit elements are directly correlated with physical structures within the system. An analysis of the inverter studied here revealed the parasitics responsible for resonances associated with peak emissions. Recommendations to mitigate emissions were made based on the elements and current paths involved in these resonances. The most effective reduction of emissions was found using a combination of an RC filter added between the DC cable and chassis and a low-frequency ferrite choke added on the AC bus bars, which was validated by measurements.

100 MHz was the highest frequency of interest for the power inverter studied here. Below 100 MHz, there was no significant parasitic coupling between the subsystems, which allowed the subsystems to be characterized separately. At higher frequencies, parasitic coupling between systems might not be ignored. For example enclosure resonances may allow efficient coupling between components that are electrically far apart. Parasitic coupling between subsystems may also be an issue at low frequencies for other inverter systems. Parasitic coupling between subsystems was not explored in this paper. This possibility must be checked through validation measurements of the overall system impedances, and accounted for when needed.

While the proposed model does not directly predict the radiated emissions, since it does not include a model of the parasitic radiating antenna, it can still be used to understand and mitigate radiation problems. The validity of this approach was demonstrated by measurement which showed that it was able to effectively predict changes in radiated emissions as a result of adding filtering strategies to the design.

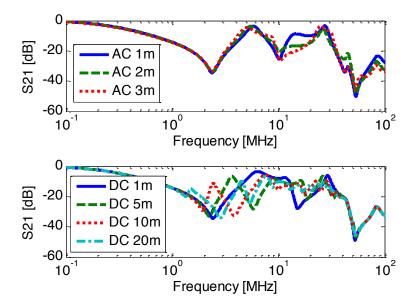

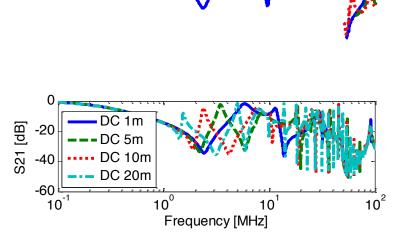

#### IX. APPENDICES

The length of the AC and DC cables may vary in the final application. The effect of different lengths of DC and AC cables was investigated. From a practical application standpoint the AC cables cannot be very long, while the DC cables can be quite long. Comparisons of values of S21 when the AC cable length varied from 1 m to 3 m and DC cables length varied from 1 m to 20 m are shown in Fig. 20. When the DC cables were 2 meter long and the AC cables lengths ranged from 1 to 3 meters, the length of the AC cable had an impact on the 10 MHz resonance, but did not have an effect on resonances at other frequencies. When the AC cables were 2 meters long, and the DC cable length varied from 1 to 20 meters, the length of the DC cables had a large impact on resonant frequencies, particularly at 5 MHz and below. While the resonant frequencies changed above 5 MHz as the DC cable length was changed, peak values of S21 above 5 MHz, however, were not changed much. Influence of DC cable length when the tangent loss value was 0.003, instead of 0.108 was also investigated. Overall, the loss of the cable becomes critical when the DC cable is long. A low loss cable generates many resonances at higher frequencies. If the loss is large, as it is for some commercially available high power cables, these resonances are largely damped by the cable loss. Similar mitigation/analysis strategies explored earlier should also apply to longer cables.

Fig. 19. Effect of AC and DC cable length on S21.

Fig. 20. Effect of DC cable length when the cable is low loss.

# X. REFERENCES

- E. Zhong, and T.A. Lipo, "Improvements in EMC performance of inverter-fed motor drives", IEEE Trans. Ind. Applicat., vol. 31, no. 6, pp. 1247–1256, 1995

- [2] L. Ran, S. Gokani, J. Clare, K.J. Bradley, and C. Christopoulos, "Conducted electromagnetic emissions in induction motor drive systems. Part I: Time domain analysis and identification of dominant modes", IEEE Trans. Power Electron., vol. 13, no. 4., pp. 757-767, Jul. 1998.

- [3] G. Skibinski, J. Pankau, R. Sladky, and J. Campbell "Generation, control and regulation of EMI from AC drives", in Conf. Rec. IEEE-IAS Annu. Meeting, 1997, pp.1571-1583.

- [4] S. Chen, T. W. Nehl, J.-S. Lai, X. Huang, E. Pepa, R. de Doncker, I. Voss, "Toward EMI prediction of a PM moor drive for automotive applications" in Proc. IEEE Appl. Power Electron. Conf., Miami, FL. 2003, pp.14-22.

- [5] "Inverter EMI modeling and simulation methodologies", IEEE Trans. Industrial Electronics, vol. 53, no. 3, Jun. 2006.

- [6] E. Falck, M. Stoisiek, and G. Wachutka, "Modeling of parasitic inductive effects in power modules" Proc. IEEE Int. Symp. Power Semiconductor Devices and IC's, Weimar, Germany, May 1997.

- [7] K. Xing, F. C. Lee, and D. Borojevic, "Extraction of parasitics within wire-bond IGBT modules" in Proc. IEEE Aplied Power Electronics Conf., 1998, pp.497-503.

- [8] J. L. Schanen, E. Clavel, and J. Roudet, "Modeling of low inductive busbar connections", IEEE Ind. Applicat. Mag., pp.39-43, Sep./Oct. 1996.

- [9] V. Ardon, J. Aime, O. Chadebec, E. Clavel, J-M. Guichon, and E. Vialardi, "EMC modeling of an industrial variable speed drive with an adapted PEEC method", IEEE Trans. Magnetics, vol. 46, no. 8, pp. 2892-2898, Aug. 2010.

- [10] V. Ardon, J. Aime, O. Chadebec, E. Clavel, and E. Vialardi, "MoM and PEEC method to reach a complete equivalent circuit of a static converter", EMC Zurich, Zurich, Switzerland, Jan. 2009.

- [11] A. Ruehli, "Equivalent circuit models for three-dimensional multiconductor systems", *IEEE Trans. Microwave Theory and Techniques*, vol. 22, no. 3, pp. 216-221, Mar. 1974.

- [12] M. Lionet, R. Prades, Y. lee Floch, E. Clavel, J.L. Schanen, and J.M. Guichon, "Improving conducted EMI forecasting with accurate layout modeling", in *IEEE Symposium on Embedded EMC, 2EMC, ESIGELEC*, Rouen, France, 2007.

- [13] T. Witting, R. Schuhmann, and T. Weiland, "Model order reduction for large systems in computational electromagnetics", *Linear Algebra and its Application*, vol. 415, no. 2-3, pp.499-530, 2006.

- [14] F. Traub, J. Hansen, W. Ackermann, and T. Weiland, "Generation of physical equivalent circuit using 3D simulations", *Proc. IEEE Int. EMC Symp.*, pp. 486-491, 2012.

- [15] H. Zhu, A. R. Hefner, and J. Lai, "Characterization of power electronics system interconnect parasitics using time domain reflectometer" in *Proc. IEEE PESC '98*, Fukuoka, Japan, May 17–22, 1998, vol.2, pp. 1937–1943.

- [16] L. Yang and W. G. H. Odendaal, "Measurement-based characterization method for integrated power electronics modules", *IEEE Trans. Power Electron.*, vol. 22, no. 1, pp. 54–62, Jan. 2007.