### Missouri University of Science and Technology Scholars' Mine

**Electrical and Computer Engineering Faculty** Research & Creative Works

**Electrical and Computer Engineering**

01 Sep 2008

### An Improved Cascaded H-Bridge Multilevel Inverter Controlled by an Unbalanced Voltage Level Sigma-Delta Modulator

Jingsheng Liao

Mehdi Ferdowsi Missouri University of Science and Technology, ferdowsi@mst.edu

Follow this and additional works at: https://scholarsmine.mst.edu/ele\_comeng\_facwork

Part of the Electrical and Computer Engineering Commons

### **Recommended Citation**

J. Liao and M. Ferdowsi, "An Improved Cascaded H-Bridge Multilevel Inverter Controlled by an Unbalanced Voltage Level Sigma-Delta Modulator," Proceedings of the IEEE Vehicle Power and Propulsion Conference (2008, Harbin, China), Institute of Electrical and Electronics Engineers (IEEE), Sep 2008. The definitive version is available at https://doi.org/10.1109/VPPC.2008.4677614

This Article - Conference proceedings is brought to you for free and open access by Scholars' Mine. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Research & Creative Works by an authorized administrator of Scholars' Mine. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# An Improved Cascaded H-Bridge Multilevel Inverter Controlled by an Unbalanced Voltage Level Sigma-Delta Modulator

Jingsheng Liao and Mehdi Ferdowsi, *Member*, *IEEE*Missouri University of Science and Technology, Rolla, MO, USA

Email: jl489@mst.edu and ferdowsi@mst.edu

Abstract—Multilevel inverters have been proven to be viable solutions for high-power automotive motor applications due to their high volt-ampere ratings. Cascaded H-bridge inverters are a promising breed of multilevel inverters which generally require several independent dc sources. Replacement of all but one of the dc sources with capacitors in cascaded H-bridge multilevel inverters, which leads to single-dc-source per-phase cascaded inverters, has recently gained popularity. However, very few efforts have been made to address the challenging problem of voltage regulation in the replacing capacitors. In this paper, applicability of a real-time voltage control technique named unbalanced voltage level sigma-delta modulation technique to provide voltage regulation across the replacing capacitors is examined. In addition, a new voltage ratio for the Hbridge cells is introduced, which simplifies the control tasks. Analytical and simulation results prove the effectiveness of the proposed scheme.

Keywords — Delta-Sigma modulator; H-bridge multi-level inverter; voltage regulation; spectrum analysis

### I. Introduction

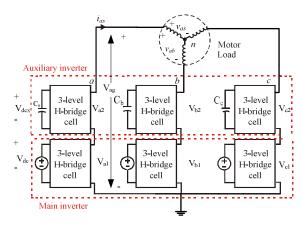

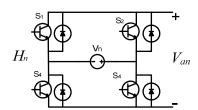

Multilevel inverters are mainly utilized to synthesize a desired single- or three-phase voltage waveform. They have found wide applications in automotive motor drives, static VAR compensators [1], and uninterruptible power supplies especially in high-power rating large vehicular motor drives (> 250kW), since high volt-ampere ratings are possible with these inverters. Their main advantages are low harmonic distortion of the generated output voltage, low electromagnetic emissions, high efficiency, capability to operate at high voltages, and modularity. In general, multilevel inverters are categorized into diodeclamped, flying capacitor, and cascaded H-bridge [2]. Fig. 1 shows the block diagram of a three-phase cascaded Hbridge inverter. As it can be observed, the inverter consists of main and auxiliary H-bridge cells in each phase. The structures of main and auxiliary cells are very similar. In Fig. 2, n is either 1 or 2 depicting the main or auxiliary inverters, respectively. As it can be seen, depending on the conduction status of four switches  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ , each converter cell can generate three different voltage levels of  $+V_n$ , 0, and  $-V_n$ . H-bridge cells in each phase are connected in series; hence, the synthesized per-phase voltage waveform is the sum of all individual cell outputs. The output voltage of phase a can be described by the following equation (see Fig. 1).

$$V_{ag} = V_{a1} + V_{a2} (1)$$

In early implementations [3-5], each H-bridge cell was fed by an independent dc source. Later, it was shown that only one cell needs to be supplied by a real dc power source and the remaining cells could be supplied with capacitors [6, 7]. However, studies show that voltage regulation of capacitors is not an easy task [8]. In previously reported works [6, 7], the ratio between the voltage of the main and auxiliary sources has been selected to be either 2:1 or 3:1, which leads to several limitations for the capacitor voltage regulation. In this paper, voltage ratio of 4:1, which simplifies the control task, is proposed and successfully implemented.

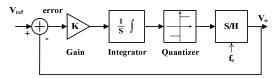

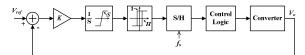

Furthermore, sigma-delta modulation (SDM) is proposed for voltage regulation across the replacing capacitors in the auxiliary cells. SDM has successfully been applied to synthesize desired voltage waveforms in discrete pulse modulated system such as resonant dc link inverters [9, 10]. The block diagram of a conventional two-level SDM is shown in Fig. 3. In Fig. 3,  $V_{ref}$  represents the desired output voltage,  $V_o$  is the synthesized output voltage, and  $f_s$  represents the sampling frequency of the system. The modulator encodes the reference signal

Figure 1. Block diagram of a three-phase cascaded H-bridge inverter

Figure 2. Circuit diagram of the main and auxiliary H-bridge cells

Figure 3. Block diagram of a two-level sigma-delta modulator

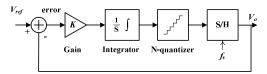

Figure 4. Block diagram representation of a multilevel sigma - delta modulator

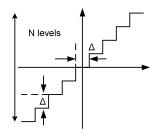

Figure 5. Static transfer characteristics of a uniform quantizer

$V_{ref}$  into a two-level output  $V_o$ . The output is fed back and compared with the reference signal through an integrator. Under normal operating conditions, the output signal has to track the input signal with zero average error.

Sigma-delta modulation technique and appropriate selection of voltage ratio in H-bridge cells are the main focus of this paper. In Section II, SDM and its principles of operation are briefly introduced. The use of SDM for driving multi-level converter with two DC sources and selection of parameters are discussed in Section III. Voltage ratio selection is discussed in Section IV. Application of SDM to single-dc-source cascaded H-bridge multilevel inverters is discussed in Section V. Simulation results are also presented in this section. Concluding remarks and overall evaluation of the proposed method are included in Section VI and Section VII.

### II. SIGMA DELTA MODULATION (SDM)

SDM can be extended to synthesize a multilevel waveform by replacing the binary quantizer with an N-level quantizer corresponding to the number of the levels of the multilevel inverter. The block diagram of the new SDM is depicted in Fig. 4.

Modulator design task requires selection of amplifier gain K, the saturation limits of the integrator block, and the sampling frequency  $f_s$ . A brief analysis of the system performance is done using the static transfer characteristics of a uniform quantizer as illustrated in Fig. 5.

Normally, the static transfer characteristics of the uniform N-level quantizer features step widths and step heights that are equal in magnitude this represents equal dc bus levels. As may be seen, each step width and the corresponding step height are of magnitude  $\Delta$ . For a normalized uniform quantizer with N number of levels the relation between N and A will be

Figure 6. Control block diagram of SDM driving multilevel converter

Figure 7. The output voltage which is good case

$$\Delta(N-1) = 2 \tag{2}$$

And the optimum choice of K and  $f_s$  will be determined by

$$K/f_s \le 1 \tag{3}$$

However, in this case, each voltage level is the same and the voltage of the capacitor cannot be balanced since the voltage drop during the discharging period is much larger than the voltage increase in capacitor voltage during the charging period. So an unequal voltage level Sigmadelta modulator will be used here.

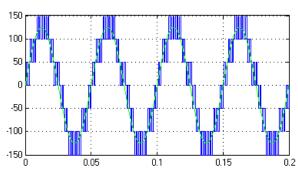

## III. USING SDM TO DRIVE A MULTI-LEVEL CONVERTER WITH TWO DC SOURCES

Previously, each H-bridge cell was fed by an independent dc source like a battery. The control diagram for this case can be shown as Fig.6. The priciples of operation is as follows: the reference voltage is a sinusoidal waveform, and the output voltage is tracking the reference voltage. The output of the modulator changes between the states +1 or -1 like a logic signal in time defined by the sampled frequency  $f_s$  and is used to drive the converter. The adjustable parameters are gain of the controller K, saturation limits of the integrator S, sampling frequency  $f_s$ , and threshold of the hysteresis loop H. Tracking characteristics of the synthesized output voltage depends on the appropriate selection of the above mentioned parameters. For instance, for H = 0.01,  $f_s = 5$ kHz,  $S = \pm 0.05$ , and K = 10 one would be able to get the output voltage that is depicted in Fig. 7. On the other hand, for H = 0.0005,  $f_s = 5$  kHz,  $S = \pm 0.5$ , and K = 10. The results are not satisfactory (see Fig. 8).

High sampling frequency is preferred to guarantee that the loop is fast enough to track the reference signal. Studies show that the sampling frequency needs to be at least 30 times of the frequency of the reference signal. For gain K and the saturation limits of the integrator block, simulations show that small values for gain K (e.g. 0.1) do not result in a good tracking response. However, values of 1 and larger are satisfactory. Saturation limits of the integrator block have a similar affect like gain K.

Figure 8. The output voltage which is bad case

Figure 9. Output voltage redundancy for 2:1 ratio

### IV. VOLTAGE RATIO SELECTION

As mentioned earlier, it has been proven that only one dc source per phase is needed in a multilevel inverter and others can be replaced with capacitors. In that case, the challenge is to regulate the voltage of the replacing capacitors [8]. Two approaches have been introduced in the literature which are redundancy [7], [11], [12], [13] and level reduction [6] methods. These two approaches both impose new limitations to the system. Redundancy method only works for a very limited load range [8] and level reduction method gives up on two of the output voltage levels, which leads to higher harmonic distortion.

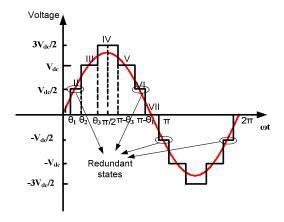

Usually, the voltage ratio of the main and auxiliary inverters is selected to be 2:1 [7]; therefore, output voltage has only seven levels, as depicted in Fig. 9. In this case,  $V_{dc}$  is the voltage level of the main cell and  $V_{dc}/2$  is that of the auxiliary cell.

Based on Fig. 9, one fourth of a period could be divided into the following subintervals

$0 < \omega_1 < \theta_1$  no Desired output voltage(V) charge capacitor or  $\theta_1^{V_c+V_c}$   $\theta_2$ capacitor charge or discharge depending on the capacitor voltage no capacitor charge itor discha no capacitor discharge VI. π -νθ  $-< \omega t < \pi - \theta_1$ capacitar diarge or discharge depending on the capacitor valtage

VII.  $\pi - \theta | < \omega t < \pi$  no capacitor charge or discharge Output voltage for 4:1 ratio ( $V_{dc} = 4 * V_{dcx}$ )

In order to balance the capacitor voltage, period IV should be very short otherwise the capacitor voltage will decrease continuously since discharging times will be longer than charging times [8]. To overcome this disadvantage, voltage ratio of 4:1 is proposed, as depicted in Fig. 10. In this case, there is no redundancy and therefore output voltage has nine levels. Capacitor is discharged when output voltage is at level 1 while it is charged when output voltage is at level 3. Therefore one fourth of a period could be divided into the following subintervals

no

capacitor

charge

or

$0 < \omega t < \theta 1$

discharge (level 0)

discharge (level 0)  $\theta 1 < \omega t < \theta 2$ capacitor discharge (level 1) III.  $\theta 2 < \omega t < \theta 3$ capacitor charge (level 3) IV.  $\theta 3 < \omega t < \theta 4$ capacitor charge or discharge (level 4) V.  $\theta 4 < \omega t < \pi - \theta 4$ capacitor discharge (level 5) VI.  $\pi - \theta 4 < \omega t < \pi - \theta 3$ capacitor charge discharge (level 4) VII.  $\pi - \theta 3 < \omega t < \pi - \theta 2$  capacitor charge (level 3) VIII.  $\pi - \theta 2 < \omega t < \pi - \theta 1$  capacitor discharge (level 1) IX.  $\pi - \theta 1 < \omega t < 2\pi$ capacitor charge

By comparing modes II and III, it can be observed that capacitor is discharged when the output voltage (and hence output current) is smaller and charged with a larger current. In this way, there is a higher chance of balancing the capacitor voltage successfully as opposed to the 2:1 case.

### V. SDM APPLIED TO THE MULITLEVEL H-BRIDGE INVERTER

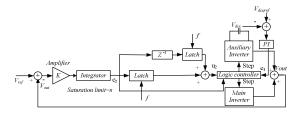

Instead of conventional stair-case modulation, SDM is proposed to push the undesired harmonic components of the output voltage to higher frequencies, as depicted in Fig. 11.  $V_{ref}$  is the reference signal, which is sinusoidal.

Figure 11. Proposed sigma-delta modulation applied to the multilevel inverter

TABLE I. CONTROL LOGIC OF LOGIC CONTROLLER

| u2       | e2 | el | Discrete step |

|----------|----|----|---------------|

| Level 0  | 1  | X  | Level 1       |

| Level 0  | -1 | X  | Level -1      |

| Level 1  | 1  | 1  | Level 3       |

| Level 1  | 1  | -1 | Level 1       |

| Level 1  | -1 | X  | Level 0       |

| Level 3  | 1  | 1  | Level 3       |

| Level 3  | 1  | -1 | Level 4       |

| Level 3  | -1 | 1  | Level 3       |

| Level 3  | -1 | -1 | Level 1       |

| Level 4  | 1  | X  | Level 5       |

| Level 4  | -1 | X  | Level 3       |

| Level 5  | -1 | X  | Level 4       |

| Level -1 | 1  | X  | Level 0       |

| Level -1 | -1 | 1  | Level -3      |

| Level -1 | -1 | -1 | Level -1      |

| Level -3 | 1  | 1  | Level -3      |

| Level -3 | 1  | -1 | Level -1      |

| Level -3 | -1 | 1  | Level -3      |

| Level -3 | -1 | -1 | Level -4      |

| Level -4 | 1  | X  | Level -3      |

| Level -4 | -1 | X  | Level -5      |

| Level -5 | 1  | X  | Level -4      |

The output voltage of the inverter  $V_{out}$  is compared with the reference signal  $V_{ref}$  and the resulting error is fed in to an integrator. The output of this block is named  $e_2$  which is one of the control signals of the logic controller. The other is the integration of the error signal between the desired sinusoidal output and the staircase output  $e_2$ . These two error signals are then quantized into one of the two possible levels 1 or -1 depending on its polarity. Then a simple logic circuit decides on which switch has to be turned ON, which can be seen in Table I where  $u_2$  is the previous status of the output voltage stage and discrete step is the next stage of the output voltage.

The output of the logic controller block step has 9 levels which are  $0, \pm 1, \pm 3, \pm 4, \pm 5$ . Accordingly, the output of the inverter is  $0, \pm V_{dcx}, \pm (V_{dc}-V_{dcx}), V_{dcx}, \pm V_{dc}, \pm (V_{dc}+V_{dcx})$ .

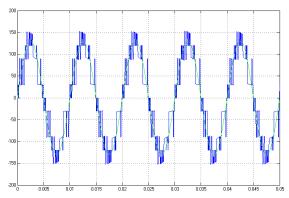

Figure 12. Output voltage waveform of the H-bridge multilevel inverter and its reference

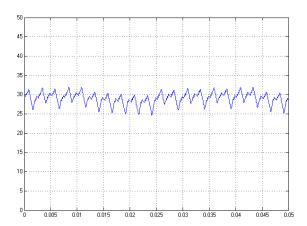

Figure 13. Regulation voltage across the capacitor in the auxiliary cell

Figure 14. The spectrum of the output voltage

Fig. 12 depicts the output voltage waveform of the inverter. As it can be observed, SDM modulation is successful in tracking the sinusoidal reference signal. Fig. 13 shows the capacitor voltage in the auxiliary H-bridge cell where the amplitude of  $V_{ref}$  is 131V; the fundamental frequency is 100 Hz, the gain of the controller (K) is 10, the saturation limits of the integrator are  $\pm 0.005$ , the sampler frequency is 10 kHz, and the threshold of the hysteresis loop is 0.0001, the value of the capacitor is 0.001F and the load is a resistive load which is  $10\Omega$ . It is obvious that capacitor voltage is well regulated. Selection of a larger capacitor would result in lower voltage ripple.

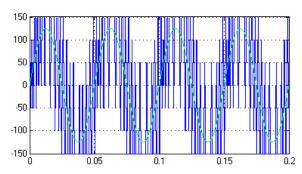

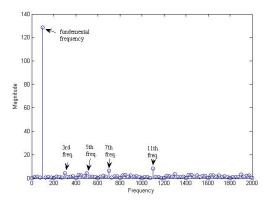

### VI. SPECTRUM ANALYSIS

Normally, the sigma-delta modulation has a problem in which output signal frequency spectrum is worse than the PWM frequency spectrum. So one need to improve this spectral behavior by using different types of high order modulators such as interpolative modulators [14], cascaded modulators [15-17] and adaptive modulators [18-20]. However, in unbalanced voltage level Sigma-Delta modulator, the spectral behavior is good with the THD equal to 0.87% which can be shown in Fig.14.

### VII. CONCLUSION

A cascaded H-bridge multilevel inverter, which requires only one dc source, driving a three phase motor has been analyzed in this paper. The inverter is proposed to have voltage ratio of 4:1, which leads to nine output voltage levels. In order to provide sinusoidal tracking characteristics, sigma-delta modulation technique is employed. Simulation results show that capacitor voltage regulation for the replacing capacitors is possible.

#### REFERENCES

- G. Joos, X. Huang, and O. Boonteck, "Direct-coupled multilevel cascaded series VAR compensators," *IEEE Trans. Industry Applications*, vol. 34, pp. 1156-1163, Sept./Oct. 1998.

- [2] L. M. Tolbert and F. Z. Peng, "Multilevel converters for large electric drives," *IEEE Trans. Industry Applications*, vol. 34, pp. 36-44, 1999.

- [3] M. D. Manjrekar and T. A. Lipo, "A hybrid multilevel inverter topology for drive applications," in *Proc. IEEE Applied Power Electronics Conference*, vol. 2, Feb. 1998, pp. 523-529.

- [4] K. A. Corzine, M. W. Wielebski, and F. Z. Peng, "Control of cascaded multilevel inverters," *IEEE Trans. Power Electronics*, vol. 19, pp. 732-738, May 2004.

- [5] M. Veenstra and A. Rufer, "Control of a hybrid asymmetric multilevel inverter for competitive medium-voltage industrial drives," *IEEE Trans. Industry Applications*, vol. 41, pp. 665-664, Mar./Apr. 2005.

- [6] K. A. Corzine, F. A. Hardrick, and Y. L. Familiant, "A cascaded multi-level H-bridge inverter utilizing capacitor voltages sources," in *Proc. IASTAD power electronics technology and applications Conference*, Feb. 2003.

- [7] Z. Du, L. M. Tolbert, and J. Chiasson, "A cascade multilevel inverter using a single DC source," in *Proc. IEEE Applied Power Electronics Conference and Exposition*, Mar. 2006, pp. 19-23.

- [8] J. Liao, K. Wan, and M. Ferdowsi, "Cascaded H-bridge multilevel inverters - a reexamination," in *Proc. IEEE Vehicle Power and Propulsion Conference*, Sep. 2007.

- [9] D. M. Divan, "The resonant DC link converter- a new concept in static power conversion," *IEEE Trans. Industry Applications*, vol. IA-25, pp. 317-325, 1989.

- [10] G. Luckjiff, I. Dobson, and D. Divan, "Interpolative sigma-delta modulators for high frequency power electronics applications", in *Proc. IEEE Power Electronics Specialists Conference*,1995, pp. 444-449.

- [11] L. Tolbert, K. McKenzie, and J. Chiasson, "Elimination of harmonics in a multilevel converter with non equal DC sources," *IEEE Trans. Industry Applications*, vol. 41, pp. 75-82, 2005.

- [12] P. N. Enjeti, P. D. Ziogas, and J. F. Lindsay, "Programmed PWM techniques to eliminate harmonics: A critical evaluation," *IEEE Trans. Industry Applications*, vol. 26, pp. 302-316, Mar. 1990.

- [13] J. Chiasson, L. M. Tolbert, K. McKenzie, and Z. Du, "Harmonic elimination in multilevel converters," in *Proc. 7th IASTED Int. Multi-Conf. Power and Energy Systems (PES)*, Palm Springs, CA, Feb. 2003, pp. 284–289.

- [14] P. K. Sood and T. A. Lipo, "Power conversion distribution system using a resonant high frequency AC link," *IEEE Trans. Industry Applications*, vol. IA-25, pp. 288-300, 1988.

- [15] W. Chou, P. W. Wong, and R. M. Gray, "Multistage sigma-delta modulation", *IEEE Trans. Information Theory*, vol. 35 no. 4, Jul. 1989, pp. 784-796.

- [16] C. K. Thanh, S. H. Lewis, and P. J. Hurst, "A second order double-sampled delta-sigma modulator using individual-level averaging", *IEEE Journal of Solid-State Circuits*, vol. 32, no. 8, Aug. 1997, pp. 1269-1273.

- [17] L. A. Williams and B. A. Wooley, "A third-order Sigma-Delta modulator with extended dynamic range", *IEEE Journal of Solid-State Circuits*, vol. 29, pp.193-202, March 1994.

- [18] J. Yu, M. B. Sandler, and R. E. Hawken, "Adaptive quantisation for one-bit sigma-delta modulation", *IEE Proceedings G Circuits*, *Devices and Systems*, vol. 139, no 1, Feb. 1992, pp. 39-44.

- [19] C. M. Zierzhoef, "Adaptive sigma-delta modulation with one-bit quantization", IEEE Trans. Circuits and Systems II: analog and digital signal processing, May 2000.

- [20] C. S. Díaz, I.E. Fernando, and C.D Gerardo, "Adaptive Sigma-Delta modulator applied to control a five level multilevel inverter", in *Proc. the Fifth IEEE International Caracas* Conference on Devices, Circuits and Systems, Nov. 2004.