### Missouri University of Science and Technology Scholars' Mine

**Electrical and Computer Engineering Faculty** Research & Creative Works

**Electrical and Computer Engineering**

01 Jul 2007

### A New Battery/Ultracapacitor Energy Storage System Design and its Motor Drive Integration for Hybrid Electric Vehicles

Shuai Lu

Keith Corzine Missouri University of Science and Technology, corzinek@mst.edu

Mehdi Ferdowsi Missouri University of Science and Technology, ferdowsi@mst.edu

Follow this and additional works at: https://scholarsmine.mst.edu/ele\_comeng\_facwork

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

S. Lu et al., "A New Battery/Ultracapacitor Energy Storage System Design and its Motor Drive Integration for Hybrid Electric Vehicles," IEEE Transactions on Vehicular Technology, vol. 56, no. 4, pp. 1516-1523, Institute of Electrical and Electronics Engineers (IEEE), Jul 2007.

The definitive version is available at https://doi.org/10.1109/TVT.2007.896971

This Article - Journal is brought to you for free and open access by Scholars' Mine. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Research & Creative Works by an authorized administrator of Scholars' Mine. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# A New Battery/Ultracapacitor Energy Storage System Design and Its Motor Drive Integration for Hybrid Electric Vehicles

Shuai Lu, Student Member, IEEE, Keith A. Corzine, Senior Member, IEEE, and Mehdi Ferdowsi, Member, IEEE

Abstract—This paper proposes a new energy storage system (ESS) design, including both batteries and ultracapacitors (UCs) in hybrid electric vehicle (HEV) and electric vehicle applications. The conventional designs require a dc-dc converter to interface the UC unit. Herein, the UC can be directly switched across the motor drive dc link during the peak power demands. The resulting wide voltage variation due to UC power transfer is addressed by the simple modulator that is introduced in this paper, so that the motor drive performance is not disrupted. Based on this new methodology, this paper further introduces two ESS schemes with different topologies, namely 1) UC rating and 2) energy flow control. They are applicable to both lightly and heavily hybridized HEVs. Both schemes have the benefits of high efficiency (without a dc-dc link) and low cost. The simulation and experimental results validate the new methodology.

*Index Terms*—Energy storage, hybrid vehicle, power management, regenerative braking, ultracapacitor (UC).

#### I. INTRODUCTION

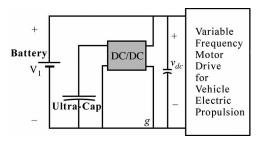

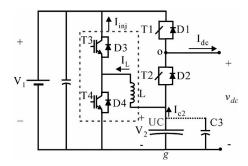

NERGY storage systems (ESSs), which include both Batteries and ultracapacitors (UCs), have been widely studied in hybrid electric vehicle (HEV) and electric vehicle (EV) applications [1]–[12], [17], [18]. Employing UCs relieves the high-energy-density battery unit from the peak power transfer stress due to their higher specific power and efficiency [13]–[18]. This extends the battery life span and greatly reduces the required battery size. As depicted in Fig. 1, conventional method of interfacing the UC unit is to use a bidirectional dc–dc converter to control the power flow in/out of the UC. Therefore, despite the wide variations of the UC terminal voltage, the voltage across the motor drive dc link remains constant. The dc-dc interfacing converter introduces considerable switching and conduction power losses. It also poses stability issues, particularly at high inrush currents [4], [5]. Moreover, it adds cost and weight to the system, particularly with its large inductor rated for the peak power transfer. In this paper, a new approach is introduced to directly interface the UC unit with the motor drive dc link. As shown in Fig. 2(a) (scheme I), no intermediate

Manuscript received March 31, 2006; revised July 31, 2006 and August 26, 2006. This paper was presented at the 2006 IEEE Industry Applications Society Conference, Tampa, FL, October 8–12. The review of this paper was coordinated by Dr. B. Fahimi.

The authors are with the Department of Electrical Engineering, University of Missouri-Rolla, Rolla, MO 65409-0040 USA (e-mail: SL4xf@umr.edu; Keith@Corzine.net; ferdowsi@umr.edu).

Digital Object Identifier 10.1109/TVT.2007.896971

Fig. 1. Conventional ESS topology.

link is needed, and therefore, no extra losses are introduced. The UC is utilized only during the peak power surges such as braking and acceleration. The resulting wide variation of dc-link  $v_{\rm dc}$  is handily resolved by the inverter modulation method that is introduced herein, so that the normal motor drive output is not disrupted.

The ESS design needs to take the high UC cost into consideration. The ESS topology and the corresponding energy flow control need to make the most out of the added UC cost. This paper provides an insightful illustration of the relationship between the motor drive speed and UC state of charge (SOC). Then the principle for UC sizing is specified, and the optimal UC sizing is defined for scheme I. With its modest UC size, it is a basic and economic solution to the efficiency improvement of regenerative braking (particularly effective in urban driving cycles, where braking and acceleration are quite frequent). Scheme I is particularly preferable in lightly hybridized HEVs.

For heavily hybridized HEVs or pure EVs, where a large ESS is required, an alternative scheme (ESS scheme II) is proposed. With some added hardware and UC sizing, it inherits the good features of scheme I, such as high efficiency via direct UC interface; it also satisfies the regular HEV/EV peak power demand with only UC sources; therefore, the internal combustion engine (ICE) and batteries can sustain only the baseline power demand. In a heavily hybridized HEV, the ICE is small, and the electric propulsion subsystem power share is considerable. Therefore, the complete coverage for peak power demands by the UC leads to a major reduction in the battery size, which justifies the increased UC sizing and cost.

For HEVs with an electric motor ranging from 10 to 100 kW, different variable-frequency drive (VFD) controls can be used. The volts per hertz (V/F) control is easy to implement, whereas the vector control approaches (rotor flux oriented indirect, stator flux oriented, direct torque control (DTC), etc.) offer better dynamic performance and easier torque sharing with the

Fig. 2. Proposed high-efficiency and low-cost ESS topology (scheme I).

ICE subsystem. The proposed ESS systems are verified with the integrated VFD control, where the vector control is used in detailed simulations and V/F control is used in the experimental verification.

Section II introduces the new ESS topology (scheme I), new modulation method, and its operation ranges. Design considerations and power management strategy are illustrated in Section III. Section IV presents the second proposed ESS topology (scheme II) and describes its operating modes. Simulation and experimental results are presented in Sections V and VI, respectively. Section VII draws conclusions and presents an overall evaluation of the new proposed ESS.

#### II. UC/BATTERY ESS SCHEME I

#### A. New ESS Topology

The first efficiency-improving scheme features a simple and cost-effective topology. Either the battery or UC source is connected across the motor drive dc link via the complimentary switch pair (T1 and T2), as indicated within the dotted rectangle in Fig. 2(a). An electrolytic capacitor C1 is connected in parallel with the battery as the source for the motor drive dc-link current pulsewidth-modulation (PWM) pulses. The electrolytic capacitor C3 can be connected in parallel with the UC depending on its internal resistance. The lower limit of the UC voltage  $V_2$ is set at 1/3 of its upper limit (battery voltage  $V_1$ ); therefore, the discharge depth is 8/9 of its full capacity. When T1 is on and T2 off, the point "o" is clamped to  $V_1$ , and D2 is reverse biased; the UC is then isolated, and the battery becomes the only source for the motor drive. When T2 is on and T1 off, the dc source is swapped to the UC, and D1 is reversed biased, leaving the battery bank isolated from charging/discharging current  $I_{dc}$ . When the peak power surge occurs during braking and acceleration, the UC source can be swapped in for higher efficiency until the peak power cycle ends or the UC SOC reaches its upper/lower limits.

Fig. 2(b)–(d) shows the possible T1/T2 switch pair implementations. Utilizing power semiconductor switches [Fig. 2(b)] introduces an extra conduction loss over T1/D1 in steady state. Since the switch pair requires no fast turn-on and turn-off characteristics, electromechanical switches can be used as in Fig. 2(c). The conduction loss is thus eliminated; however, the response time is longer (a few milliseconds). Precautions might be taken to protect the UC from possible shoot-through damage, although the UC can sustain thousands of amperes short-circuit current. When insulated gate bipolar transistor (IGBT) is used

in T2 [Fig. 2(d)], the shoot-through fault can be terminated within a few milliseconds.

This proposed ESS topology has a fault tolerance feature in that the UC is protected against overcharging when the controller malfunctions because of the discharge path via the antiparallel diodes D1 and D2, which keeps  $V_2$  below the battery voltage  $V_1$ . Also, during deadtime when T1 and T2 are both off,  $I_{\rm dc}$  still has the path via either D1–C1 (negative  $I_{\rm dc}$ ) or D2–UC (positive  $I_{\rm dc}$ ); thus, no high-voltage spike is induced.

#### B. New Modulation Method

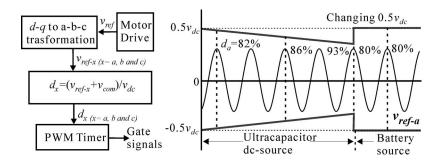

The simplified ESS topology entails extra complexity in VFD modulator. During HEV peak power demand, the direct UC connection across the dc link implies a changing  $v_{\rm dc}$  due to the energy transfer from/to the UC. A straightforward modulation method is proposed herein to guarantee that the motor drive voltage reference  $v_{\rm ref}$  can always be accurately synthesized (i.e., the normal fundamental voltage output is not disrupted by wide  $v_{\rm dc}$  variations). When the VFD energy source is swapped from the battery to the UC,  $v_{\rm dc}$  steps from the constant  $V_1$  to the changing  $V_2$ . For the correct duty-ratio computation, the modulator needs to update  $v_{\rm dc}$  every PWM cycle, and the voltage reference  $v_{\rm ref}$  has to use the real value instead of the modulation index (m-index).

Figs. 3 and 4 illustrate the proposed modulation method in natural sampling and space vector perspectives. Fig. 3 shows the normalization process and equations to compute the duty ratio for each phase. The voltage reference vector is to be transformed into each phase, and certain common-mode reference is to be added, such as the third harmonic addition for the 15% magnitude boost of the output voltage. It is instructive to note that the same voltage reference point returns different duty ratios as  $v_{\rm dc}$  changes.

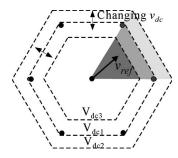

Fig. 4 illustrates that the size of the voltage vectors' hexagonal pattern is proportional to the varying  $v_{\rm dc}$ . To synthesize the given  $v_{\rm ref}$ , the duty ratios of the two enclosing active vectors (in red) are to be changed proportionally with  $v_{\rm dc}$ .

#### C. Operational Limitations

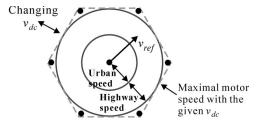

Certain limitation exists for the UC voltage variation in normal VFD operation. As depicted in Fig. 5, the typical VFD voltage and its synchronous frequency are roughly proportional except for the motor resistive voltage drop. Based on this, Fig. 6 shows the two red rings of different inverter voltage magnitudes

Fig. 3. New modulator and its time domain per-phase illustration.

Fig. 4. New modulator space vector illustration.

Fig. 5. Typical motor drive voltage versus speed.

Fig. 6. VFD speed range in vector space.

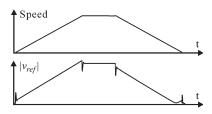

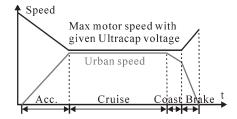

that can also represent the motor full-speed and half-speed operations. Transformed with HEV mechanical reduction gear ratio, they correspond to the boundaries of the vehicle highway and urban speeds, respectively. In Fig. 6, the radius of the inscribing circle of the hexagon represents the maximal reference voltage magnitude ( $|v_{\rm ref}| < (2/\sqrt{3}) \cdot (1/2)v_{\rm dc}$ ) and the maximal VFD motor speed; it varies with the changing dc-link voltage. In time domain (Fig. 7), this maximal speed can be plotted in typical driving cycles. Herein, vehicle acceleration with the UC source decreases  $V_2$  ( $v_{\rm dc}$ ) and the maximal speed (in blue), whereas the braking increases both. As long as the motor speed is below its maximal limits, the VFD can sustain braking and acceleration with the UC source alone. Otherwise, the energy source is switched to the battery.

Fig. 7. UC source operating range in urban driving.

Fig. 8. Scheme I topology with small-current-rating UC charging circuitry option.

This limitation of the UC voltage variation poses no concern to scheme I since the dominant occurrence of the braking and acceleration are in urban driving [9], [10]. As the motor speed is lower than half or 1/3 of the rated value, the UC can be discharged down to half or 1/3 of  $v_{\rm dc}$ , i.e., 3/4 or 8/9 of the UC energy storage can be utilized.

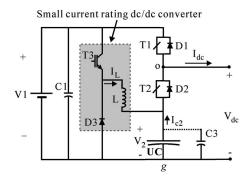

#### D. Add-On Charging Circuitry and Practical Considerations

As losses exist in all subsystems of a vehicle's propulsion system, the regenerated energy in one cycle is not sufficient for the subsequent acceleration (to the same speed). Therefore, a small dc–dc converter can be added, as shown in Fig. 8, to charge the UC. The SOC is maintained by the overall vehicle energy control. By adjusting the duty ratio of T3, the UC charging current can be controlled at much smaller value than the current at peak power demand; thus, the required dc–dc converter requires much smaller switches and inductor.

One thing to note is that the motor drive inverter cannot have a snubber capacitor directly across its dc link with this ESS topology since the step change of the dc-link voltage will induce large current surge through the snubber capacitor and trigger the swap switch driver fault. However, the

resistance-capacitance snubber across each switch can be used if necessary.

Another practical consideration is that, in previous practice of using UC with dc-dc converter, the UC bank voltage rating was usually low, whereas the proposed ESS has high UC nominal voltage equal to the motor drive dc-link voltage (usually between 200 and 500 V). This entails large quantities of UC cells in series connection, which could result in imbalanced charging among cells and poses a reliability issue as the lifetime of UC bank/module is mostly determined by the individual cell voltage and temperature [14]. However, this is no longer an obstacle with the maturing technology of the UC module or standard building blocks [14]–[16]. The charge-balancing circuits between cells greatly improve the performance, reliability, and lifetime of UC modules, and high-voltage-rating UC modules are becoming a mature product line [14]–[16].

### III. HEV ESS DESIGN CONSIDERATIONS AND POWER FLOW CONTROL METHODOLOGY

In this paper, three major ESS design objectives are specified: 1) improving ESS efficiency; 2) reducing UC cost; and 3) decreasing battery sizing while maintaining the peak power performance of the HEV electric propulsion. With the dcsource swapping methodology, the first objective is realized. The second objective is vital for the commercially viable HEV since the UCs are still a costly solution for the energy storage applications. The cost-oriented design principle is that the energy transfer with the largest UC voltage variation should supply only one typical peak power cycle, hereby minimizing UC sizing. This is because braking is usually followed shortly by acceleration. Thus, the regenerated braking energy (less than acceleration energy needed due to the loss) that is stored in the UC will be used up in subsequent acceleration and leave enough room for the next braking. For scheme I, the UC rating is to supply the energy (20–30 W · h) of a full acceleration cycle up to the urban speed (55-65 km/h) with 75% of its capacity (UC voltage varies between half and full). HEV energy flow control is straightforward in scheme I. Detailed estimation shows that it keeps the UC bulk order cost and weight well under U.S. \$800 and 10 kg for a sedan-size HEV; at the same time, it eliminates the need for a bulky dc-dc converter with peak current rating. Thus, it is a very practical option for the future HEV or EV ESS.

This modest UC sizing greatly improves the ESS efficiency in urban driving (frequent braking occurrence), but it will not supply power surges with longer duration, such as the acceleration to freeway speed. The small UC will be exhausted before reaching half speed; the battery needs to provide the high power for the remainder of the cycle, and the battery size must be large. In cases when the third objective is mandatory in HEV design (i.e., to maintain the peak power while reducing the battery size and overall ESS weight), the UC size has to be increased. Assuming that HEV distributes power proportionally between ICE and the electric powertrain, approximately four times the size of the UC in scheme I is needed (four times the kinetic energy at about twice the urban speed). This way, the

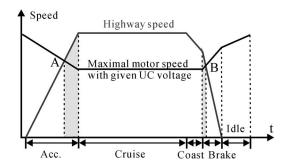

Fig. 9. UC operating range in highway driving cycle.

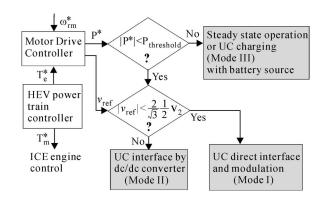

Fig. 10. Energy flow control block diagram.

Fig. 11. Scheme II topology: complete solution.

reduce-sized battery only supplies the baseline power, except for unusual cases like extended time of hill climbing.

For the complete solution to all three design objectives, not only the UC size has to be increased; the topology in scheme I and the energy flow control also need to be modified to handle a full highway driving cycle, as sketched in Fig. 9. Note that the power demands below points A and B still come from the UC source directly. Beyond these limits, the UC voltage is too low to maintain the motor speed, which is further increasing. During these periods (indicated by the shaded areas), a bidirectional dc-dc converter is needed to control the surge power from the UC. The dc link swaps to the battery during the constant-speed cruise. Subsequently, UC is swapped in to absorb regenerative braking energy and then charged with the controlled small current during idle time. The flowchart of this new energy management scheme (scheme II) is illustrated in Fig. 10. Circuit implementation of this new ESS topology is shown in Fig. 11 and discussed in the next section.

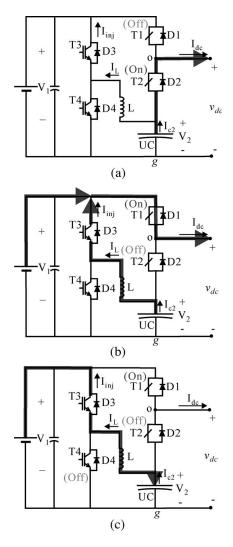

Fig. 12. Operation modes of the ESS scheme II. (a) Mode I: High efficiency. (b) Mode II: Combined sources. (c) Mode III: UC charging.

## IV. FULL-PERFORMANCE ESS TOPOLOGY AND ITS OPERATION MODES

The new ESS topology (in Fig. 11) has three operation modes for peak power demands. For braking and acceleration in the urban speed range, Mode I is used [see Fig. 12(a)]. Therein, the dc-dc converter (in red dotted lines) and the battery are bypassed, and the UC becomes the direct power source of the motor drive using the modulation method in scheme I. When the acceleration and braking occur between highway speed and urban speed, Mode II is used [see Fig. 12(b)]. The majority of the VFD power demands are transferred from/to the UC by controlling the magnitude of the inductor current (within the dc-dc converter). The rest are from the battery source. The UC power contribution can be viewed as a current source injection into the VFD dc link, and it is expressed as  $P_{\rm uc} =$  $V_1 \cdot (i_L \cdot D_3) = V_2 \cdot i_L$ , where D3 is the duty ratio of T3. Note that in Fig. 12(b), the power flow that is indicated by red arrows is reversed for negative direction during regenerative braking at high speed. The purpose of Mode III [see Fig. 12(c)] is to charge the UC by battery, particularly during the idle period between braking and subsequent acceleration cycle. SOC of the UC is maintained by the system-level intelligent control. In this mode, T3 switches at PWM frequency, and T4 remains off. While T3 is on, inductor current  $I_L$  increases. Whereas turning T3 off forces D4 to conduct and decrease  $I_L$ .

Generally, Mode I is the most frequent operating mode, whereas Mode II is to maintain the vehicle power performance during less frequent highway speed braking/acceleration. It is instructive to discuss the transitions between Mode I and Mode II. As in Fig. 9, acceleration to the highway speed starts with Mode I. When the UC voltage  $V_2$  becomes too low to maintain the VFD motor speed (corresponding reference voltage), T2 is turned off, and T1 is turned on. Then switches T4 and T3 switch with a certain PWM duty ratio according to current injection command. After a few PWM cycles,  $I_L$ reaches the steady state. The current injection into the dc link is in PWM pulses and so is  $I_{\rm dc}$ . The capacitor provides the source for these high-frequency current pulses and stabilizes  $v_{\rm dc}$ . When braking from highway speed, the control starts in Mode II, where the inductor current (negative direction) is controlled to direct all the braking energy to the UC. As  $V_2$  increases and the motor speed decreases beyond point B (Fig. 9), the UC voltage becomes large enough to produce the VFD reference voltage for the decreasing motor speed. Then Mode II is switched to the high-efficiency Mode I. The inductor current takes the path through D4 to dump the residue energy into the UC.

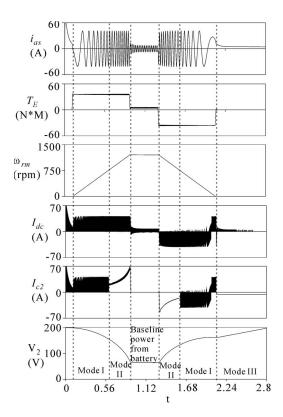

#### V. SIMULATION STUDY

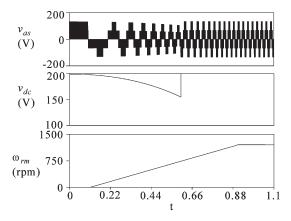

The integrated control of the VFD drive and ESS were simulated with a detailed system model. The VFD drive uses DTC with space vector modulation (DTC-SVM), but any other types of vector controls could be used. The modulation method introduced earlier in this paper was applied to replace the conventional SVM. The torque command to the VFD is assumed to be constant during the acceleration and braking. Fig. 13 shows the simulation results for a complete cycle of acceleration and braking (highway speed using ESS scheme II). The six traces are the motor phase current, toque output, motor speed, VFD dc-link current, UC discharging current, and UC terminal voltage, respectively. The operation modes and their transitions are labeled in the figure. Note that when Mode I is used, the UC charging and discharging current  $I_{c2}$  is in PWM pulse form, whereas in Mode II, the  $I_{c2}$  is the inductor current, which is commanded to follow the peak power transfer requirement.

Fig. 14 illustrates the direct UC interface operation (scheme I). With the proposed modulation method, the commanded fundamental of  $v_{\rm as}$  remains unaffected by the changing  $v_{\rm dc}$ , although the envelope of the  $v_{\rm as}$  changes with dc-link  $v_{\rm dc}$ .

#### VI. EXPERIMENTAL RESULTS ANALYSIS

A 3.7-kW induction motor is used to emulate the HEV motor. Parallel arrays of four 3900-µF electrolytic capacitors are used to emulate the UC to observe wide voltage variation during braking and accelerating. The prototype uses the topology in Fig. 2, and dual-pack IGBTs are used as the dc-source swap switch. A Microchip dsPIC30F4012 microcontroller is used for

Fig. 13. Simulation results of scheme II.

Fig. 14. Simulation results of scheme I.

the motor drive and ESS control. The V/F control is used in laboratory validation. The PWM sample frequency is 5 kHz.

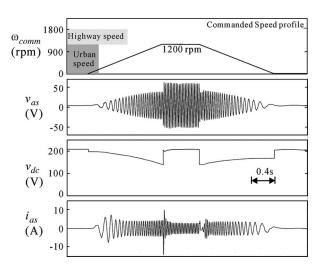

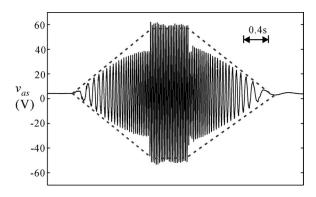

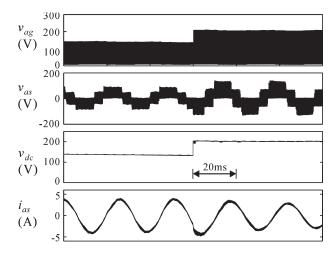

Fig. 15 shows the motor drive performance with the proposed dc-source swapping. Trace 1 is the commanded speed profile emulating an urban driving cycle. Traces 2, 3, and 4 are the filtered version of the motor drive a-phase voltage output, dc-link voltage, and a-phase current, respectively. The UC is switched across the dc link during acceleration and braking;  $v_{\rm dc}$  then has a wide voltage variation and a large step change as the dc link swaps between battery and UC. In this test, conventional SVM modulation is used. Therefore,  $v_{\rm as}$  magnitude cannot ramp up together with the frequency as commanded. Fig. 16 shows the zoom-in view of the deformed  $v_{\rm as}$ , where the dotted line represents the commanded  $|v_{\rm as}|$ . Obviously, the deformed  $v_{\rm as}$  is shaped by the outline of  $v_{\rm dc}$  waveform.

Fig. 15. Laboratory results of a start-steady-stop cycle (without new modulation method).

Fig. 16. Motor phase voltage output deformation.

Fig. 17. Laboratory results of a start-steady-stop cycle (with new modulation method).

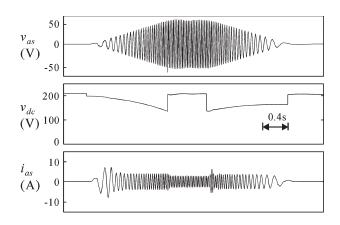

Fig. 17 shows the same set of laboratory results when the new modulation method is used with same motor speed profile. Obviously, wide  $v_{\rm dc}$  change is now transparent to the motor as its output phase voltage (fast average or filtered value) follows the ramp correctly. Hence,  $v_{\rm dc}$  change will not disrupt the motor drive performance.

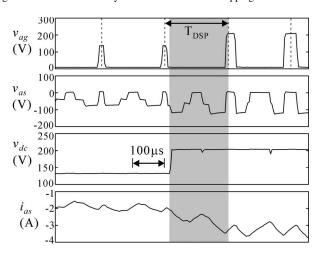

It is instructive to take a detailed look at the proximity of the point of source swapping from the UC to the battery. In Fig. 18, the traces are a-phase to ground voltage, a-phase to

Fig. 18. Detailed laboratory data of the dc-source swapping.

Fig. 19. DC-source swap transition analysis.

neutral voltage, dc-link voltage, and a-phase current, respectively. Although  $v_{\rm ag}$  and  $v_{\rm as}$  have the obvious step change in their PWM waveform outline, their fast average value remains unchanged before and after the source swap point.

Also note that there is a slight discrete change in the current waveform. This is due to the discrete property of digital control. It is illustrated in Fig. 19, which plots the same set of laboratory data with a smaller timescale. Ideally, the duty ratios of the phase to ground voltages (such as  $v_{\rm ag}$ ) should have a step change simultaneously with  $v_{\rm dc}$ . In the PWM cycle when the source swap occurs, the battery voltage is used to compute the three phase duty cycles. However, this change takes effect in the subsequent cycle. Therefore, as indicated by the highlighted region, the wrong duty ratios are still used after the step change of  $v_{\rm dc}$ . Note that the active PWM portions are on the two edges of each cycle.

Since the IGBT implementation of the swap switch has only a few milliseconds of rising time, a completely smooth and seamless dc-source swapping can be achieved by scheduling the external timer module to start source swapping at the beginning of the next PWM cycle after the duty ratios are computed using the new value of the dc-source voltage. Using electromechanical switch takes longer time (several PWM cycles) to change the dc-link voltage, and the resulting discrete current step might

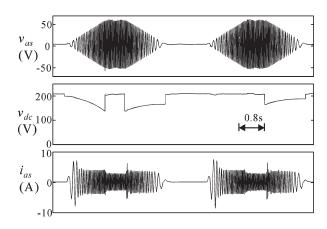

Fig. 20. Multiple regenerative braking test results.

be more significant; however, the short-duration transient will not affect the motor performance much.

Fig. 20 shows a test of ESS energy flow management, where the UC is charged by multiple braking phases before it is used in acceleration. Therein, the traces are the a-phase line to neutral voltage, the dc-link voltage, and a-phase current. The first acceleration lowers the UC voltage. Even with the energy absorbed by the subsequent braking, it is still insufficient to supply the next acceleration. Therefore, the second acceleration uses battery power. Then the second braking builds up the UC voltage to the point such that it can completely supply the next acceleration.

As stated previously, in lightly hybridized vehicles, a small low-power dc-dc converter can be used to charge the UC. This builds up the UC voltage during coasting and idling periods, so that in most cases, the UC has enough stored energy and can be used for each acceleration cycle.

#### VII. CONCLUSION

The major energy-saving scheme employed by HEVs is recycling the regenerative braking energy, particularly in the urban driving cycles, which basically consist of subsequent braking and acceleration. In the conventional battery and UC ESS, the UCs are interfaced by a dc-dc converter. However, it is proposed in this paper that in the urban driving conditions, where the motor speed is usually below its half-rated value, the UC can be directly connected into the dc link of the motor drive as its power source. By employing a slightly more complex inverter modulation, the motor drive output voltage remains intact, although the UC has wide voltage variations. It is also proven that the effective UC voltage variation range can utilize its energy storage capacity to a large extent.

The UC direct connection methodology improves the regenerative energy recycling efficiency considerably. Design principles of HEV ESS are specified in this paper. For realization in lightly hybridized and heavily hybridized HEVs, two ESS schemes are proposed with different topologies, UC rating, and energy flow management. Detailed simulation and experimental results verify the new methodology and the effectiveness of the control set.

#### REFERENCES

- S. Pay and Y. Baghzouz, "Effectiveness of battery-supercapacitor combination in electric vehicles," in *Proc. IEEE Bologna Power Tech Conf.*, Jun. 2003, vol. 3.

- [2] M. Ortuzar, J. Dixon, and J. Moreno, "Design, construction and performance of a buck-boost converter for an ultracapacitor-based auxiliary energy system for electric vehicles," in *Proc. IECON*, Nov. 2003, vol. 3, pp. 2889–2894.

- [3] B. J. Arnet and L. P. Haines, "High power DC-to-DC converter for supercapacitors," in *Proc. IEEE-IEMDC*, Cambridge, MA, Jun. 2001, pp. 985–990.

- [4] W. Lhomme, P. Delarue, P. Barrade, A. Bouscayrol, and A. Rufer, "Design and control of a supercapacitor storage system for traction applications," in *Proc. IAS Conf.*, 2005. CD-ROM.

- [5] K. C. Tseng and T. J. Liang, "Novel high-efficiency step-up converter," Proc. Inst. Electr. Eng.—Electr. Power Appl., vol. 151, no. 2, pp. 182–190, Mar. 2004.

- [6] R. M. Schupbach, J. C. Balda, M. Zolot, and B. Kramer, "Design methodology of a combined battery–ultracapacitor energy storage unit for vehicle power management," in *Proc. Power Electron. Spec. Conf.*, Jun. 15–19, 2003, vol. 1, pp. 88–93.

- [7] E. Ozatay, B. Zile, J. Anstrom, and S. Brennan, "Power distribution control coordinating ultracapacitors and batteries for electric vehicles," in *Proc. Amer. Control Conf.*, Jun. 30–Jul. 2, 2004, vol. 5, pp. 4716–4721.

- [8] J. R. Anstrom, B. Zile, K. Smith, H. Hofmann, and A. Batra, "Simulation and field-testing of hybrid ultra-capacitor/battery energy storage systems for electric and hybrid-electric transit vehicles," in *Proc. Appl. Power Electron. Conf. and Expo.*, Mar. 2005, vol. 1, pp. 491–497.

- [9] M. Amrhein and P. T. Krein, "Dynamic simulation for analysis of hybrid electric vehicle system and subsystem interactions, including power electronics," *IEEE Trans. Veh. Technol.*, vol. 54, no. 3, pp. 825–836, May 2005.

- [10] C. C. Chan, "The state of the art of electric and hybrid vehicles," *Proc. IEEE*, vol. 90, no. 2, pp. 247–275, Feb. 2002.

- [11] M. Ehsani, K. M. Rahman, and H. A. Toliyat, "Propulsion system design of electric and hybrid vehicles," *IEEE Trans. Ind. Electron.*, vol. 44, no. 1, pp. 19–27, Feb. 1997.

- [12] S. Onoda and A. Emadi, "PSIM-based modeling of automotive power systems: Conventional, electric, and hybrid electric vehicles," *IEEE Trans. Veh. Technol.*, vol. 53, no. 2, pp. 390–400, Mar. 2004.

- [13] L. Zubieta and R. Bonert, "Characterization of double-layer capacitors for power electronics applications," *IEEE Trans. Ind. Appl.*, vol. 36, no. 1, pp. 199–205, Jan./Feb. 2000.

- [14] D. Linzen, S. Buller, E. Karden, and R. W. De Doncker, "Analysis and evaluation of charge-balancing circuits on performance, reliability, and lifetime of supercapacitor systems," *IEEE Trans. Ind. Appl.*, vol. 41, no. 5, pp. 1135–1141, Sep. 2005.

- [15] Ultracapacitor Product Brochures and Application Notes. [Online]. Available: http://www.maxwell.com

- [16] Epcos 2005 Datasheet-UltraCap Double Layer Capacitors. [Online]. Available: http://www.epcos.com

- [17] A. Emadi, Handbook of Automotive Power Electronics and Motor Drives. New York: Marcel Dekker, May 2005.

- [18] M. Ehsani, Y. Gao, S. E. Gay, and A. Emadi, Modern Electric, Hybrid Electric, and Fuel Cell Vehicles: Fundamentals, Theory, and Design. Boca Raton, FL: CRC Press, Dec. 2004.

**Shuai Lu** (S'05) received the B.S.E.E. degree in electrical engineering from Chongqing University, Changqing, China, in 1997, the M.S.E.E. degree in electrical engineering from the University of Wisconsin, Milwaukee, in 2003, and the Ph.D. degree in electrical engineering from the University of Missouri, Rolla, in 2007.

He is currently a Senior R&D Engineer at MTS System Corporation, Eden Prairie, MN. He is the holder of two patents pending. His research interests include power electronics and motor drives,

including multilevel converters, multiphase power conversion, electric motor analysis/design/control, and their applications to hybrid (electric) vehicles and renewable energy. His current focus is on ultrahigh power density and high-performance electric drive systems for hybridizing racing cars and ground vehicle testing systems. He has authored or coauthored many technical papers.

He has authored or coauthored seven IEEE TRANSACTIONS papers.

**Keith A. Corzine** (S'92–M'97–SM'06) received the B.S.E.E., M.S.E.E., and Ph.D. degrees from the University of Missouri-Rolla in 1992, 1994, and 1997, respectively.

He taught at the University of Wisconsin-Milwaukee from 1997 to 2004 and is currently an Associate Professor at the University of Missouri-Rolla. His research interests include power electronics, motor drives, naval ship propulsion systems, and electric machinery analysis.

**Mehdi Ferdowsi** (S'01–M'04) received the B.S. degree in electronics from the University of Tehran, Tehran, Iran, in 1996, the M.S. degree in electronics from Sharif University of Technology, Tehran, in 1999, and the Ph.D. degree in electrical engineering from the Illinois Institute of Technology, Chicago, in 2004.

In August 2004, he joined the Department of Electrical and Computer Engineering, University of Missouri-Rolla, where he is currently an Assistant Professor. He is the author of more than 20 papers

published in international journals and conference proceedings. His major research interests include digital control of switched-mode power converters, battery charge equalization, electric and hybrid vehicles, and multilevel converters.

Dr. Ferdowsi was a recipient of the Joseph J. Suozzi INTELEC 2003 Fellowship Award from the IEEE Power Electronics Society.